Преобразователь числа в модулярный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

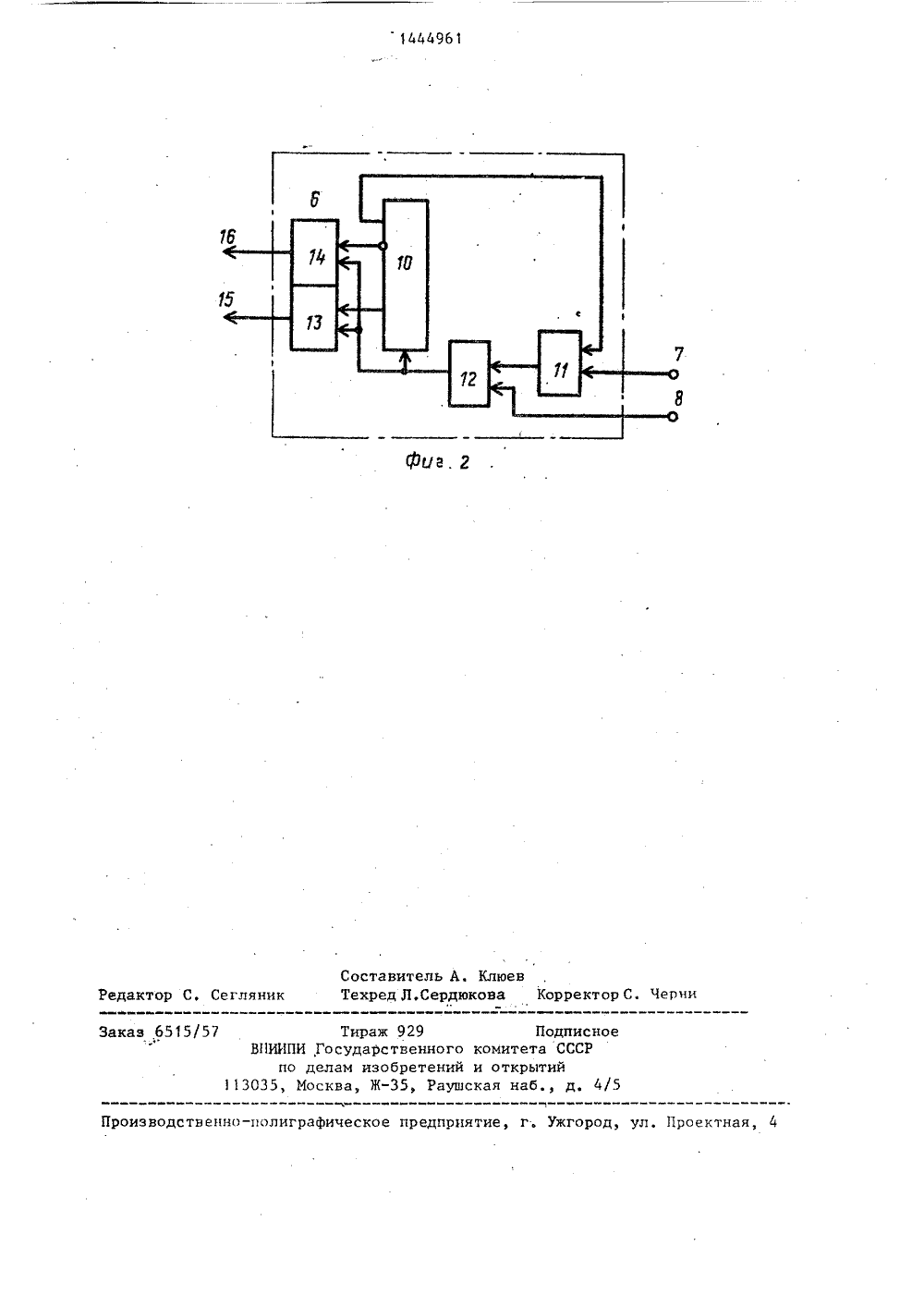

(51) 4 Н 03 И 7/18 ОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) Авторское свидетельство СССР Яф 662932, кл, Н 03 И 7/18, 1976,Авторское свидетельство СССР У 10.12237, кл. Н 03 М 7/18, 1981.Авторское свидетельство СССР В 374596, кл. Н 03 И 7/ 18, 1970. (54) ПРЕОБРАЗОВАТЕЛЬ ЧИСЛА В ИОДУГГРНЫЙ КОД(57) Изобретение относится к области вычислительной техники и может быть использовано для сопряжения устройств ЯО 1444961 А 1 функционирующих в фибоначчиевых кодах, например высокочастотных аналого-цифровых преобразователей, сустройствами, функционирующими в модулярном коде, например, высокопроизводительными процессорами. Цельизобретения - расширение области применения за счет возможности преобразования фибоначчиевого кода в модулярный код, Поставленная. цель достигается тем, что преобразователь числа в модулярный код, содержащий блок"1 элементов И, сумматор 2 по модулю,накапливающий сумматор 3 по модулю,регистр 4 сдвига, блок б синхронизации, содержит регистр 5 сдвига с соответствующими связямн. 2 ил,Изобретение относится к вычислительной технике и может быть использовано для сопряжения устройств,функционирующих в "фибоначчиевом"коде, например, высокоточных аналогоцифровых преобразователей, с устройствами функционирующими в модулярныхкодах, например, высокопроизводительными и высоконадежными процессорами, 10Цель изобретения - расширение области применения за счет возможностипреобразования "фибоначчиевого" кодав модулярный код,На фиг. 1 представлена схема преобразователя числа в модулярный код;на фиг, 2 - схема блока синхронизации.. Преобразователь (фиг. 1) содержитблок 1 элементов И, сумматор 2 по модулю, накапливающий сумматор 3 по модулю, регистры 4 и 5 сдвига, блок 6синхронизации, вход 7 запуска преоб. разователя, тактовый вход 8 преобразователя, вьиод 9 преобразователя.Блок 6 синхронизации (фиг. 2) содержит счетчик 10 по модулю, триггер 11, элементы И 12-14, выходы 15и 16 блока 6 синхронизации, причемвход 7 запуска преобразователя соединен со входом установки в единицу 30триггера 11, выход которого соединен с первым входом элемента И 12,выход которого соединен со счетнымвходом счетчика 10 по модулю и спервыми входами элементов И 13 и 14,вьиоды которых являются соответственно выходами 15 и 16 блока 6 синхронизации, прямой и инверсный выходымладшего разряда и импульсный выходобнуления счетчика 10 по модулю соединен соответственно со вторыми входами элементов И 13 и 14 и со входомустановки в нуль триггера 11, Сумматор2 и накапливающий сумматор 3 являются сумматорами по модулю(45модуль системы остаточных классов),Разрядность регистра 4 сдвига имодуль счетчика 10 равны и (и - разрядность кода Фибоначчи).Регистр 5 сдвига состоит из (р+1)параллельных регистров разрядности1 од р - параметр кода Фибоначчи).,Преобразование кода А Фибоначчи в модулярный код А выполняется согласно следующему уравнению:3; я С(1) (вод )у ) - наименьший неотрицательныйвычет от д-го веса "фибоначчиевого" кода где Фрг; й А ( А и оЕ;еА ЕА(тпос 1)р)10 при хс 1; Р 1 при=1;( (д)+( (1-р;1) при 1 ) 1 а, - двоичная цифра;Ы; - наименьший неотрицательный вычет.Первые р+1 весов "фибоначчиевого" кода всегда равны единице и, следовательно, не превышают величиныЭто позволяет использовать их в качестве исходных условий для получения вычетов /р , , / ь- помощью рекурентного соотношения: р,: , + ; р, (шос 1 ) ) В момент времени, соответствующий началу преобразования по входу 7, поступает импульс, в результате чего, на выходах блока 6 синхронизации начинают поочередно вырабатываться единичные импульсы. Первый импульс поступает на вход записи сумматора 3 и записывает внего произведение а, Р,Второй импульс поступает на вхо" ды сдвига регистров 4 и 5, производит в них сдвиг информации на один разряд влево. При этом в (р+1)-й разряд регистра 5 записывается значение, а на выходе сумматора 2 образуется значение (3 р,э . На выходе блока 1 элементов И образуетса произведение а3 Принцип преобразования для всех модулей системы остаточных классов аналогичен.Преобразователь (фиг. 1) работает следующим образом.В исходном состоянии в регистр 4 записан код преобразуемого числа А в "фибоначчиевом" коде, а в регистр 5 - единицы, накапливающий сумматор 3 по модулю обнулен, состояние блока б синхронизации соответствует исходному. Так как на входы сумматора 2 по модулю поступают единицы, то на ,вход записи (р+1)-го разряда регистра 5 поступает величины 3 , На выходе блока 1 элементов И устанавливается величина а,(а,3, + а )топ р Преобразователь числа в модулярный код, содержащий блок элементовИ, сумматор по модулю, накапливающийсумматор по модулю, первый регистрсдвига и блок синхронизации, причем .вход запуска и тактовый вход преобразователя соединены соответственно совходом запуска и тактовым входом блока синхронизации, первый выход которого соединен с входом разрешениясдвига первого регистра сдвига, выход младшего разряда которого соединен с первым входом блока элементовИ, выход которого соединен с информационным входом накапливающего сумматора по модулю, о т л и ч а ющ и й с я тем, что, с целью расши-.рения области применения путем обес"печения воэможности преобразованияфибоначчиевого кода в модулярный код,он содержит второй регистр сдвига,причем выход младшего разряда второго регистра сдвига соединен с вторымвходом блока элементов И и с входомпервого слагаемого сумматора по модулю, вход второго слагаемого которого соединен с выходом старшего разряда второго регистра сдвига, входстаршего разряда которого соединен свыходом сумматора по модулю, первый и второй выходы блока синхронизациисоединены соответственно с входом разрешения сдвига второго регистрасдвига и с входой разрешения записи накапливающего сумматора по модулю,выход которого является выходом преобразователя. и так далее,Таким образом, в процессе преобразования на выходе (р+1) разряда 10регистра 5 образуются значения 3,3 , на выходе блока 1 элементов И - значения а,3 а 3 , В конце преобразования в накапливающемсумматоре 3 образуется сумма Ю 15являнрцаяся результатом преобразованияБлок 6 синхронизации работает следующим образом. В исходном состояниисчетчик 10 по модулю и триггер 11 обнулены. 20 В момент времени, соответствующий началу преобразования по входу 7 поступает импульс и устанавливает триггер 11 в единичное состояние. В ре зультате этого на счетный вход счетчика 10 по модулю поступают тактовые импульсы. Так как вторые входы элементов 11 и 14 соединены с прямым и инверсным выходами счетчика 10, соот ветствующими его младшему разряду, то иа выход 15 блока поступают импульсы с нечетными номерами, а на выход 16 - с четными, Так как модуль пересчета счетчика 10 равен п, то при поступлении на информационный вход накапливающего сумматора 3 по модулю последнего слагаемого а,3 счетчик 10 обнуляется и на его импульсном выходе обнуления вырабаты вается единичный импульс, который сбрасывает триггер 11 в нулевое сосПосле паступленйя третьего импульса в накапливающем сумматоре 3 образуется значение 4тояние, после чего блок 6 готов к новому циклу работы.Формула н э о б р е т е н и я14449 б 1 2 егляни Подпи комитета СССи открыт кая наб. 4/ изводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 Редактор С. С Заказ 6515/57 Составитель А. КлюевТехред Л,Сердюкова Корректор С. Черни Тираж 929 ВНИИПИ,Государственного по делам изобретений 113035, Москва, Ж, Рауш

СмотретьЗаявка

4235497, 27.04.1987

КРАСНОДАРСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК

КЛЮЧКО ВЛАДИМИР ИГНАТЬЕВИЧ, ТКАЧЕНКО АЛЕКСАНДР ВАСИЛЬЕВИЧ, ФИНЬКО ОЛЕГ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H03M 7/18

Метки: код, модулярный, числа

Опубликовано: 15.12.1988

Код ссылки

<a href="https://patents.su/4-1444961-preobrazovatel-chisla-v-modulyarnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь числа в модулярный код</a>

Предыдущий патент: Преобразователь двоичного кода в код грея

Следующий патент: Преобразователь последовательно-параллельного кода в параллельный

Случайный патент: Способ определения анизотропии разрывной длины бумаги