Преобразователь последовательно-параллельного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

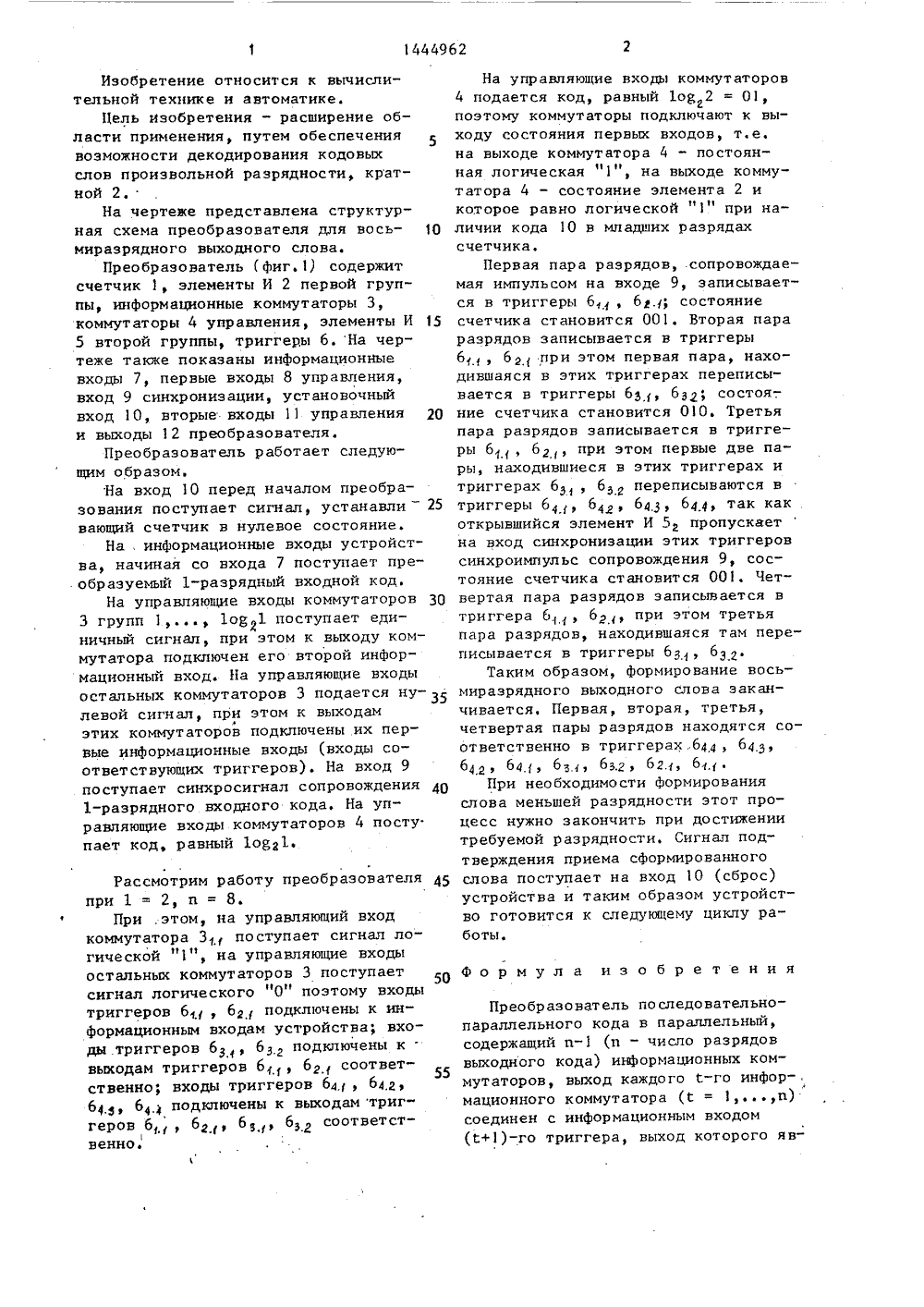

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 11 4 Н 03 И 9/00 НИЯ в, В. П, Карпенченко ьство СССР О, 1982. е вычислив, И.; Энер ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТКРЫТИЙ ОПИСАНИЕ ИЗОБРЕН АВТОРСКОМУ СВИДЕТЕЛЬСТВ(57) Изобретение относится к областивычислительной техники и автоматикиЦель изобретения - расширение области применения преобразователя путемобеспечения возможности преобразования кодовых слов произвольной разрядности, кратной 2, Преобразователь содержит счетчик 1, элементы И 2 первой группы, информационные коммутаторы 3, коммутаторы 4 управления,элементы И 5 второй группы, триггеры 6. 1 ил.Изобретение относится к вычислительной технике и автоматике.Цель изобретения - расширение области применения, путем обеспечения возможности декодирования кодовых слов произвольной разрядности, кратной 2.На чертеже представлена структурная схема преобразователя для вось миразрядного выходного слова.Преобразователь ( Фиг.1) содержит счетчик 1, элементы И 2 первой группы, информационные коммутаторы 3, коммутаторы 4 управления, элементы И 15 5 второй группы, триггеры 6. На чертеже также показаны информационные входы 7, первые входы 8 управления, вход 9 синхронизации, установочный вход 10, вторые входы 11 управления 20 и выходы 12 преобразователя.Преобразователь работает следующим образом.На вход 10 перед началом преобразования поступает сигнал, устанавли 25 вающий счетчик в нулевое состояние.На, информационные входы устройства, начиная со входа 7 поступает преобразуемый 1-разрядный входной код,На управляющие входы коммутаторов 30 3 групп 1 1 од 1 поступает единичный сигнал, при этом к выходу коммутатора подключен его второй информационный вход. На управляющие входы остальных коммутаторов 3 подается ну левой сигнал, при этом к выходам этих коммутаторов подключены их первые информационные входы (входы соответствующих триггеров). На вход 9 поступает синхросигнал сопровождения 1-разрядного входного кода. На управляющие входы коммутаторов 4 посту. пает код, равный 1 ое 21. Рассмотрим работу преобразователяпри 1 = 2, и = 8,При .этом, на управляющий входкоммутатора 34 поступает сигнал логической "1", на управляющие входыостальных коммутаторов 3 поступаетсигнал логического "0" поэтому входытриггеров 64, бгподключены к информационным входам устройства; входы.триггеров бз , 6 подключены к .выходам триггеров 644, бг. соответственно; входы триггеров 64 64,г,64., 64 4 подключены к выходам триг"геров 6 бг 6 , 6 соответственно. На управляющие входы коммутаторов4 подается код, равный 1 о 2 = 01,поэтому коммутаторы подключают к выходу состояния первых входов, т.е.на выходе коммутатора 4 - постоянная логическая "1", на выходе коммутатора 4 - состояние элемента 2 икоторое равно логической "1" при наличии кода 10 в младших разрядахсчетчика,Первая пара разрядов, .сопровождаемая импульсом на входе 9, записывается в триггеры 6,4, бт.; состояниесчетчика становится 001, Вторая параразрядов записывается в триггеры64, бг при этом первая пара, находившаяся в этих триггерах переписывается в триггеры 6 , 6, состоя-,ние счетчика становится 010. Третьяпара разрядов записывается в триггеры 64, бг при этом первые две пары, находившиеся в этих триггерах итриггерах б, бг переписываются втриггеры 64, 64 г, 64 З, 644, так какоткрывшийся элемент И 5 г пропускаетна вход синхронизации этих триггеровсинхроимпульс сопровождения 9, состояние счетчика становится 001, Четвертая пара разрядов записывается втриггера 644, бган, при этом третьяпара разрядов, находившаяся там переписывается в триггеры 64, 6 г.Таким образом, Формирование восьмиразрядного выходного слова заканчивается, Первая, вторая, третья,четвертая пары разрядов находятся со -ответственно в триггерахб 44, 64,64 г, 64,1 бз 4 бзг бг 4 64.сПри необходимости Формированияслова меньшей разрядности этот про"цесс нужно закончить при достижениитребуемой разрядности, Сигнал подтверждения приема сформированногослова поступает на вход 10 (сброс)устройства и таким образом устройство готовится к следующему циклу работы.Формула изобретенияПреобразователь последовательно- параллельного кода в параллельный, содержащий и(и - число разрядов выходного кода) информационных коммутаторов, выход каждого -го инфор-, мационного коммутатора ( = 1и) соединен с информационным входом (г+1)-го триггера, выход которого явЗаказ 6516/58 .Тираж 929 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ляется соответствующим выходом преобразователя, информационный вход первого триггера является первым информационным входом преобразователя,5 о т л и ч а ю щ и й с я тем, что, с целью расширения области применения преобразователя за счет обеспечения возможности преобразования кодовых слов произвольной разрядности, кратной 2, в него введены ш(ш =1 ор) коммутаторов управления, счетчик шэлементов И первой группы и шэлементов И второй группы, инверсный выход каждого разряда счет чика соединен с соответствующими входами одноименного и всех последующих элементов И первой группы, прямой выход каждого разряда счетчика, кроме первого, соединен с соответст вующим входом предыдущего элемента И первой группы, выход 1-го (1 = 1 ш) элемента И первой группы соединен с (1 с - 1+1)-м (1 с = 1 ш, 1; ) 1) информационным входом 1-го коммутатора управления, остальные (2 - 2 ) информационные входы каждого из которых подключены к шине логической единицы, выход каждого коммутатора управления соединен с первым входом последующего элемента И второй группы, выход первого элемента И второй группы соединен с синхровходами первого и второго триггеров, выход р-го (р = 2,ш) элемента И второй группы соединен с синхровходами кажФ дых 2 последующих триггеров, выходы триггеров соединены с первыми входами одноименных информационных коммутаторов каждой из д (11,ш), содержащей 1 Ц = 12" ) информационных коммутаторов, вторые входы информационных коммутаторов являются соответствующими вторыми информационными входами преобразователя, управляющие входы информационных коммутаторов каждой группы объединены и являются соответствующими первыми управляющими входами преобразователя, управляющие входы коммутаторов управления и вход установки счетчика являются соответственно вторыми управляющими входами и установочнымвходом преобразователя, вторые входы элементов И второй группы объединены с синхровходом счетчика и являются входом синхронизации преобразователя.

СмотретьЗаявка

4275961, 03.07.1987

СПЕЦИАЛЬНОЕ ПРОЕКТНО-КОНСТРУКТОРСКОЕ БЮРО "ДИСКРЕТ" ОДЕССКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

ДРОЗД АЛЕКСАНДР ВАЛЕНТИНОВИЧ, ЖЕРДЕВ ЮРИЙ РОБЕРТОВИЧ, КАРПЕНКО ВИКТОР ПЕТРОВИЧ, ЛЕБЕДЬ ВАЛЕРИЙ ВЛАДИМИРОВИЧ, МИНЧЕНКО ВАЛЕНТИНА АНАТОЛЬЕВНА

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательно-параллельного

Опубликовано: 15.12.1988

Код ссылки

<a href="https://patents.su/3-1444962-preobrazovatel-posledovatelno-parallelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательно-параллельного кода в параллельный</a>

Предыдущий патент: Преобразователь числа в модулярный код

Следующий патент: Декодирующее устройство -разрядного кода

Случайный патент: Способ профилактики и лечения атеросклероза в эксперименте