Устройство для сопряжения процессоров в однородной вычислительной структуре

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1392572

Авторы: Важнов, Максименко

Текст

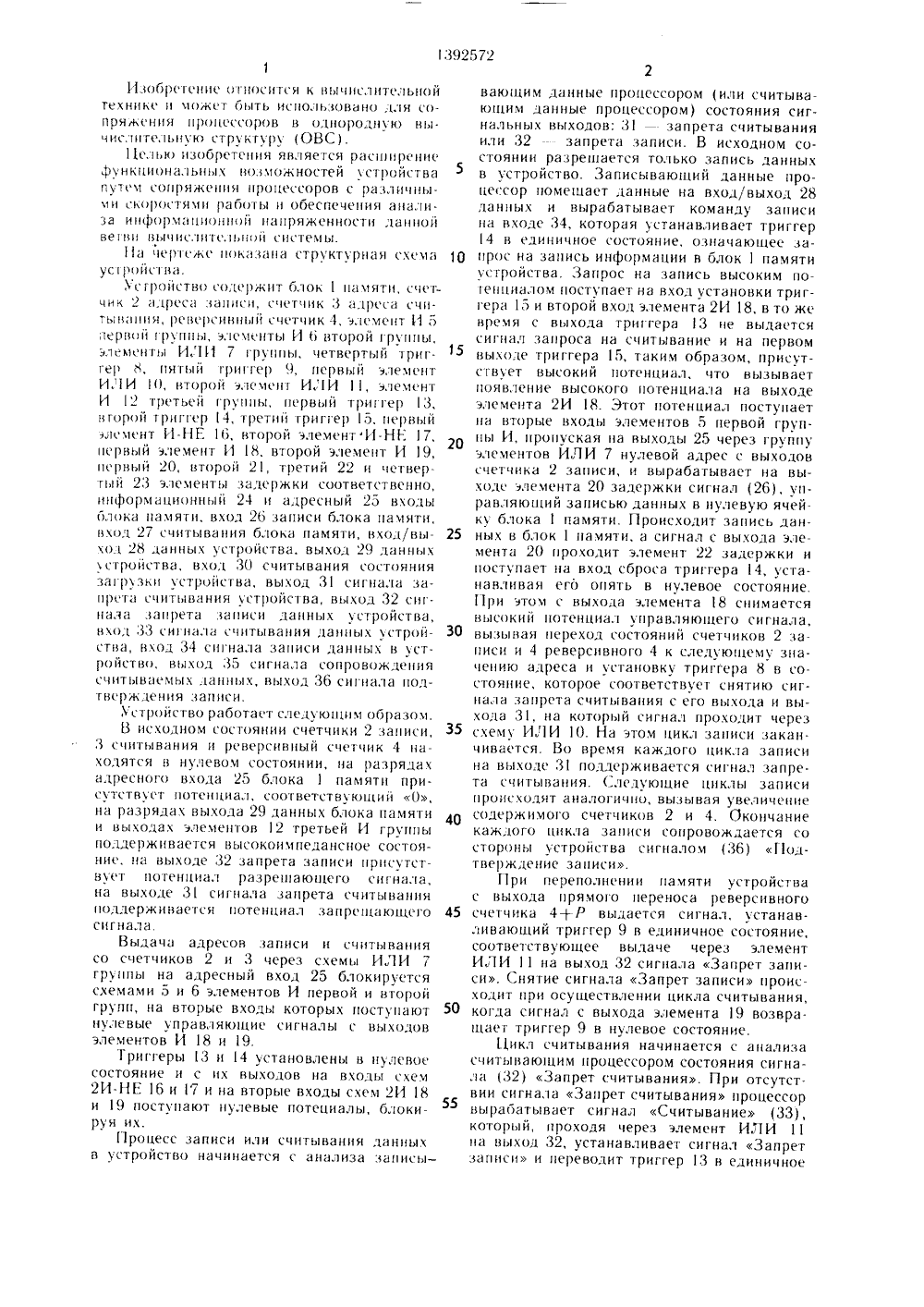

(5 д 4 С 06 Г 15/ бфЦТ,ТЕНИЯ ффц Н АВТОРСКОМУ( СВИДЕТЕЛЬСТВУ С. А. Важиов ство ССС/00, 1981.во СССР3/00, 984 Я СОПРЯЖЕНИЯ НОРОДНОЙ ВЫУКТУРЕтся к вычислительь использовано для ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗО(57) Изобретение относиной технике и может быт сопряжения процессоров в однородную вы. числительную структуру. Целью изобретения является расширение функциональных возможностей устройства за счет сопряжения процессоров с различными скоростями работы и анализа информационной напряженности данной ветви вычислительной системы. Для этого в устройство, содержащее счетчики 2 и 3 адреса записи и считывания соответственно, реверсивный счетчик 4, блок 1 памяти, группы элементов ИЛИ 7 и И 5, б, элементы задержки 20 - 23, элементы И 8, 19, триггеры 13, 14, 15, дополнительно введены два триггера 8, 9, два элемента ИЛИ 10 11, группа элементов 11 2. 1 ил.Изобрстсцие отцо.итси к цислитеэьцой техникс и может быть использовано лля сопряжс ция процессоров в однородную вычислительную структуру (ОВС).11 ег к изобретения является расцирецие функциональных возможностейстройства путеч сопряжения процессоров с различнычи скоростячи ранты и обеспечения ацализд ицфорчционцои цпряженности лап пои веци вычислите.ьцой системы.На чертсжс показана структурная сыча 10 ус гр) сва.Усгройств содержит блок 1 пачяти, счетчик 2 адреса записи, счетчик 3 адреса считышция, ренсрсивц счетчик 4, элемент И 5 первй группы, элечецты И 6 второй группы, элелецт И,1 И 7 группы, четвсртый триггер 8, пятый триггер Ч, первый элемент И,1 ИО, второи элс ченг И,1 И 11, элемент И 12 третьей группы, первый триггер 13, вгорой триггер 14, третий триггер 15, первый элечегг И-НЕ 16, второй элементИ-НЕ 17, ерный элемент И 18, второй элемент И 19, первый 20, второй 21, третий 22 и четвертый 23 элементы задержки соответственно, информационный 24 и адресный 25 входы блока памяти, вход 26 записи блока памяти, вход 27 считывания блока памяти, вход/вы хол 28 данных устройства, выход 29 данныхстройства, вход 30 считывания состояния загрузки устройства, выход 31 сигнала запрет считывания устройства, выход 32 сигнала запрета записи данных устройства, вход 33 сигнала считывания данных устрой .тва, вход 34 сигца,а записи данных в хстройство, выход 35 сигнала сопровождения считываемых даццьх, выход 36 сигнала подтверждения записи.Устройство работает следующим образом.В исходном состоянии счетчики 2 записи, 35 3 считывания и реверсивный счетчик 4 находятся в нулевом состоянии, на разрядах адресного входа 25 блока 1 памяти присутствует потенциал, соответствукщий О, на разрядах выхода 29 данных б ока па яти 40 и выходах элементов 12 третьей И группы поддерживается высокоичпедацсцое состояние, ца выходе 32 запрета записи присугствует потенциал разрешающего сигнала, на выходе 31 сигнала запрета считывания поддерживается потенциал запрецающего 45 сигнала.Выдача адресов записи и считывания со счетчиков 2 и 3 через схемы ИЛИ 7 группы на адресный вход 25 блокируется схемами 5 и 6 элементов И первой и второй групп, на вторые входы которых поступают 50 нулевые управляющие сигналы с выходов элементов И 18 и 19.Триггеры 13 и 14 установлены в нулевое состояние и с их выходов на входы схем 2 И-НЕ 16 и 17 и на вторые входы схем 2 И 18 и 19 поступают нулевые потециалы, блокируя их.Г 1 роцесс записи или считывания данных в устройство начинается с анализа записы -вающим данные процессором (или считывающим данные процессором) состояния сигнальных выходов: 31 запрета считывания или 32 запрета записи. В исходном состоянии разрешается только запись данных в устройство. Записывающий данные процессор помецает данные на вход/выход 28 данных и вырабатывает команду записи на входе 34, которая устанавливает триггер 14 в единичное состояние, означающее запрос на запись информации в блок 1 памяти устройства. Запрос на запись высоким поенциалом поступает на вход установки триггера 15 и второй вход элемента 2 И 18, в то же время с выхода триггера 13 це выдается сигнал запроса на считывание и на первом выыле триггера 15, таким образом, присутствует высокий потенциал, что вызывает появление высокого потенциала на выходе элемента 2 И 18. Этот потенциал поступает ца вторые входы элементов 5 первой группы И, пропуская ца выходы 25 через группу элементов ИЛИ 7 нулевой адрес с выходов счетчика 2 записи, и вырабатывает на выходе элемента 20 задержки сигнал (26), управляющий записью данных в нулевую ячейку блока 1 памяти. Происходит запись данных в блок 1 памяти, а сигнал с выхода элемента 20 проходит элемент 22 задержки и поступает ца вход сброса триггера 14, устанавливая его опять в нулевое состояние. При этом с выхода элемента 18 снимается высокий потенциал управляюпего сигнала, вызывая переход состояний счетчиков 2 записи и 4 реверсивного 4 к слелуюцему значению адреса и установку триггера 8 в состояние, которое соответствует снятию сигнала запрета считывания с его выхода и выхода 31, на который сигнал проходит через схему ИЛИ 10. На этом цикл записи заканчивается. Во время каждого цикла записи на выходе 31 поддерживается сигнал запрета считывания. ( ледующие циклы записи происходят аналогично, вызывая увеличение содержимого счетчиков 2 и 4. Окончание каждого никла записи сопровождается со стороны устройства сигналом (36) Годтверждение записи.Г 1 ри переполнении памяти устройства с выхода прямого переноса реверсивного счетчика 4+Р выдается сигнал, устанавливающий триггер 9 в единичное состояние, соответствующее выдаче через элемент ИЛИ 11 на выход 32 сигнала Запрет записи. Снятие сигнала Запрет записи происходит при осуществлении цикла считывания, когда сигнал с выхода элемента 19 возвращает трипер 9 в нулевое состояние.11 икл считывания начинается с анализа считывающим процессором состояния сигнала (32) Запрет считывания. При отсутствии сигнала Запрет считывания процессор вырабатывает сигнал Считывание (33), который, проходя через элемент И 1 И 11 ца выход 32, устанавливает сигнал Запрет записи и переводит триггер 13 в единичное1 О состояние, озцацдюще здирос нд сцитывдцис информации из блока 1 памяти хстройствд. Этот сигнал устанавливает триггер 15 н нулевое состояние, цри котором нуль с выхола элемента 2 И-НЕ 17 цосгуцает на первый вхол элемента 2 И 18, тем самым блокируя его. Нд второй вхол элемента 2 И 19 поступает елиничцый сигнал с выхола триггера 13 и на выхолс элемента 19 вырабдтывается елиницный сигнал, который разрешает цолачу адреса считывания со сцтчика 3 считывания через группу элемегов И б и группу лементов ИЛИ 7 нд длресные вхслы 25 блока 1 памяти. Информация из блока 1 памяти поступает ца вьхол 29 устройствад цо си Гнд;1 у считывания, н рохол 1- щего с выхола элемента 2 здлс ржки нд вход 27 разрецения считывания блока цахяти.,1 лительнссть сигнала считывания (27) оцрелелятся элементом 23 задержки, с выхолд которого нд выхол 35 подается синдл сопровож;1 ния считывания в сцитывднщий процессор. По сбросу сигнала считывания считывание из блока памяти завершдтся. триггер 13 устанавливается сигналом с выхода элемента 23 залержки в нулевое состояние, ца выхоле элемента 2 И 19 устанавливается низкий потенциал, со,1 ержимо счетчика 3 увеличивается, а реверсивного счетчика 4 - уменьшается на елиницу. с: цолацей на вход 33 устройства слелукццего считывающего сигнала цикл обслуживания запроса считывания цовторяется. При считывании всей информации из устройства солержимое реверсивноп счетчика становится равныл нулю и сигнал с его выхола обратного нерееса - Р) устандвливает трипер 8 в состояние, цри которсл с его выхода сигнал здцрстд считывания поступает через элемент ИЛИ О на выхол 31. Возврат триггера 8 в исходное сстояние цроизволится сигналом с выходд элемента 2 И 18 в цикле записи лднных в устройство.Если си цал считывания прихо;1 ит на вход 33 во время обслуживания запроса записи, он запоминается на триггере 13, не вызывая изменния состояния тригерд 15 ло момента окончания цикла записи, т. е. до сброса триггера 14. После сброса триггера 14 начинается цик, сбслуживания 11)нрс- са считывания.Аналогично, если сигнал запроса записи приходит на вход 34 во время протекания цикла считывания, сигнал запоминается ца триггере 14 и обслуживание запроса записи начинается после окончания цикла считывания, т. е. после сбрса триперд 13.Определение степени заполнения ланцыми устройства производится цри подаче с процессора сигнала считывания состояния загрузки на вхол 3), который цолклкчает разрялы реверсивного счетчика 4 через группу 12 элементов И к шине 28. Анализ процессором содержимого счетчика 4 позволяет определить в однородной вычислительной системе информдциоццуо напряженность 15 20 25 30 35 40 45 50 55 лднной ветви с целью ситихиз)ции здрх.ки всех цроцессоров.Таким образом, цреллдгдемое усгройство осуществляет прием и вылдчу информации цри любом временном рдспложен ни лруг относительно друга сигналов .циси и считывания и разных скоростях рабты цолклк- сннх к нехх црсцсссров.Формула дор гс нзУстройство лля сопряжения црцессоров в однородной вычислительной структу р, сс)держащее счетчик алрссд здциси, сцтцик длреса считывания, реверсивцый счетчик, лве группы элементов И, груццу элсмнпв ИЛИ, блок памяти, четыре элементд залержки, три триггера, первьк вхолы элементов И первой ц второй групп солицены с выхолами соответствукщих рдзрялов счетчиков дЛресд записи и алресд считывания соответствнно, а выхолы соелинень с первым и вторым вхолами элементов ИЛИ группы соответственно, ныхолы которы ссе;1 ицены с алресными вхолдми блокд памяти, выхол первого элемента здлержки ссЛинн с вхолом здциси блока памяти и черсз третий элсмент залержки -- с вхолом сбрссд второо триггера, вхс)л установки котороп сслинн с вхолом режима записи в блок цдмяти стройстзд, д вьхсл вторсго триггерд ссслинц с вхслом сбрс)сд третьего триггрд, вхс,1 усз д нонки которого схс линц с выхолом первого триггера, д вхол устднонки црвоп тригерд соединен с вхолом режима считывания блока памяти устройств 1, вхол сброса црвого триггера соелинц с выхолм четиртого элехентд злркки, вход которого сослинен с выхо;цм второго элемента здлержки и вхолом считывания блока имя 1 и, вхсл которого соелинен с выхоЛом лднцых устрсистца, от,ичаоесн тем, цто, с цельк рдсширения функциоцальцьх возхожцостс й х сгройства путем сопряжения нроцесссров с различными скорсстями работы и обесн- цция анализа информационной напряженнои данной ветви выцислительцой структуры, в него введены четвертый и пятый триггеры, первый и второи элементы ИЛИ, третья груццд элементов И, цсрвый и второй элементы И, первый в 1 ол первого элемента И соелицц спрямым выхолом третьеп триг. гера, второй вхол цсрвого элемента И сслицеи с выхолом второго триперд, выхол цр. вого элементд И сселинен с вхолом первого элемента задержки, вторыми вхоЛдми элементов И первой группы, счстным вхолсм счетчика алреса записи, суммирукиим вхолом реверсивного счетчикд и вхолом сбрссд четвертого триггера, первый вхол второгс элелента И соелинен с инверсцыл выхолом третьего триггера, а второй вхол второго элемента 11 соединен с выхолом первого три- гера, выход второго элемента И соединен с вхолом второго элемента задержки, вторыми входами элементов И второй группы, счетным вхолом сцетчика адреса считывания, выцитд1392572 Составитель Л. ИвановРедактор А.Маковская Техред И. Верес Корректор В. БутягаЗаказ 1809/54 Тираж 704 ПодписноеВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж - 35, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ющим входом реверсивного счетчика и входом сброса пятого триггера, вход установки которого соединен с выходом положительного переполнения реверсивного счетчика, выход пятого триггера соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого триггера, выход второго элемента ИЛИ соединен с выходом сигнала запрещения записи данных устройства, вход установки четвертого триггера соединен с выходом заема реверсивного счетчика, выход четвертого триггера соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго триггера, выход первого элемента ИЛИ является выходом сигнала запрещения считывания данных устройства, информационные выходы реверсивного счетчика соединены с вторыми входами элементов И третьей группы, первые входы которых соединены с входом сигнала считывания состояния загрузки устройства, выходы элементов И третьей группы соединены с входом/ /выходом данных устройства и информационным входом блока памяти, выход третьего элемента задержки соединен с выходом сигнала подтверждения записи данных устройства, выход четвертого элемента задержки является выходом сигнала сопровождения считываемых данных устройства.

СмотретьЗаявка

4165620, 24.12.1986

ПРЕДПРИЯТИЕ ПЯ Р-6609

МАКСИМЕНКО ВЛАДИМИР НИКОЛАЕВИЧ, ВАЖНОВ СЕРГЕЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 15/163

Метки: вычислительной, однородной, процессоров, сопряжения, структуре

Опубликовано: 30.04.1988

Код ссылки

<a href="https://patents.su/4-1392572-ustrojjstvo-dlya-sopryazheniya-processorov-v-odnorodnojj-vychislitelnojj-strukture.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сопряжения процессоров в однородной вычислительной структуре</a>

Предыдущий патент: Устройство для сопряжения вычислительной машины с телеграфными каналами связи

Следующий патент: Устройство для моделирования систем передачи и обработки информации

Случайный патент: Бобинецдля оснастки трала