Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

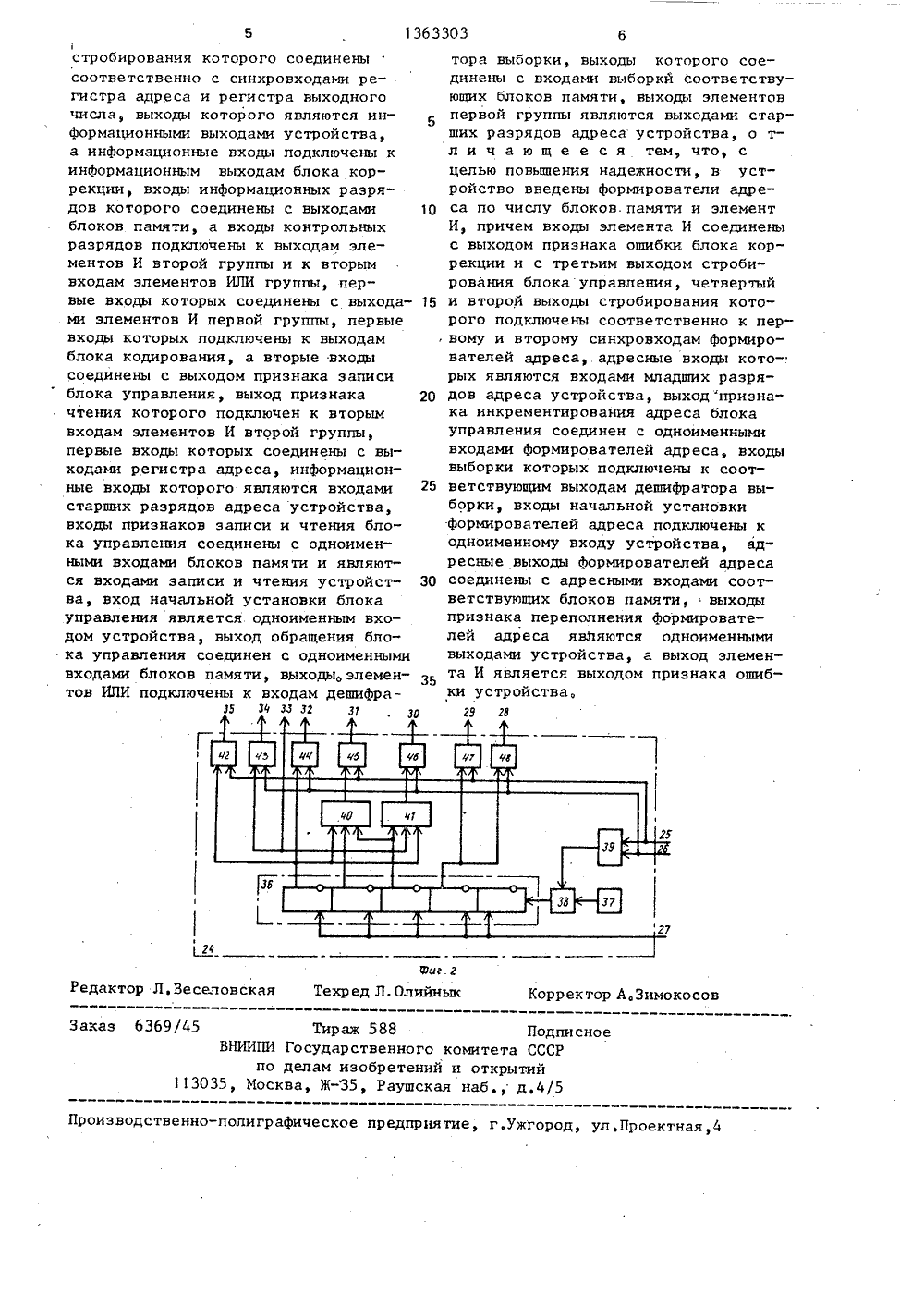

СОЮЗ СОВЕТСКИ)1СОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 19) 01) 1) 4 С 11 С 11/О ОПИСАНИЕ ИЗОБРЕТЕНИЯ ДЕТЕЛЬ СПс ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРпо делАм изОБРетений и ОткРытии(56) Авторское свидетельство СССР У 68799, кл, С 11 С 29/00, 1976,Авторское свидетельство СССР В 841059, кл. С 11 С 29/00 1981(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С И РАВПЕНИЕИ ОП)ИБОК(57) Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройств. Целью изобретения является повышение надежности устройтва. Устройство содержит накопитель,входной 1 и выходной 20 регистры числа,: регистр 3 адреса, блок 5 кодирования, блок коррекции, блок 24 управления, дешифратор 10 выборки, формирователи 49 адреса, первую 6 ивторую 9 группы элементов И, группу8 элементов ИЛИ, элемент И 12, В устройстве накопитель разделен на блокипамяти, в каждом из которых хранятсяслова, имеющие одинаковое значениеконтрольных разрядов, используемыхв качестве старших разрядов кода адреса. Это позволяет исключить необходимость хранения контрольных разрядов в накопителе, что ведет к увеличению надежности всего запоминающего устройства, 2 ил.10 20 30 35 40 50 55 Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройстн,Целью изобретения является повышение надежности устройства,На фиг,1 приведена схема запоминающего устройства с исправлением ошибок, на фиг.2 -. схема блока управления,Устройство (фиг,1) содержит входной регистр 1 числа с информационными входами 2, регистр 3 адреса.с инФормационными входами 4, блок 5 кодирования, первую группу элементовИ 6 с выходами 7, группу элементовИЛИ 8, вторую группу элементов И 9,дешифратор 10 выборки, блоки 11 памяти, элементы И 12, счетчики 13, дешифраторы 14, элементы И 15, входы16, выходы 17 и 18, блок 19 коррекции, регистр выходного 20 числа свыходами 21, элемент И 22 с выходом23, блок 24 управления с входами 2527 и выходами 28 - 35,Блок 24 управления (Фиг.2) содержит сдвиговый регистр 36, генератор37, элемент И 38, элементы ИЛИ 3941, элементы И 42 - 48.Блоки 12 - 15 на фиг,1 объединены в формирователи 49 адреса.Предполагается, что для обнаружения и исправления ошибок х-й кратности / Ь 1/ необходимо формировать Кконтрольных разрядон. Тогда количество блоков памяти 11 и, следовательно, элементов И 12, счетчиков 13, дешифраторон 14, элементов И 15 выбирается равным 2 . Это объясняется тем,что в каждый блок памяти заносятсяслова, имеющие одинаковую комбинациюконтрольных разрядов (контрольныйкод)оЗапоминающее устройство с исправлением ошибок работает следующимобразом,Сначала н режиме записи происходит занесение информации в блоки 11памяти устройства. В этом режиме навход 26 устройства поступает сигнал,определяющий режим записи, а навход 27 - сигнал начальной установки. С входа 26 сигнал поступает вузел 24 управления и на управляющиевходы блоков 11 памяти, Сигнал с вхоца 27 поступает на входы обнулениясчетчиков 13 и н блок 24 управления,где устанавливает первый триггер регистра 36 сдвига н единичное состояние, а остальные триггеры регистра - н нулевое. Сигнал с входа 26 через элемент ИЛИ 39 открывает элемент И 38, и тактовые сигналы от генератора 37 через элемент И 38 поступают на сдвигоный вход регистра 36. Записанная в первый триггер единица сдвигается по каждому тактовому сигналу в следующий разряд регистра. Сигналы с единичных выходов триггеров регистра 36 поступают на элементы ИЛИ 40 и 41 и элементы И 42 - 48. На выходах элементов И 43, 44 46 и 48 формируются управляющие сигналы, обеспечивающие работу устройства в режиме записи.По сигналу с выхода 28 блока 24 управления во входной регистр 1 свхода 2 принимается записываемое слово, Оно поступает на блок 5 кодиро-,вания, где формируются необходимыеконтрольные разряды для обеспечения обнаружения и исправления ошибок д-йкратности, Кроме того, записываемоеслово подается на информационныевходы блоков 11 памяти с целью последующей записи. По сигналу с выхода 30 контрольные разряды через первую группу элементов И 6 поступают на один из входов элементов ИЛИ 8 и затем на дешифратор 10. Контрольные разряды подаются также на выход 7 устройства и используются в дальнейшем как старшие разряды адреса обращения к записанному слону, На выходе дешифратора 1 О формируется сигнал обращения к одному из блоков 11 памяти в соответствии с поступившим кодом. Таким образом, контрольные разряды обеспечивают выбор конкретного блока памяти и являются старшими разрядами адреса, 1Сигнал на выходе 33 блока 24 угравления запускает выбранный блок 11 памяти. Адрес ячейки блока памяти определяется соответствующим дешифратором 14, на вход которого подаются сигналы с выхода соответствующего счетчика 13, Сигналы с выходов счетчика 13 поступают также на выходустройства с целью последующего чспользования для формиронаия адреса считывания, Поскольку предварительно все счетчики 13 обнулены, то слово записывается и нулевую ячейку выбранного накопителя, Одновременно по сигналу 34 опрашивается состояние35 счетчиков 13. Если в счетчике записаны все единицы, т.е. содержимое егомаксимально, то с последнего (старшего) выхода соответствующего дешифратора 14 сигнал через элемент И 15поступает на выход 18 устройства.Этот сигнал является свидетельствомтого, что все ячейки данного блокапамяти заполнены и для дальнейшей 10записи необходимо увеличить его емкость.Сигнал с выхода 32 через соответствующий элемент И 12, открытый сигналом с выхода дешифратора 10, обеспе чивает прибавление единицы в соответствующий счетчик 23 и, тем сажм,формирует адрес очередной ячейки дляданного блока памяти.На этом цикл записи слова заканчивается и выполняется запись очередного слова, Если запись производится в этот же.блок памяти, то словозаносится в следующую по номеру ячейку, Если же производится запись в 25другой блок памяти, то она начинается с нулевойячейки. Под воздействиемсигналов сдвига единица по кольцуциркулирует в регистре 36 сдвига,обеспечивая формирование необходимых ЗОуправляющих сигналов. Окончание процесса записи определяется снятиемс входа 26 устройства управляющегосигнала.По окончании записи информации вкажцом блоке 11 памяти записаны слова, имеющие одинаковые контрольныеразряды,Режим считывания определяетсясигналом, поступающим на вход 25 40устройства, и сигналом начальнойустановки по входу 27. Сигнал начальнойустановки обнуляет счетчик 13 и устанавливает в исходное состояниетриггеры регистра 36 сдвига блока 24 45управления, Сигнал с входа 25 подается на блоки 11 памяти и определяетрежим их работы, В блоке 24 управления этот сигнал через элемент ИЛИ39 открывает элемент И 38, и сигналыс генератора 37 поступают на регистр36На выходе элементов И 42, 45 и47 формируются сигналы, управляющиевзаимодействием блоков устройства врежиме считывания,55По сигналу с выхода 29 в регистр3 с входа 4 принимаются разряды адреса, определяющие номер блока 11 памяти, Эти разряды фактически представляют собой контрольный код длясчитываемого слова, Сигнал с выхода29 поступает также на управляющиевходы счетчиков 13 и обеспечиваетприем в них с входа 16 младших раз".рядов адреса, определяющих номерячейки, к которой выполняется обращение. Дешифраторы 14 подготавливаютвыбор ячейки в соответствии с адресом,По сигналу с выхода 31 блока 24управления старшие разряды адреса,из регистра 3 через элементы И 9второй группы и элементы ИЛИ 8 поступают на дешифратор 10 для выбораодного из накопителей,По сигналу с выхода 33 блока 24управления запускается выбранныйблок 11 памяти, и содержимое ячейки, определенной дешифратором 14,считывается в блок 19 коррекции.На блок 19кроме того, поступаютс выхода элементов И 9 старшие разряды адреса, являющиеся контрольными разрядами. В блоке 19 коррекцииосуществляется обнаружение и, есливозможно, исправление ошибок.По сигналу с выхода 35 скорректированное слово принимается в выход"ной регистр 20 и далее на выход 21.Если в считанном слове возникла неисправимая ошибка, то по этому жесигналу на выходе элемента И 22формируется .сигнал, который посту-.пает на выход 23 устройства, Сигнална этом выходе информирует о том,что слово, находящееся в выходномрегистре 20, содержит неисправимыеошибки,Аналогично выполняется считывание очередного слова.Окончание режима считывания определяется снятием сигнала с входа 25 устройства.Формула изобретения.апоминающее устройство с исправлением ошибок, содержащее блоки памяти, информационные входы которых соединены с входами блока кодирования и с вьгходами входного регистра числа, информационные входы которого являются информационными входами устройства, а синхровход подключен к первому выходу стробирования блока управления, второй и третий выходы, Олиинык Заказ 6369 45 Тираж 588 ВНИИПИ Государственного по делам изобретений 13035, Москва, Ж"35, Раушскаясное Подомитета СССи открытийнаб д,4/ Проектная,4 оизводственно-полиграфическое предприятие, г,ужгород стробирования которого соединены соответственно с синхровходами регистра адреса и регистра выходного числа, выходы которого являются информационными выходами устройства, а информационные входы подключены к информационным выходам блока коррекции, входы информационных разрядов которого соединены с выходами блоков. памяти, а входы контрольных разрядов подключены к выходам элементов И второй группы и к вторым входам элементов ИЛИ группы, первые входы которых соединены с выходами элементов И первой группы, первые входы которых подключены к выходам блока кодирования, а вторые входы соединены с выходом признака записи блока управления, выход признака чтения которого подключен к вторым входам элементов И второй группы, первые входы которых соединены с выходами регистра адреса, информационные входы которого являются входами старших разрядов адреса устройства, входы признаков записи и чтения блока управления соединены с одноименными входами блоков памяти и являются входами записи и чтения устройства, вход начальной установки блока управления является одноименным входом устройства, выход обращения блока управления соединен с одноименными входами блоков памяти, выходы, элементов ИЛИ подключены к входам дешифраы илюг зу тора выборки, выходы которого соединены с входами выборкй соответствующих блоков памяти, выходы элементов 5первой группы являются выходами старших разрядов адреса устройства, о тл и ч а ю щ е е с я тем, что, сцелью повышения надежности, в устройство введены формирователи адре са по числу блоков. памяти и элементИ, причем входы элемента И соединеныс выходом признака ошибки блока коррекции и с третьим выходом стробирования блока управления, четвертый 15 и второй выходы стробирования которого подключены соответственно к первому и второму синхровходам формирователей адреса, адресные входы которых являются входами младших разря дов адреса устройства, выход признака инкрементирования адреса блокауправления соединен с одноименнымивходами формирователей адреса, входывыборки которых подключены к соот ветствующим выходам дешифратора выборки, входы начальной установкиформирователей адреса подключены кодноименному входу устройства, адресные выходы формирователей адреса ЗО соединены с адресными входами соответствующих блоков памяти, выходыпризнака переполнения формирователей адреса явЛяются одноименнымивыходами устройства, а выход элемен та И является выходом признака ошибки устройства,

СмотретьЗаявка

4095497, 06.05.1986

ПУШКИНСКОЕ ВЫСШЕЕ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

ГОРБЕНКО АЛЕКСАНДР СЕРГЕЕВИЧ, ТЕРНОВОЙ ВАЛЕРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G11C 11/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 30.12.1987

Код ссылки

<a href="https://patents.su/4-1363303-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Устройство для перемещения магнитной головки

Следующий патент: Генератор цилиндрических магнитных доменов

Случайный патент: Устройство для измерения длины вращающегося плеча центрифуги