Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

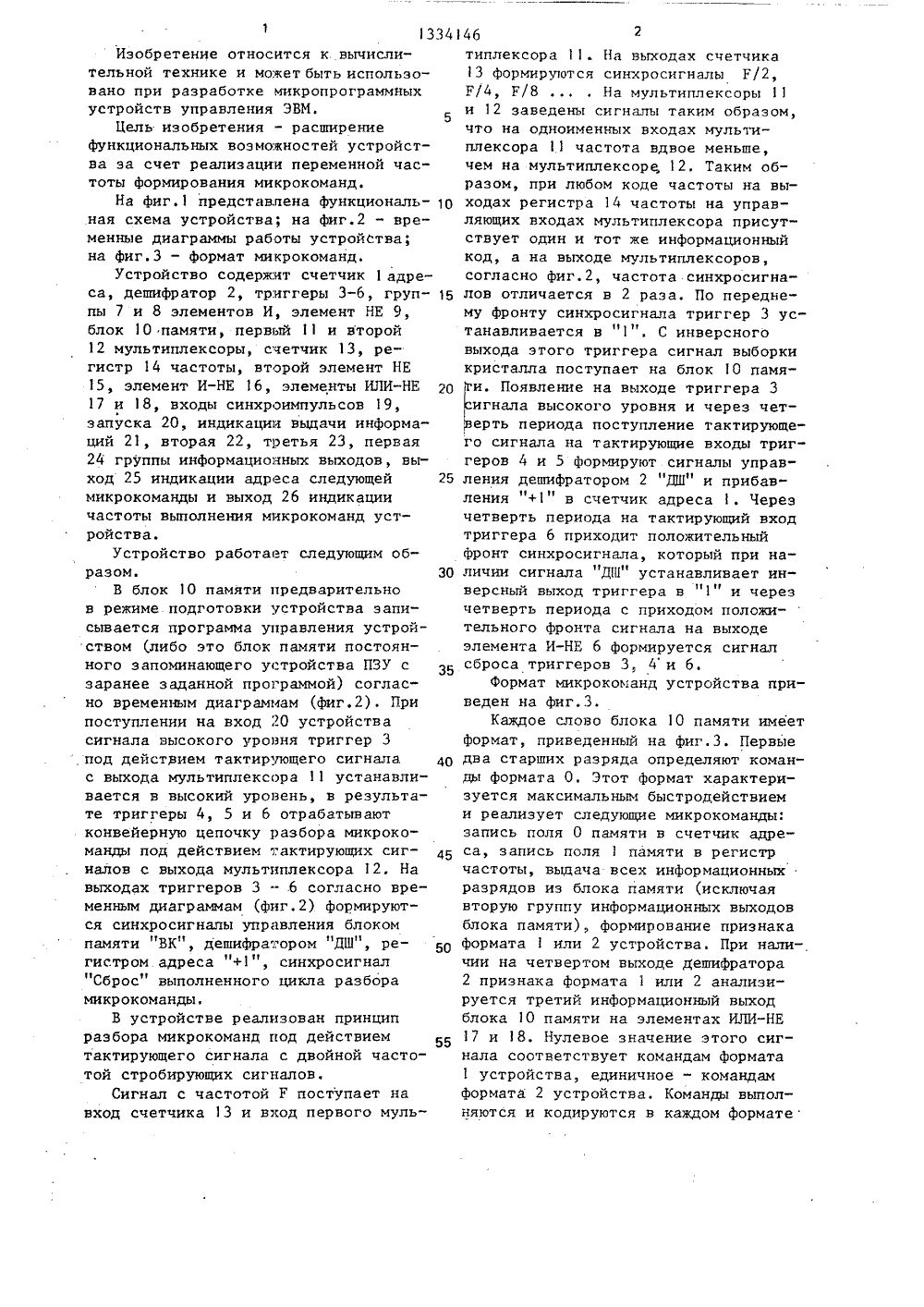

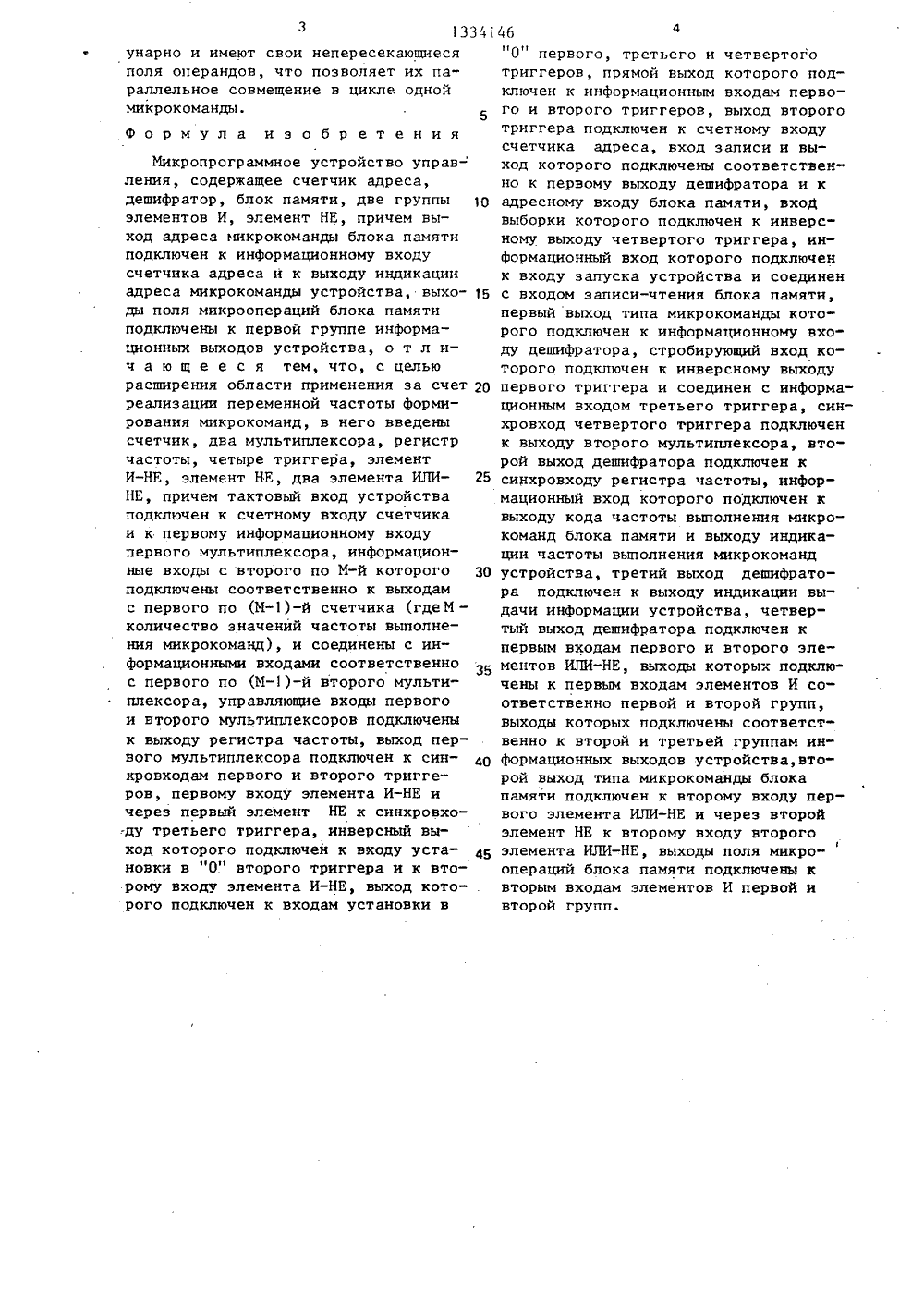

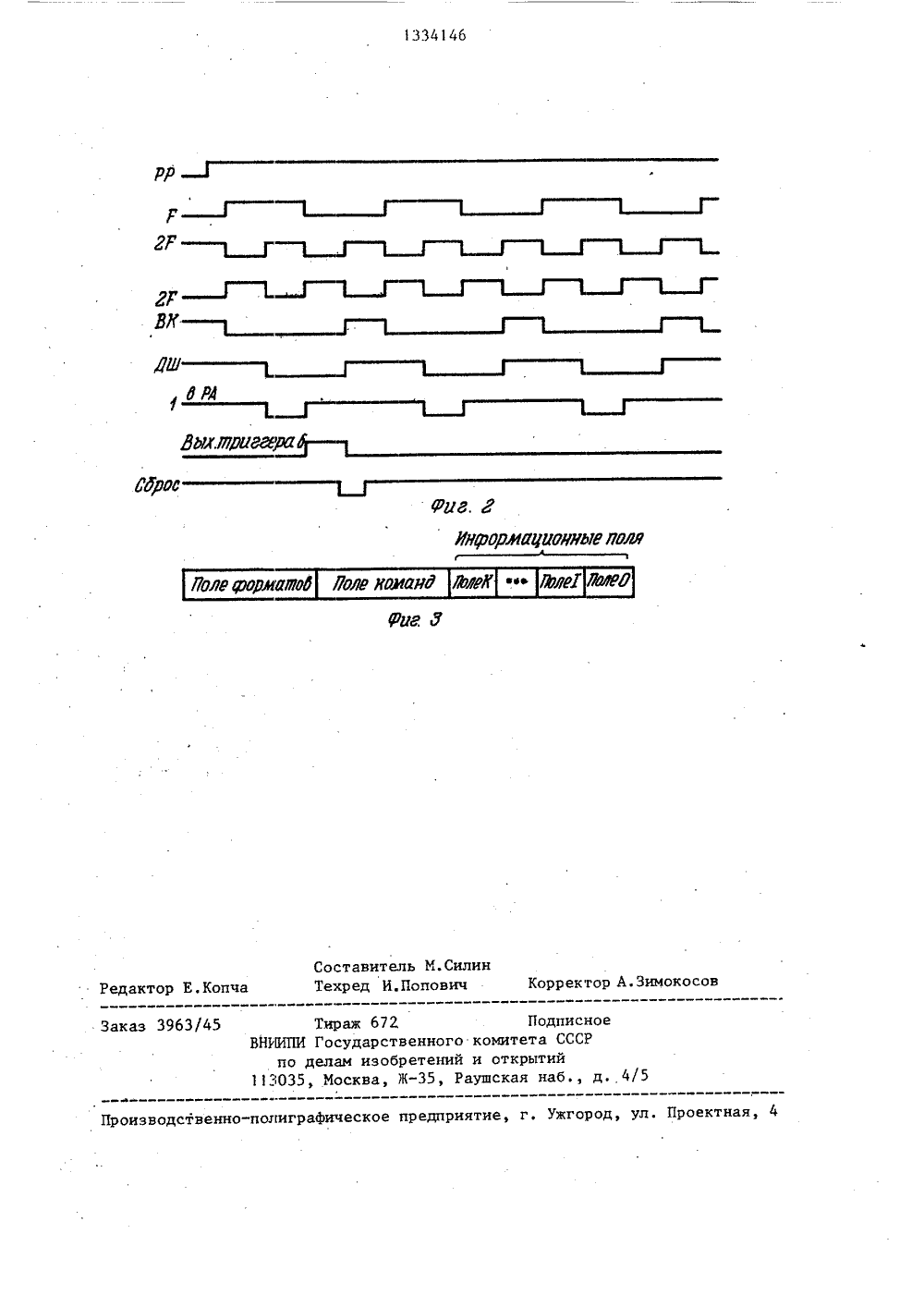

.П.Васильев,арпунин, 10.П.Кр В.И.Песоченк И азов и8.8) вление. вып 39.Авторское 28356, кл видетельство СССР С 06 Г 9/22, 1980(5 4) МИКР УПРАВЛЕНИЯ (57) Микр управлени роля и ди рог отн аммное устроиство тся к технике кон 22 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ Микропрограммное уп- . М.: М р, 1973,РОГРАММНОЕ УСТРОИСТВ ностики цифровых устроис. и может быть использовано при разработке микропрограммных устройств управления ЭВМ, микропроцессорных устройств. Цель изобретения - расширение функциональных возможностей уст- ройства за счет реализации переменной частоты формирования микрокоманд. Сущность изобретения состоит в том, что в известное устройство, содержащее счетчик 1 адреса, дешифратор 2, блок памяти 10, две группы элементов И 7, 8, первый элемент НЕ 9, дополнительно введены счетчик 13, первый и второй мультиплексоры 11, 12, регистр 14 частоты, четыре триггера 3- 6, элемент И-НЕ 16, второй элемент НЕ 15, два элемента ИЛИ-НЕ 17, 18.3 ил13341Изобретение относится к вычислительной технике и может быть использовано при разработке микропрограммных устройств управления ЭВМ.Цель изобретения - расширение функциональных воэможностей устройства за счет реализации переменной частоты формирования микрокоманд.На фиг, представпена функциональ ная схема устройства; на фиг.2 - временные диаграммы работы устройства; на фиг.З - формат микрокоманд.Устройство содержит счетчик 1 адреса, дешифратор 2, триггеры З-б, груп пы 7 и 8 элементов И, элемент НЕ 9, блок 10 памяти, первый 11 и второй 12 мультиплексоры, счетчик 13, регистр 14 частоты, второй элемент НЕ 15, элемент И-НЕ 16, элементы ИЛИ-НЕ 20 17 и 18, входы синхроимпульсов 19, запуска 20, индикации выдачи информаций 21, вторая 22, третья 23, первая 24 группы информационных выходов, выход 25 индикации адреса следующей 25 микрокоманды и выход 26 индикации частоты выполнения микрокоманд устройства.Устройство работает следующим образом. 30В блок 10 памяти предварительно в режиме подготовки устройства записывается программа управления устройством (либо это блок памяти постоянного запоминающего устройства ПЗУ с заранее заданной программой) согласно временным диаграммам (фиг.2). При поступлении на вход 20 устройства сигнала высокого уровня триггер 3 под действием тактирующего сигнала. с выхода мультиплексора 11 устанавливается в высокий уровень, в результате триггеры 4, 5 и 6 отрабатывают конвейерную цепочку разбора микрокоманды под действием тактирующих сиг иалов с выхода мультиплексора 12, На выходах триггеров 3 - 6 согласно временным диаграммам (фиг.2) формируются синхросигналы управления блоком памяти "ВК", дешифратором "ДШ , регистром адреса "+1", синхросигнал "Сброс" выполненного цикла разбора микрокоманды.В устройстве реализован принцип разбора микрокоманд под действием тактирующего сигнала с двойной частотой стробирующих сигналов.Сигнал с частотой Р поступает на вход счетчика 13 и вход первого муль46 2 типлексора 1. На выходах счетчика 3 формируются синхросигналы Г/2, Р/4, Р/8. На мультиплексоры 11 и 12 заведены сигналы таким образом, что на одноименных входах мультиплексора 11 частота вдвое меньше, чем на мультиплексоре, 12. Таким образом, при любом коде частоты на выходах регистра 14 частоты на управляющих входах мультиплексора присутствует один и тот же информационный код, а на выходе мультиплексоров, согласно фиг.2, частота синхросигналов отличается в 2 раза. По передне- му фронту синхросигнала триггер 3 устанавливается в "1". С инверсного выхода этого триггера сигнал выборки кристалла поступает на блок О памяи. Появление на выходе триггера 3 игнала высокого уровня и через чет- ерть периода поступление тактирующего сигнала на тактирующие входы триг- геров 4 и 5 формируют сигналы управления дешифратором 2 "ДШ" и прибав" ления "+1" в счетчик адреса 1. Через четверть периода на тактирующий вход триггера 6 приходит положительный фронт синхросигнала, который при наличии сигнала "ДШ" устанавливает инверсный выход триггера в "1" и через четверть периода с приходом положительного фронта сигнала на выходе элемента И-НЕ б формируется сигнал сброса триггеров 3, 4 и бФормат микрокоманд устройства при- веден на фиг.З.Каждое слово блока 1 О памяти имеет формат, приведенный на фиг.З. Первые два старших разряда определяют коман- ды формата О. Этот формат характеризуется максимальным быстродействием и реализует следующие микрокоманды: запись поля О памяти в счетчик адреса, запись поля 1 памяти в регистр частоты, выдача всех информационных разрядов из блока памяти (исключая вторую группу информационных выходов блока памяти), формирование признака формата 1 или 2 устройства. При нали- чии на четвертом выходе дешифратора 2 признака формата 1 или 2 анализируется третин информационный выход блока 1 О памяти на элементах ИЛИ-НЕ 17 и 18. Нулевое значение этого сигнала соответствует командам формата 1 устройства, единичное - командам формата 2 устройства. Команды выполняются и кодируются в каждом формате13341унарно и имеют свои непересекающиеся поля операндов, что позволяет их параллельное совмещение в цикле одной микрокоманды.ф о р м у л а и з о б р е т е н и яМикропрограммное устройство управ- ления, содержащее счетчик адреса, дешифратор, блок памяти, две группы 1 О элементов И, элемент НЕ, причем выход адреса иикрокоманды блока памяти подключен к информационному входу счетчика адреса и к выходу индикации адреса микрокоманды устройства, выхо ды поля микроопераций блока памяти подключены к первой группе информационных выходов устройства, о т л ич а ю щ е е с я тем, что, с целью расширения области применения за счет 2 О реализации переменной частоты формирования микрокоманд, в него введены счетчик, два мультиплексора, регистр частоты, четыре триггера, элемент И-НЕ, элемент НЕ, два элемента ИЛИ Б НЕ, причем тактовый вход устройства подключен к счетному входу счетчика и к первому информационному входу первого мультиплексора, информационные входы с второго по М-й которого 30 подключены соответственно к выходам с первого по (М)-й счетчика (гдеМ- количество значений частоты выполнения микрокоманд), и соединены с информационными входами соответственно с первого по (М)-й второго мультиплексора, управляющие входы первого и второго мультиплексоров подключены к выходу регистра частоты, выход первого мультиплексора подключен к син О хровходам первого и второго триггеров, первому входу элемента И-НЕ и через первый элемент НЕ к синхровходу третьего триггера, инверсный выход которого подключен к входу уста новки в "О" второго триггера и к второму входу элемента И-НЕ, выход кото- . рого подключен к входам установки в 464О" первого, третьего и четвертого триггеров, прямой выход которого подключен к информационным входам первого и второго триггеров, выход второго триггера подключен к счетному входу счетчика адреса, вход записи и выход которого подключены соответственно к первому выходу дешифратора и к адресному входу блока памяти, вхоД выборки которого подключен к инверсному выходу четвертого триггера, информационный вход которого подключен к входу запуска устройства и соединен с входом записи-чтения блока памяти, первый выход типа микрокоманды которого подключен к информационному входу дешифратора, стробирующий вход которого подключен к инверсному выходу первого триггера и соединен с информационным входом третьего триггера, синхровход четвертого триггера подключен к выходу второго мультиплексора, второй выход дешифратора подключен к синхровходу регистра частоты, информационный вход которого подключен к выходу кода частоты выполнения микро- команд блока памяти и выходу индикации частоты выполнения микрокоманд устройства, третий выход дешифратора подключен к выходу индикации выдачи информации устройства, четвертый выход дешифратора подключен к первым входам первого и второго элементов ИЛИ-НЕ, выходы которых подклю" чены к первым входам элементов И соответственно первой и второй групп, выходы которых подключены соответственно к второй и третьей группам информационных выходов устройства,второй выход типа микрокоманды блока памяти подключен к второму входу первого элемента ИЛИ-НЕ и через второй элемент НЕ к второму входу второго элемента ИЛИ-НЕ, выходы поля микро" операций блока памяти подключены к вторым входам элементов И первой и второй групп.1334146 Риг. 8 Мнрсрмацианньмтпя Составитель М.СилинТехред И.Попович Корректор А.Зимокосов ор Е.Копча аз 3963/45 Производственно-полиграФическое предприятие, г. Ужгород, ул. Проектная, 4 ГГ ВХ Тираж 672 ВНИИПИ Государственного к по делам изобретений и 113035, Москва, Ж, РаушПодписноемитета СССРоткрытийская наб д. 4/

СмотретьЗаявка

3995122, 23.12.1985

ПРЕДПРИЯТИЕ ПЯ Р-6052

БУЧНЕВ АЛЕКСАНДР НИКОЛАЕВИЧ, ВАСИЛЬЕВ НИКОЛАЙ ПЕТРОВИЧ, ГОРОВОЙ ВЛАДИМИР РОДИОНОВИЧ, КАРПУНИН ЕВГЕНИЙ ИВАНОВИЧ, КРЫЛАТЫХ ЮРИЙ ПЕТРОВИЧ, МАТАЗОВ АНАТОЛИЙ НИКОЛАЕВИЧ, ПЕСОЧЕНКО ВАСИЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.08.1987

Код ссылки

<a href="https://patents.su/4-1334146-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Цифровой интегратор

Следующий патент: Устройство циклического приоритета

Случайный патент: Устройство компенсации реактивной мощности