Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1309024

Авторы: Газиян, Мартиросян, Мурадханян, Саркисян, Тамазян

Текст

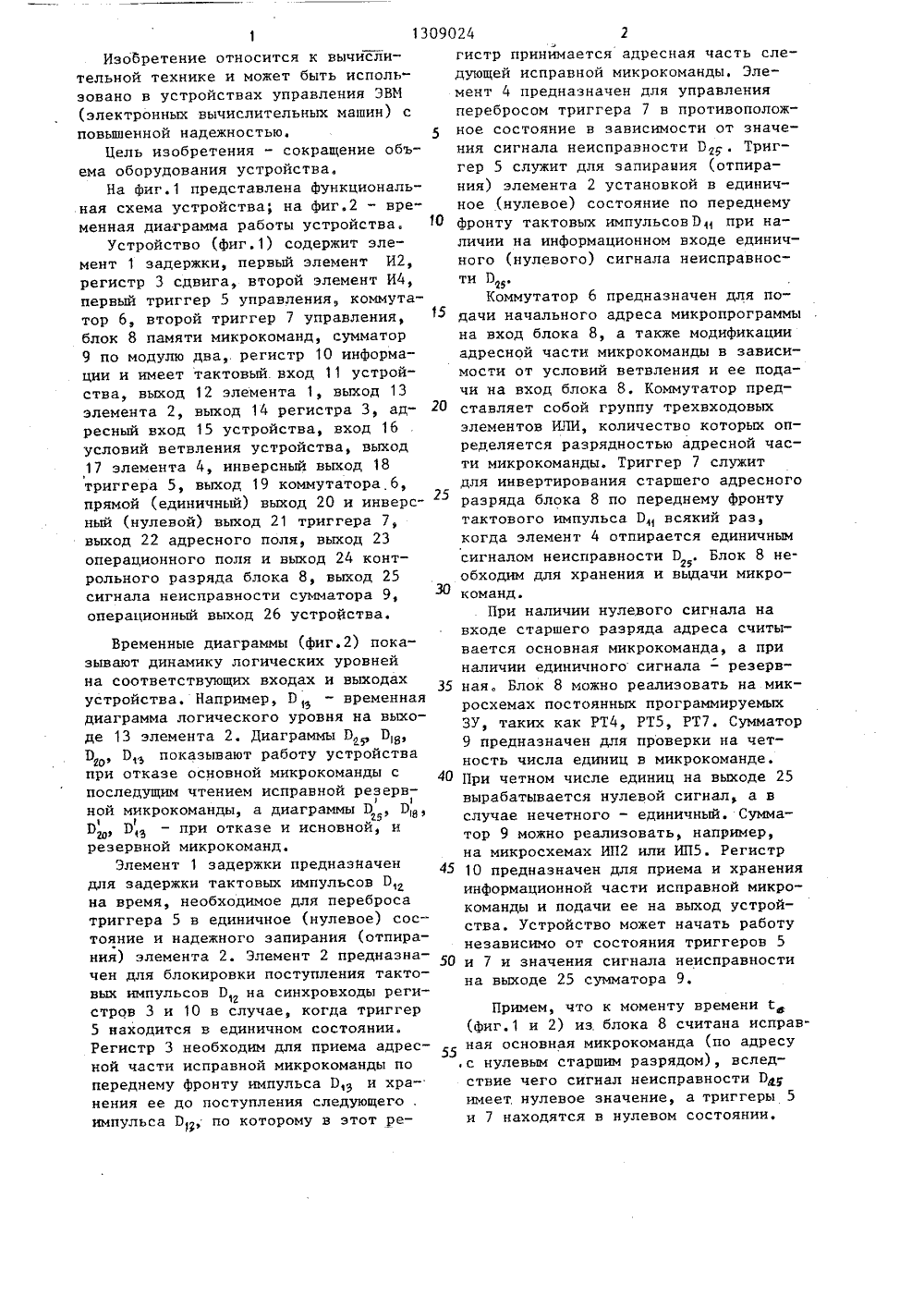

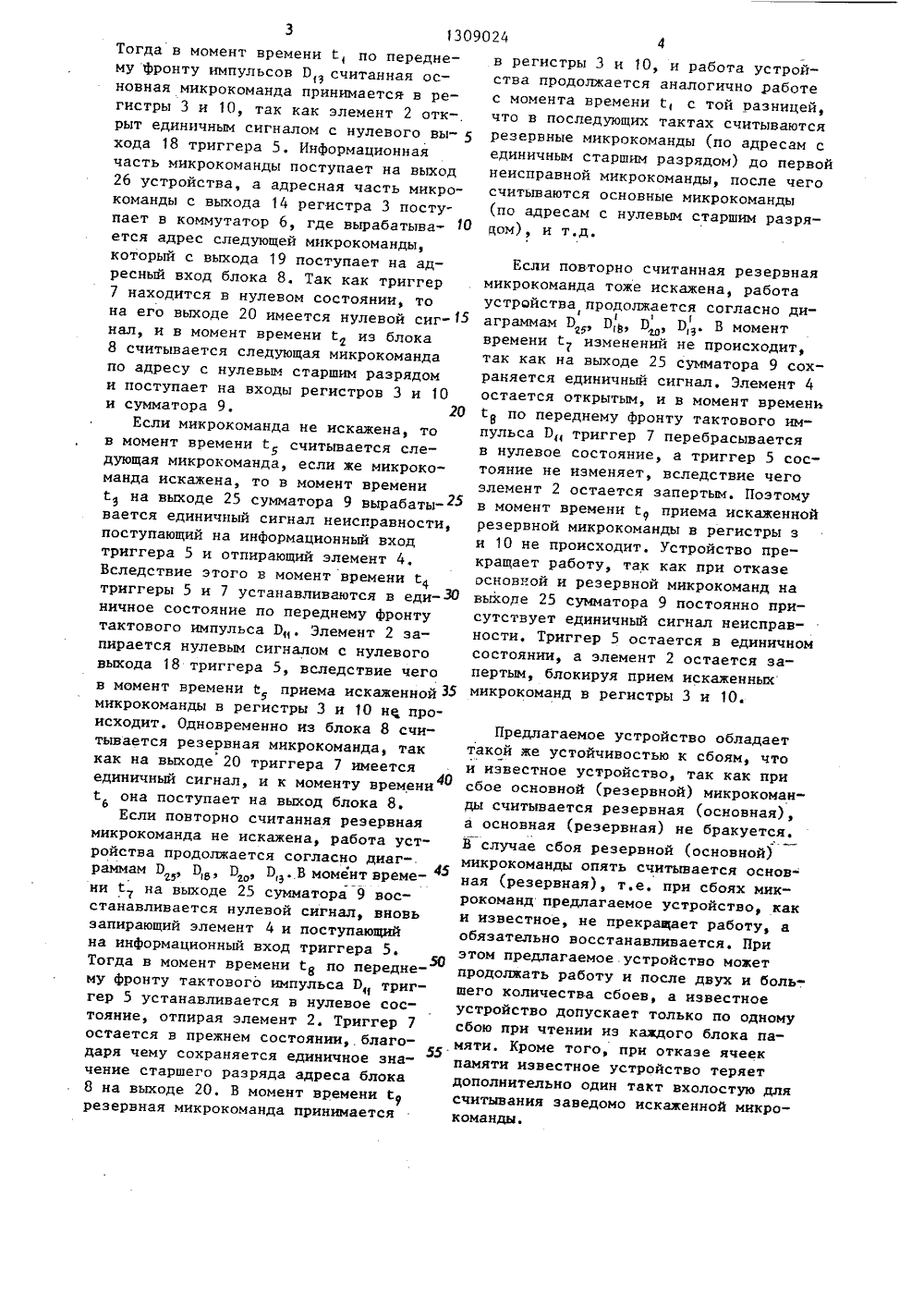

СОВХОЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 1 4 С 06 Г 9/22 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ЪОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетельство СССРВ 993261, кл. С 06 Р 9/22, 1981.Авторское свидетельство СССРВ 938283, кл. С 06 Г 9/22, 1980.Авторское свидетельство СССРУ 1043652, кл, С 06 Г 9/22, 1981.Авторское свидетельство СССРВ 1007 108, кл, С 06 Р 9/22, 1981.(57) Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ (электронных вычислительных машин) с повышенной надежностью, Целью изобретения является сокращение объема оборудования устройства. С этой целью в устройство, содержащее блок 8 памяти микрокоманд, регистр 3 адреса, коммутатор 6, два триггера 5,7 управления, два элемента И 2,4 и элементзадержки, введены сумматор 9 по модулю два и регистр 10 информации, что позволяет обеспечить равные с известными устройствами параметры надежности при исключении из их состава д второго блока памяти микрокоманд и средств для формирования его входных и выходных сигналов. 2 ил.Изобретение относится к вычислительной технике и может быть исполь" зовано в устройствах управления ЭВМ (электронных вычислительных машин) с повышенной надежностью.Цель изобретения - сокращение объема оборудования устройства. На фиг,1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма работы устройства,Устройство (фиг.1) содержит элемент 1 задержки, первый элемент И 2, регистр 3 сдвига, второй элемент И 4,первый триггер 5 управления, коммутатор 6, второй триггер 7 управления, блок 8 памяти микрокоманд, сумматор 9 по модулю два, регистр 10 информации и имеет тактовый. вход 11 устройства, выход 12 элемента 1, выход 13 элемента 2, выход 14 регистра 3, адресный вход 15 устройства, вход 16 условий ветвления устройства, выход 17 элемента 4, инверсный выход 18 триггера 5, выход 19 коммутатора 6,прямой (единичный) выход 20 и инверсный (нулевой) выход 21 триггера 7, выход 22 адресного поля, выход 23 операционного поля и выход 24 контрольного разряда блока 8, выход 25 сигнала неисправности сумматора 9, операционный выход 26 устройства.Временные диаграммы (фиг.2) показывают динамику логических уровней на соответствующих входах и выходахустройства. Например, В, - временнаядиаграмма логического уровня на выходе 13 элемента 2, Диаграммы 025, Рв,Э , Пз показывают работу устройствапри отказе основной микрокоманды споследущим чтением исправной резерв 1ной микрокоманды, а диаграммы Р , Пш,125 фР , П,з - при отказе и исновной, ирезервной микрокоманд.Элемент 1 задержки предназначендля задержки тактовых импульсов 0,2на время, необходимое для перебросатриггера 5 в единичное (нулевое) состояние и надежного запирания (отпирания) элемента 2, Элемент 2 предназначен для блокировки поступления тактовых импульсов О, на синхровходы регистров 3 и 10 в случае, когда триггер5 находится в единичном состоянии.Регистр 3 необходим для приема адресной части исправной микрокоманды по переднему фронту импульса П, и хранения ее до поступления следующего . импульса Р, по которому в этот ре гистр принимается адресная часть следующей исправной микрокоманды. Элемент 4 предназначен для управленияперебросом триггера 7 в противоположное состояние в зависимости от значения сигнала неисправности Р 25 . Триггер 5 служит для запираыия (отпирания) элемента 2 установкой в единичное (нулевое) состояние по переднемуФронту тактовых импульсовР 11 при наличии на информационном входе единичного (нулевого) сигнала неисправнос 25Коммутатор 6 предназначен для подачи начального адреса микропрограммына вход блока 8, а также модификацииадресной части микрокоманды в зависимости от условий ветвления и ее подачи на вход блока 8. Коммутатор представляет собой группу трехвходовыхэлементов ИЛИ, количество которых определяется разрядностью адресной части микрокоманды. Триггер 7 служитдля инвертирования старшего адресногоразряда блока 8 по переднему фронтутактового импульса 01 всякий раз,когда элемент 4 отпирается единичнымсигналом неисправности Р . Блок 8 не 25обходим для хранения и выдачи микрокоманд.При наличии нулевого сигнала навходе старшего разряда адреса считывается основная микрокоманда, а приналичии единичного сигнала - резервная. Блок 8 можно реализовать на микросхемах постоянных программируемыхЗУ, таких как РТ 4, РТ 5, РТ 7. Сумматор9 предназначен для проверки на четность числа единиц в микрокоманде.При четном числе единиц на выходе 25вырабатывается нулевой сигнал, а вслучае нечетного - единичный. Сумматор 9 можно реализовать, например,на микросхемах ИП 2 или ИП 5. Регистр10 предназначен для приема и храненияинформационной части исправной микрокоманды и подачи ее на выход устройства. Устройство может начать работунезависимо от состояния триггеров 5и 7 и значения сигнала неисправностина выходе 25 сумматора 9,5 10 15 20 25 30 35 40 45 50 Примем, что к моменту времени й, (фиг.1 и 2) из. блока 8 считана исправная основная микрокоманда (по адресу ,с нулевым старшим разрядом), вследствие чего сигнал неисправности Пг 5 имеет нулевое значение, а триггеры 5 и 7 находятся в нулевом состоянии,1309024 4в регистры 3 и 10, и работа устройства продолжается аналогично работе с момента времени 1, с той разницей, что в последующих тактах считываются резервные микрокоманды (по адресам с единичным старшим разрядом) до первой д неисправной микрокоманды, после чего о- считываются основные микрокоманды(по адресам с нулевым старшим разря 10 цом), и т.д. Тогда в момент времени 1 по передне му фронту импульсов Эц считанная основная микрокоманда принимается в ре гистры 3 и 10, так как элемент 2 отк рыт единичным сигналом с нулевого вь хода 18 триггера 5. Информационная часть микрокоманды поступает на выхо 26 устройства, а адресная часть микр команды с выхода 14 регистра 3 посту пает в коммутатор 6, где вырабатывается адрес следующей микрокоманды, который с выхода 19 поступает на адресный вход блока 8. Так как триггер 7 находится в нулевом состоянии, то на его выходе 20 имеется нулевой сиг нал, и в момент времени 1 из блока 8 считывается следующая микрокоманда по адресу с нулевым старшим разрядом и поступает на входы регистров 3 и 10 и сумматора 9. 20Если микрокоманда не искажена, то в момент времени С считывается сле 5дующая микрокоманда, если же микрокоманда искажена, то в момент временина выходе 25 сумматора 9 вырабатывается единичный сигнал неисправности, поступающий на информационный вход триггера 5 и отпирающий элемент 4.Вследствие этого в момент времени С триггеры 5 и 7 устанавливаются в единичное состояние по переднему фронту тактового импульса Э. Элемент 2 запирается нулевым сигналом с нулевого выхода 18 триггера 5, вследствие чего в момент времени е приема искаженной З 5 микрокоманды в регистры 3 и 10 не происходит. Одновременно из блока 8 считывается резервная микрокоманда, так как на выходе 20 триггера 7 имеется единичный сигнал, и к моменту времени й она поступает на выход блока 8.Если повторно считанная резервная микрокоманда не искажена, работа уст" ройства продолжается согласно диаг-.раммам Э, Э Э, Э, . В момент време 45 нина выходе 25 сумматора 9 восстанавливается нулевой сигнал, вновь запирающий элемент 4 и поступающий на информационный вход триггера 5.Тогда в момент времени йв по переднему фронту тактового импульса Эп триггер 5 устанавливается в нулевое состояние, отпирая элемент 2. Триггер 7 остается в прежнем состоянии, благодаря чему сохраняется единичное значение старшего разряда адреса блока 8 на выходе 20, В момент времени й резервная микрокоманда принимается Если повторно считанная резервная микрокоманда тоже искажена, работа устройства продолжается согласно диаграммам Э , Э Э , Эц. В момент времени С изменений не происходит, так как на выходе 25 сумматора 9 сохраняется единичный сигнал. Элемент 4 остается открытым, и в момент временипо переднему фронту тактового импульса Э триггер 7 перебрасывается в нулевое состояние, а триггер 5 состояние не изменяет, вследствие чего элемент 2 остается запертым. Поэтому в момент времениприема искаженной резервной микрокоманды в регистры з и 10 не происходит. Устройство прекращает работу, так как при отказе основной и резервной микрокоманд на выходе 25 сумматора 9 постоянно присутствует единичный сигнал неисправности. Триггер 5 остается в единичном состоянии, а элемент 2 остается запертым, блокируя прием искаженных микрокоманд в регистры 3 и 10Предлагаемое устройство обладает такой же устойчивостью к сбоям, что и известное устройство, так как при сбое основной (резервной) микрокоманды считывается резервная (основная), а основная (резервная) не бракуется. В случае сбоя резервной (основной) микрокоманды опять считывается основ" ная (резервная), т.е. при сбоях микрокоманд предлагаемое устройство, как и известное, не прекращает работу, а обязательно восстанавливается. При этом предлагаемое устройство может продолжать работу и после двух и большего количества сбоев, а известное устройство допускает только по одному сбою при чтении из каждого блока памяти. Кроме того, при отказе ячеек памяти известное устройство теряет дополнительно один такт вхолостую для считывания заведомо искаженной микро- команды.13090246выходом первого элемента И и первыминформационным входом коммутатора,второй информационный вход, управляющий вход и выход которого подключенысоответственно к адресному входу ивходу условий ветвления устройства иадресному входу блока памяти микрокоманд, вход и выход элемента задержкисоединены соответственно с тактовымвходом устройства и первым входомпервого элемента И, второй вход которого подключен к инверсному выходупервого триггера управления, информационный вход и синхровход первоготриггера управления соединены соответственно с выходом сумматора по модулю два и тактовым входом устройства,второй вход и выход второго элементаИ подключены соответственно к тактовому входу устройства и синхровходувторого триггера управления, инверсный выход которого соединен с егоинформационным входом, а прямойвыход второго триггера управления подключен к входу старшего разряда адреса блока памяти микрокоманд. Формула изобретения Микропрограммное устройство управления, содержащее блок памяти микро- команд, регистр адреса, коммутатор, 5 два триггера управления, два элемента И и элемент задержки, о т л и - ч а ю щ е е с я тем, что, с целью сокращения объема оборудования, оно содержит сумматор по модулю два и регистр информации, информационный вход, синхровход и выход которого соединены соответственно с выходом операционного поля блока памяти микрокоманд, выходом первого элемента И и операционным выходом устройства, первый, второй и третий входы и выход сумматора по модулю два подключены соответственно к выходу адресного поля, выходу операционного поля, выходу 20 контрольного разряда блока памяти микрокоманд и первому входу второго элемента И, информационный вход, син-, хровход и выход регистра адреса соеЯ 5 динены соответственно с выходом адрес ного поля блока памяти микрокоманд,Составитель Г.ВиталиевТехред В.Кадар Корректор.А,Тяско ктор Н.Тупиц Заказ 1799/41 Тираж ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Рауш

СмотретьЗаявка

3982256, 02.12.1985

ПРЕДПРИЯТИЕ ПЯ А-7390

САРКИСЯН АКОП ЕРВАНДОВИЧ, ГАЗИЯН ВЛАДИМИР НИКОЛАЕВИЧ, ТАМАЗЯН ГАГИК САМСОНОВИЧ, МАРТИРОСЯН РУБИК КАЧАВАНОВИЧ, МУРАДХАНЯН АРМЕН ЭДУАРДОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.05.1987

Код ссылки

<a href="https://patents.su/4-1309024-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Многоканальное устройство приоритета

Случайный патент: Пусковая гидромуфта