Устройство для вычисления функции двоичной экспоненты

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

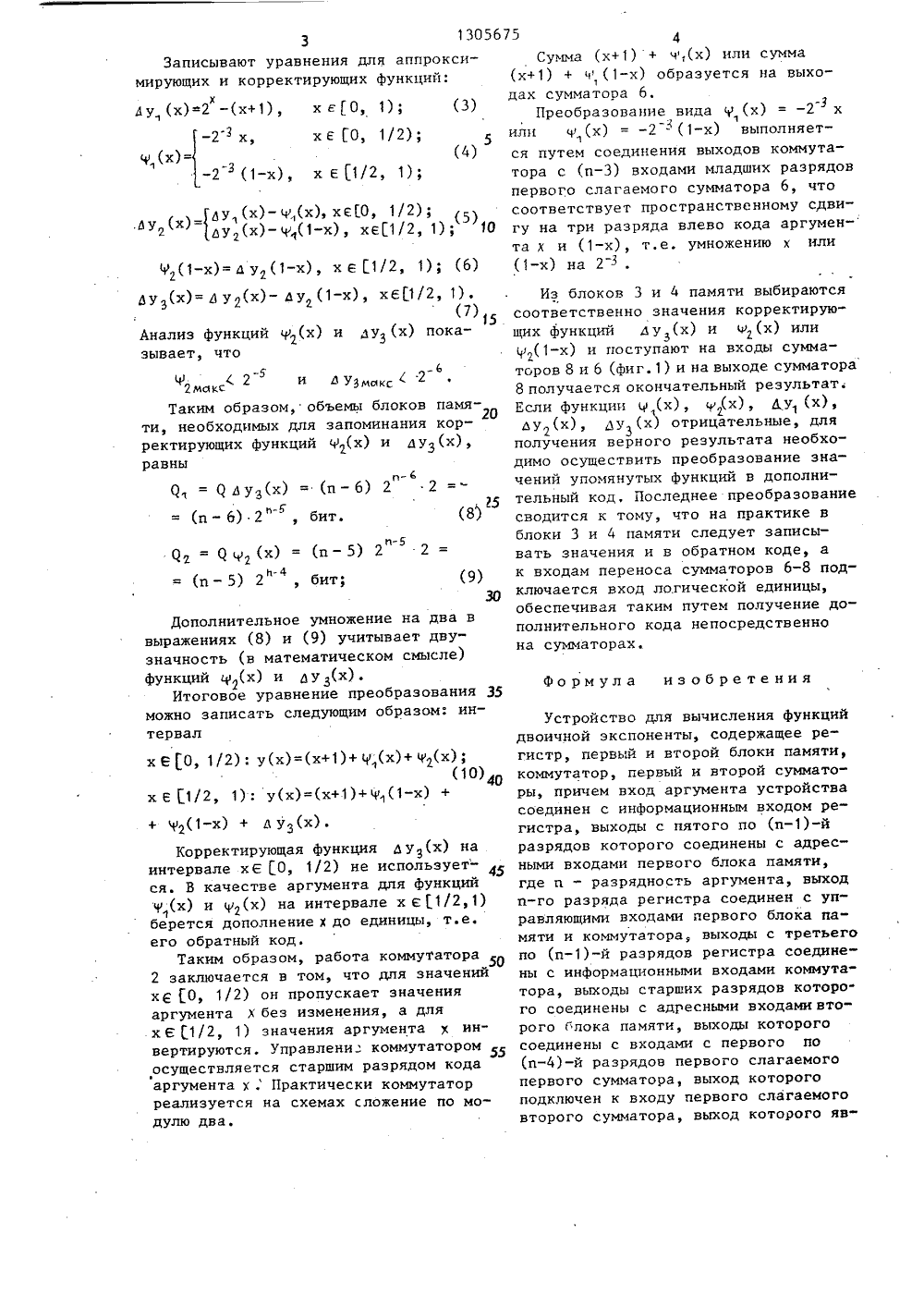

СОЮЗ СОВЕТСНИХСООИАЛИСТИЧЕСНРЕСПУБЛИК 06 Г 7/556 ОПИСАНИЕ ИЗОБРЕТ РСКО ТЕЛЬСТВУ(21) (22) (46) (72) В.Д. (53) (56) итви ов Ю.В. К воп тельных усти потенциистемы и маросу ройс рова шины А И 12(556, 1984 ОСУДАРСТВЕННЦЙ КОМИТЕТ СССР О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ 3974836/24-2405. 11. 8523.04.87. Бюл. ИЮ.В.Хохлов, А.М.Лиделко и С.В.Шант681.325(088.8)Циделко В.Д., Хохлпостроения вычислив логарифмировани 80130567(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ ДВОИЧНОЙ ЭКСПОНЕНТЫ(57) Изобретение касается цифровойвычислительной техники и может бытьиспользовано при построении специализированных вычислителей,. информационно-измерительных систем и цифровых устройств для обработки сигналовЦель изобретения - уменьшение объемапамяти. В состав устройства входятрегистр 1, первый и второй блоки 3и 4 памяти, коммутатор 2, три сумматора 6, 7, 8 и блок 5 злементов НЕ.В данном устройстве уменьшение объема памяти достигается за счет использования кусочно-линейной функции коррекции, аппроксимирующей разность1305675 10 1 у 1 (х)мсье,с2 ф между исходной функцией и ее линейным приближением, а также за счет.использования симметрии функции корИзобретение относится к цифровойвычислительной технике и может быть использовано при построении специализированных вычислителей, цифровыхустройств для обработки сигналов, гибридных функциональных преобразователей и информационно-измерительныхсистем, при восстановлении и сжатиисигналов, при цифровой нелинейной обработке звуковых и видеосигналов вустройствах реального времени,Цель изобретения - уменьшение объема памяти.На фиг.1 приведена структурнаясхема устройства для вычисления функции двоичной экспоненты; на фиг.2 -эпюры, поясняющие принцип преобразования.Устройство для вычисления функциидвоичной экспоненты содержит регистр1, коммутатор 2, первый и второй блоки 3 и 4 памяти, блок 5 элементов НЕ,третий, первый и второй сумматоры6-8, входы 9 и 10 логических нуля иединицы.Работа устройства для вычисленияфункции двоичной экспоненты у = 2где х Е ГО; 1) (в дальнейшем . - исходной функции), основана на кусочнолинейной аппроксимации этой функциис последующей коррекцией разности,называемой функцией коррекции, междуисходной функцией и ее линейным приближением,На фиг.2 о показана аппроксимация функции у = 2", х 6 0, 1) прямой линией, откуда видно, что входной кодсодержит часть информации о выходной величинеи может использоваться как грубое приближение исходной функции, Разность между исходной Функцией и ее линейным приближением ау (х)=2 . - (х + 1) показана на фиг.2 Б. Анализ функции у (х) показывает, что рекции, устранения двузначности функции коррекции и введения второго канала коррекции, 2 ил,Построим функцию ,(х), котораяявляется кусочно-линейной аппроксимацией функции разности Л у(х) на интервалах х Е 0, 1/2) и х Е.1/2, 1), 5 таким образом, чтобы-3кода аргумента х на коэффициент -2соответствует операции сдвига на триразряда влево и не представляет трудностей при практической реализации,а вычисление(х) на интервале11/2, 1) может выполняться аналогично, если в качестве аргумента братьдополнение у до 1, т.е. обратныйход Х, что возможно вследствие сим метрии функции ч(х) .Разность между Функциями д у(х)и Ч (х); ау 2(х) = ду (х) -(х) показана на фиг.2 б. Построим Фуйкцию(х), которая является симметричным отображением Функции ду(х) длязначений х е О, 1/2) относительнооси, проведенной через точку х = 1/2(фиг.2 б, пунктир).Значения функции М (х) на интервале 0, 1/2) рассчитывается заранее ипомещаются во второй блок памяти.Очевидно, что для получения функцииЧ (х) на интервале х е 1/2, 1) необходимо брать дополнение аргумента до 40 1. Вследствие построенной симметриифункция ф (х) совпадает с функцией2ду (х) на интервале х е СО, 1/2).функция разности Ьу (х) = Йу 2(х) -3Ф 2(х) (фиг.2 б), значения которой 45 запоминаются в первом блоке памятии служат для получения точного результата преобразования на интервалех Е Г 1/г, 1).(х) = 3 13056Записывают уравнения для аппроксимирующих и корректирующих функций: ду (х)2 -(х+1), х е 0, 1); (3)(ду 2(х) - Ч,(1-х), хе 1/2, 1); 10 М 2(1-х) = д у 2 (1-х), х Е Г 1/2, 1); (б) дуЗ(х)= д у 2(х) - ду (1-х), хам/2, 1).15 Анализ функции ц 2 х и дуЗ х пока зывает, что42 сС 2 и д У 3 мокс с 26Таким образом, объемы блоков памя 20 ти, необходимых для запоминания корректирующих функций М (х) и ду 3(х), равныи-Я, = й дУ,(х) = (и) 2(и - 5) 2, бит; (9)30 Дополнительное умножение на два в выражениях (8) и (9) учитывает двузначность (в математическом смысле) функций с (х) и дуз(х),Итоговое уравнение преобразования 35 можно записать следующим образом: ин- тервал х б 0, 1/2): у(х) =(х+1)+ (х)+ М 2(х) 3+ у 2(1-х) + дуЗ(х)Корректирующая функция дуз(х) на интервале хЕ 0, 1/2) не использует ся. В качестве аргумента для функций Ч (х) и 2(х) на интервале х е 1/2, 1) берется дополнение Х до единицы, т.е. его обратный код.Таким образом, работа коммутатора 2 заключается в том, что для значений хЕ 0, 1/2) он пропускает значения аргумента Х без изменения, а для х Е 1/2, 1) значения аргумента х инвертируются. Управлени коммутатором 55 осуществляется старшим разрядом кодааргумента х . Практически коммутаторреализуется на схемах сложение по модулю два. 754Сумма (х+1) + ч,(х) или сумма (х+1) + ч (1-х) образуется на выхо 1дах сумматора 6.Преобразование вида у (х) = -2 х или ч (х) = -2 - (1-х) выполняется путем соединения выходов коммутатора с (и) входами младших разрядов первого слагаемого сумматора 6, что соответствует пространственному сдвигу на три разряда влево кода аргумен- та х и (1-х), т,е. умножению х или (1-х) на 2. Из блоков 3 и 4 памяти выбираются соответственно значения корректирующих функций ду (х) и ц (х) или 2(1-х) и поступают на входы сумматоров 8 и б (фиг.1) и на выходе сумматора 8 получается окончательный результат. Если функции (х), 2(х), Ау 1 (х), ду 2(х) ду (х) отрицательные для получения верного результата необходимо осуществить преобразование значений упомянутых функций в дополнительный код, Последнее преобразование сводится к тому, что на практике в блоки 3 и 4 памяти следует записывать значения и в обратном коде, а к входам переноса сумматоров 6-8 подключается вход логической единицы, обеспечивая таким путем получение дополнительного кода непосредственно на сумматорах. формула изобретения Устройство для вычисления функций двоичной экспоненты, содержащее регистр, первый и второй блоки памяти, коммутатор, первый и второй сумматоры, причем вход аргумента устройства соединен с информационным входом регистра, выходы с пятого по (и)-й разрядов которого соединены с адресными входами первого блока памяти, где и - разрядность аргумента, выход и-го разряда регистра соединен с управляющими входами первого блока памяти и коммутатора, выходы с третьего по (и)-й разрядов регистра соединены с информационными входами коммутатора, выходы старших разрядов которо. го соединены с адресными входами второго блока памяти, выходы которого соединены с входами с первого по (и)-й разрядов первого слагаемого первого сумматора, выход которого подключен к входу первого слагаемого второго сумматора, выход которого яв1305675 у уф к ю (х)фиг Р оставитель А.Нуляехред Л.Олейник в Корректор А.Обручар акто огулич Заказ 1452/ б 73 Тираж ВНИИПИ Госуда по делам и 113035, Москвдписноеа СССР ственного коми обретений и от , Ж, Раушск тий набд 4/5 роизводстве полиграфическое предприятие, г.ужгород, ул,Проектна 5ляется выходом результата устройства, выходы первого блока памяти соединены с входами с первого по (и)-й разрядов второго слагаемого второго сумматора, входы переносов первого и второго сумматоров подключены к входу логической единицы устройства, вход логического нуля которого подключен к входам четырех старших разрядов первого слагаемого первого сумматора 10 и к входам пяти старших разрядов второго слагаемого второго сумматора, о т л и ч а ю ш е е с я тем, что, с целью уменьшения объема памяти, в него введены третий сумматор и блок 15 6элементов НЕ, входы которого пораз-рядно подключены к выходам коммутатора, выходы блока элементов НЕ соединены с входами с первого по (и)-й разрядов первого слагаемого третьего сумматора, выход которого соединен с входом второго слагаемого первого сумматора, выход регистра соединен с входом второго слагаемого третьего сумматора, вход переноса которого соединен с входом логической единицы устройства, входы трех старших разрядов первого слагаемого третьего сумматора подключены к входу логического нуля устройства.

СмотретьЗаявка

3974836, 05.11.1985

КОНСТРУКТОРСКОЕ БЮРО "ШТОРМ" ПРИ КИЕВСКОМ ПОЛИТЕХНИЧЕСКОМ ИНСТИТУТЕ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ХОХЛОВ ЮРИЙ ВИКТОРОВИЧ, ЛИТВИН АЛЕКСАНДР МИХАЙЛОВИЧ, ЦИДЕЛКО ВЛАДИСЛАВ ДМИТРИЕВИЧ, ШАНТЫРЬ СЕРГЕЙ ВАЛЕРЬЕВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, двоичной, функции, экспоненты

Опубликовано: 23.04.1987

Код ссылки

<a href="https://patents.su/4-1305675-ustrojjstvo-dlya-vychisleniya-funkcii-dvoichnojj-ehksponenty.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции двоичной экспоненты</a>

Предыдущий патент: Устройство для вычисления модуля комплексного числа

Следующий патент: Управляемый датчик случайных чисел

Случайный патент: Шарошечное долото для планетарного бурения