Преобразователь балансно-модулированных сигналов переменного тока в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

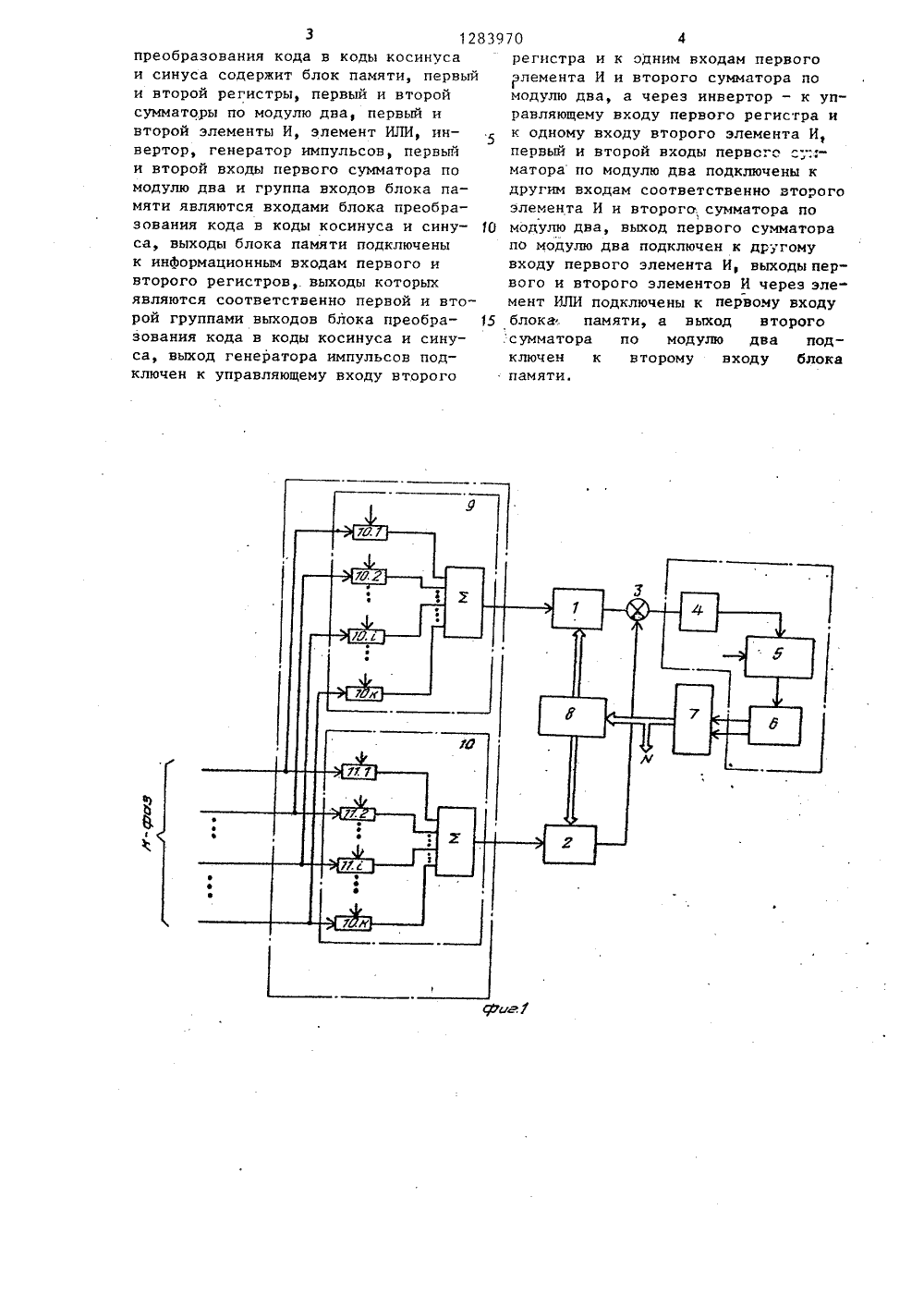

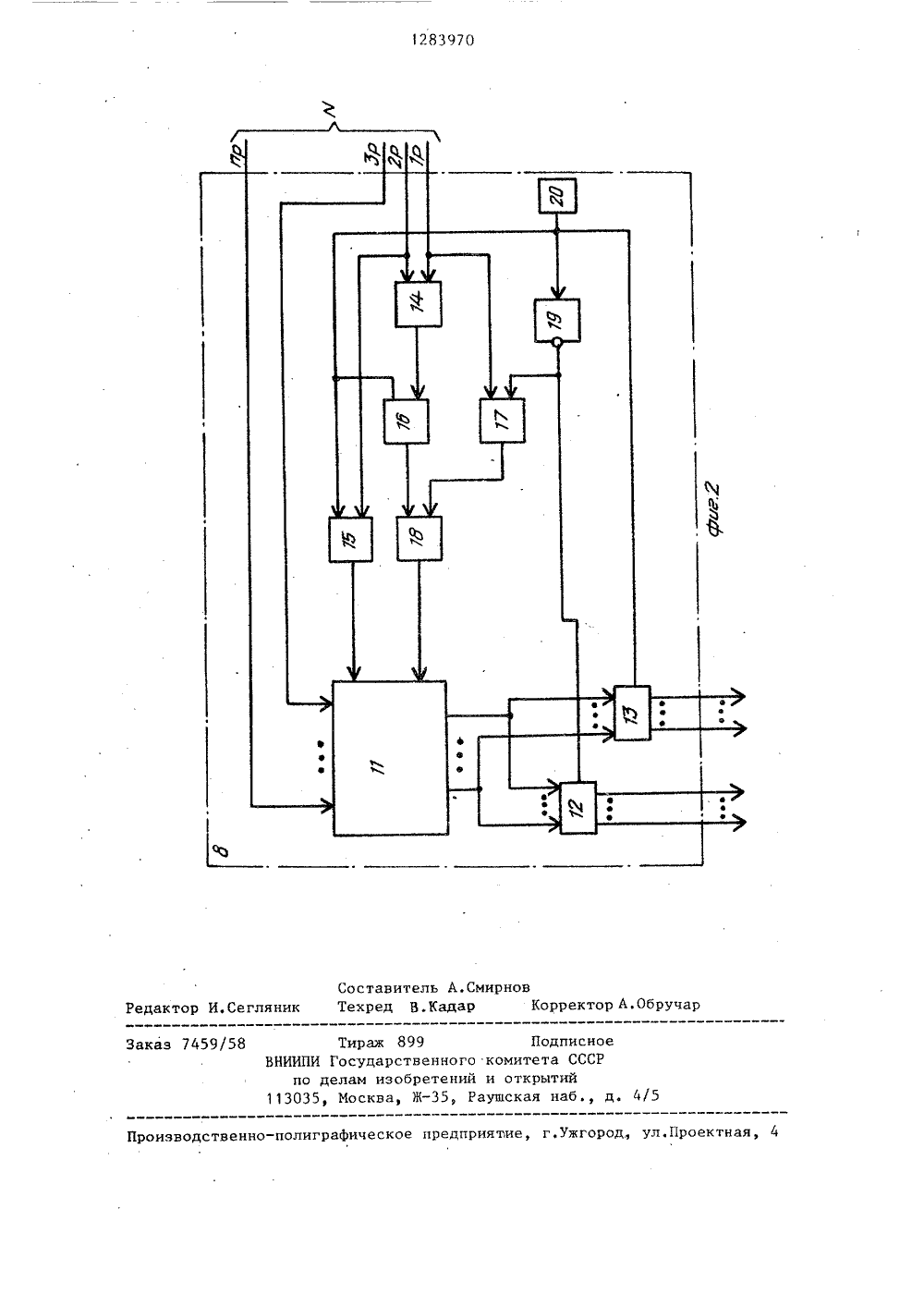

,ЯО 128397 51)4 Н 03 48 ОПИСАНИЕ ИЗОБРЕТЕНК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССР У 1088045, кл. С 08 С 9/00, 1983,Авторское свидетельство СССР В 1123043, кл. С 08 С 9/00, 1983. (54) 11 РЕОБРАЗОВАТЕЛЬ БАЛАНСНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ПЕРЕМЕННОГО ТОКА В КОД(57) Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью упрощения преобразователя путем уменьшения числа аналого-цифровых умножителей н преобразователь, соДержащий первый и второй аналогоцифровые умножители, первый сумматор, усилитель, фаэочувствительный выпрямитель, регулятор частоты, реверсивныи счетчик и блок преобразования кода в коды косинуса и синуса, введены второй и третий сумматоры. Входные балансно-модулированные сигналы преобразователя суммируются друг с другом во втором и третьем аналоговых сумматорах с весовыми коэффициентами, пропорциональными косинусной зависимости для второго сумматора и синусной зависимости для третьего сумматора. На выходах второго и третьего сумматоров формируются сигналы переменного тока, модулированные в Функции синуса и косинуса соответственно, которые в аналого-цифровых умножителях умножаются на коды коси-нуса и синуса выходного кода М преобразователя. На выходе первого сумматора формируется сигнал переменного Св тока, амплитуда которого пропорциональна рассогласованию между параметром ои его кодовым эквивалентом И. Код И реверсивного счетчика изменяется до устранения рассогласования между о и И. 1 з.п. Ф-лы, 2 ил.83970 2 цифровых умножителей ственно, В сумматоре 3 напряжение П разности налов аналого-цифровых 1 и 2 и 2 соответформируется выходньгх сигумножителей 1 12Изобретение относится к автоматике и вычислительной технике и можетбыть использовано для связи аналоговых источников информации с цифровымвычислительным устройством.. Цель изобретения - упрощение преобразователя путем уменьшения числааналого-цифровых умножителей,На фиг.1 приведена структурнаясхема преобразователя; на фиг,2 -структурная схема блока преобразования кода в коды косинуса и синуса..Преобразователь балансно-модулированных сигналов переменного токав код (фиг.1) содержит первый 1 ивторой 2 аналого-цифровые умножители,первый сумматор 3, усилитель 4, фазочувствительный выпрямитель 5, регулятор б частоты, реверсивный счетчик7, блок 8 преобрйзоцания кода в кодыкосинуса и синуса, второй 9 и третий10 сумматоры.Блок 8 преобразования кода в кодыкосинуса и синуса (фиг,2) содержитблок 11 памяти, первый 12 и второй 13регистры, первый 14 и второй 15 сумматоры по модулю два, первый 16 ивторой 17 элементы И, элемент ИЛИ 18,инвертор 19, генератор 20 импульсов.Преобразователь работает следующимобразом.На вход преобразователя поступаетК балансно-модулированных сигналовпеременного тока вида11. =Пвз.псЕ + - (1-1) 127 где1,2,К - номер сигнала;1=Пвпа)г, - опорное напряжение.В сумматоре 9 производится суммирование входных сигналов преобразователя с весовыми коэффициентами2 Ксов в (-1) для каждого -го каналаКсоответственно. В сумматоре 10 входные сигналы преобразователя суммируются с весовыми коэффициентами2 Хв.пр-(х) для каждого ь-го канала. На выходе сумматоров 9 и 10 формируются сигналыК КП 9 Пп е 1 по0 Уп совс которые поступают на аналоговые входь аналого-цифровых умножителей 1 и 2 соответственно.В блоке 8 из кода И реверсивного счетчика 7 формируются коды, пропорциональные совМ и зпИ, которые поступают на цифровые входы аналогоК-вп(- - И) .3 п 2В фазочувствительном выпрямителе 5из сигнала П выделяется постояннаяэсоставляющая, в зависимости от амплитуды и знака которой регулятор б вырабатывает импульсы определеннойчастоты по одному иэ выходов. Код Бв реверсивном счетчике 7 изменяется 15 до устранения рассогласования междуи Б. Формула изобретения 20 1Преобразователь балансно-модулированных сигналов переменного токав код, содержащий первый и второйаналого .цифровые умножители, цифровые входы которых соединены соответ ственно с первой и второй группамивыходов блока преобразования кодав коды косинуса и синуса, а выходыподключены к входам первого сумматора, выход первого сумматора через 30 усилитель подключен к одному входуфазочувствительного выпрямителя, другой вход которого соединен с источником опорного напряжения, а выходподключен к входу регулятора частоты, 35 выходы регулятора частоты подключенык входам сложения и вычитания реверсивного счетчика соответственно, выходы разрядов реверсивного счетчикаявляются выходами преобразователя и 40 подключены к входам блока преобразования кода в коды косинуса и синуса,о т л и ч а ю щ и й с я тем, что,с целью упрощения преобразователя,в него введены второй и третий сум маторы, входы которых являются входами преобразователя, а выходы подключены к аналоговым входам первогои второго аналого-цифровьгх умножителей соответственно причем коэффи циенты передачи второго и третьегосумматоров выбраны в соответствии27с косинусной соз(х) и синусной к23зп в (1-1) зависимостями, где 1=55 . к3 12839 преобразования кода в коды косинуса и синуса содержит блок памяти, первый и второй регистры, первый и второй сумматоры по модулю дна, первый и второй элементы И, элемент ИЛИ, инвертор, генератор импульсов, первый и второй входы первого сумматора по модулю два и группа входов блока памяти являются входами блока преобразования кода в коды косинуса и сину- О са, выходы блока памяти подключены к инйормационным входам первого и второго регистров,. выходы которых являются соответственно первой и второй группами выходов блока преобра зования кода в коды косинуса и синуса, выход генератора импульсов подключен к управляющему входу второго о 4регистра и к одним входам первогоэлемента И и второго сумматора ломодулю два, а через нннертор - к управляющему входу первого регистра ик одному входу второго элемента И,первый и второй входы пернсгоматора по модулю дна подключены кдругим входам соответственно второгоэлемента И н второго, сумматора помодулю два, выход первого сумматорапо модулю два подключен к другомувходу первого элемента И, выходь 1 первого и второго элементов И через зле"мент ИЛИ подключены к первому входублока. памяти, а выход второго.сумматора по модулю два подключен к второму входу блокапамяти.1283970 Составитель А Техред В.Кад ирнов Корректор А.Обр едактор И,Сегляник аказ 7459/5 Производственно-полиграфическое предприятие, г.ужг ул,Проектна Тираж 899 ВНИИПИ Государственного к по делам изобретений и 1 1 3035 у Москва) Ж 35 р Рауш

СмотретьЗаявка

3921119, 26.06.1985

ПРЕДПРИЯТИЕ ПЯ А-3327

ГОЛОПЯТОВ ВЯЧЕСЛАВ ФЕДОРОВИЧ, ЧЕБОТАЕВ ОЛЕГ ЕГОРОВИЧ

МПК / Метки

МПК: H03M 1/48

Метки: балансно-модулированных, код, переменного, сигналов

Опубликовано: 15.01.1987

Код ссылки

<a href="https://patents.su/4-1283970-preobrazovatel-balansno-modulirovannykh-signalov-peremennogo-toka-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь балансно-модулированных сигналов переменного тока в код</a>

Предыдущий патент: Двухотсчетный преобразователь синусно-косинусно модулированных сигналов переменного тока в код

Следующий патент: Следящий аналого-цифровой преобразователь

Случайный патент: Патентно. f. rfxkhifcila: • библиотека