Устройство для приема и градиентного декодирования избыточных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

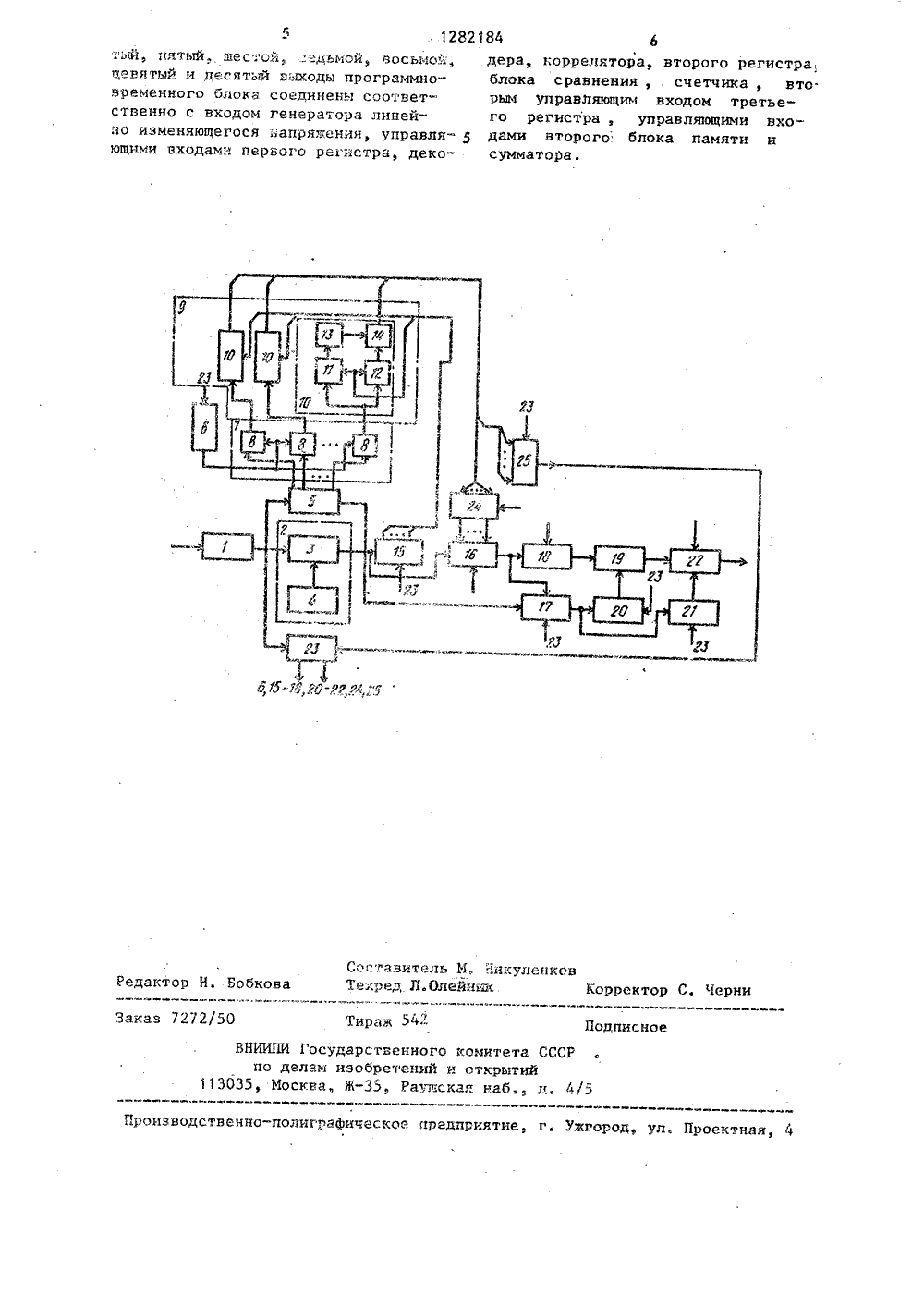

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ЕНИЯ с ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ ПИСАНИЕ ИЗО ВТСРСЙОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССРВ 824263, кл, С 08 С 19/28, 1979.Авторское свидетельство СССРМ 1152020, кл. С 08 С 19/28, 1983.(54) УСТРОЙСТВО ДПЯ ПРИЕМА И ГРАДИЕНТНОГО ДЕКОДИРОВАНИЯ ИЗБЫТОЧНЫХСИГНАЛОВ,(57) Изобретение относится к радиотехнике и электросвязи и может использоваться в системах передачи ди кретных сигналов, использующих коды большой мощности. Изобретение позволяет упростить устройство, Устройство осуществляет прием избыточных сигналов в целом, декодирование кодо вой комбинации и выдачу декодированной комбинации, наиболее близкой к входному сигналу. Устройство содержит приемник, пороговый блок, блоки памяти, генератор линейно изменяющегося напряжения, компараторы, инвер" торы, регистры, декодер, коррелятор, ,ключ, .блок сравнения, счетчик и сумматор. 1 ил.Изобретение относится к радиотехнике и электросвязи и мажет использоваться в системах передачи дискрет.най информации для приема избыточныхсигналов в целом, использующих кодыбольшой мощности.Цель изобретения - упрощение устройства.На чертеже приведена структурнаясхема устройства,10Устройство для приема и градиентного декодирования избыточных сигналов содержит приемник 1 (аналоговыйдемодулятор), пороговый блок 2, состоящий из элемента 3 сравнения и источника 4 опорного напряжения, первыйбуферный блок 5 памяти, генератор блинейно изменяющегося напряжения,блок 7 компараторов, состоящий изкомпараторов 8, логический блок 9,состоящий из управляемых инверторов10, каждый иэ которых состоит из ключей 11 и 12, элемента НЕ 13 и элемента ИЛИ 14, первый регистр 15 сдвига,декодер 16, коррелятор 17, второй25регистр 18 сдвига, ключ 19, блок 20сравнения, двоичный счетчик 21, третий регистр 22 сдвига, программновременной блок 23, второй буферныйблок 24 памяти и сумматор 25.Устройство работает следующимобразом.На вход устройства поступает из канала связи составной сигнал с избыточностью, который обрабатывается в аналоговом демодуляторе 1. На выходе последнего формируется йналоговый составной избыточный сигнал, в котором элементарным сигналом является импульс постоянного тока соответствующей амплитуды, Импульсы постоянного тока запоминаются в блоке 5 памяти, а также подаются на вход программно-временного блока 23 и на вход порогового блока 2 - на первый вход элемента 3 сравнения, на другой вход которого подается напряжение от источника 4 порогового напряжения, При превышении Аналоговым сигналом порогового напряжения на выходе блока 2 формируется единичный сигнал, в противном случае - нулевой сигнал,Совокупность двоичных сигналов на выходе блока 2 соответствует двоичной кодовой комбинации, являющейся грубой оценкой избыточного сигнала. Эта двоичная комбинация запоминается в регистре 15, а также поступает на вход декодера 16.В декодере 16 входная комбинация отождествляется с ближайшей разрешенной кодовой комбинацией, которую декодер 16 записывает в регистр 18 и коррелятор 17. На другой вход коррелятора 17 из блока 5 памяти (по сигналу блока 25) подается аналогогый составной сигнал - точная оценка избыточного сигнала. Коррелятор 17 вычисляет степень близости двоичной комбинации к аналоговому сигналу,В случае, если коэффициент корреляции больше предыдущего коэффициента корреляции (в данном случае это "0"), то кодовая комбчнация из регистра 18 через ключ 19, открывающийся по сигналу блока 20 сравнения, поступает в регистр 22, где запоминается. Если коэффициент корреляции меньше предыдущего коэффициента, то на выходе блока 20 сравнения управляющий сигнал не формируется, ключ 19 не открывается и комбинация остается в регистре 18, где на следующем такте заменяется на очередную комбинацию.Информация иэ блока 5 памяти может считываться многократно. С параллельных выходов блока 5 памяти аналоговые сигналы на компараторы 8 блока 7, На другие входы компараторов 8 от генератора 6 (который запускается импульсом, вырабатываемым в блоке 23, пока импульс есть, генератор 6 Функционирует) подается сигнал, напряжение которого изменяется по линейному закону. С помощью компараторов 8 Фиксируются моменты совпадения входных сигналов. В эти моменты времени на выходах соответствующих компараторов 8 формируются управляющие сигналы. Эти сигналы подаются на входы соответствующих инверторов 10, на другие входы которых поступают сигналы с параллельных выходов регисра 15. Выходной управляющий сигнал компаратора поступает на управляющие входы ключей 11 и 12, При наличии управляющего сигнала открывается ключ 1 1, а при отсутствии - ключ 12. В случае, когда ключ 11 открыт, выходной двоичный сигнал соответствующей ячейки памяти регистра 15 проходит ключ 11, инвертируется в помощью элемента НЕ 13 в противоположный дво1282184 Техническое преимущество устройства по сравнению с известным заключается в исключении из схемы известного части блоков, снижающих его надежность, т.е. в упрощении устройства. ичный сигнал и через элемент ИЛИ 14записывается в соответствующую ячейку памяти блока 24. Если открыт ключ12, то. соответствующий двоичный сигнал записывается в определенную ячейку памяти регистра блока 24 без изменения. Каждое срабатывание компараторов блока 7 фиксируется суммато- Формула из обре те ния ром 25 и подается в блок 23, в котором формируется управляющий сигнал и 10 Устройство для приема и градиент- сформированная на выходах блока 9 ного декодирования избыточных сигдвоичная кодовая комбинация перепи- налов, содержащее приемник, вход косывается в блоке 24 из первого парал- торого является входом устройства, лельного. буферного регистра во вто- выход приемника соединен с входами рой, потом в третий и т.д, Количество 15 первоо блока памяти и порогового регистров в блоке 24 определяется блока, выход порогового блока соедискоростью обработки информации уст- нен с информационным входом первого ройством, быстродействием элементов регистра и первым информационным и т.п. По мере появления управляющих входом декодера выходы первого ресигналов на выходах блока 7 двоичные 20 гистра соединены с информационными комбинации продвигаются по регистрам входами соответствующих инверторов, блока 24 и.в определенный момент вре- управляющие входы которых подключены мени (он определяется количеством к выходам соответствующих компаратосработавших компараторов 8 блока 7 ров, выход декодера соединен с инфори емкостью блока 24 памяти) на выхо мационным входом второго регистра и дах блока 24 появляется двоичная ко- первым информационным входом корредовая комбинация, Эта комбинация по" лятора, второй информационный вход дается на входы декодера 16, в кото- коррелятора подключен к первому выром преобразуется в ближайшую разре- ходу первого блока памяти, выход щенную кодовую комбинацию. Данная З 0 коррелятора соединен с информационразрешающая кодовая комбинация запи- ными входами блока сравнения и счетсывается в регистр 18, поступает на чика, выход блока сравнения и выход вход коррелятора 17 и обрабатывается второго регистра соединены соответв соответствии с описанным алгорит- ственно с управляющими н и фи н информацимом,Если для нее коэффициент корреля- онными входами ключа выход35выход ключа и ции больше коэффициента корреляции выход счетчика соединены соответстпредыдушей комбинации,то она записы- венно с информационным и первым упвается в регистр 22,в противном слу- равляющим входами третьего регистра, чае остается в регистре 18. выход которого является выходом устройства, программно-временной блокАналогичным образом обрабатываютсяУвторой блок памяти и генератор линейвсе двоичные комбинации с выхода бло- но изменяющегося напряжения, о т л ика 2 памятна ч а ю щ е е с я тем, что, с цельюКогда выходное напряжение генера- упрощения устройства, в негр введен тора 6 достигает своего мак ио го максимального сумматор, вторые выходы первого блоэначения, снимается уп авляю ий сиг-упр вляющий сиг. ка памяти соединены с первыми входанал блока 23, включая гене атоя генератор 6. ми соответствующих компараторов, выПри посту еход генератора линейно изменяющегосяри поступлении на вход корреля"тора 17 й бнапряжения соединен с вторыми входамипоследней комбинации а эна компараторов, выходыинверторов соедичит и на вход счетчика 21, в котором 50 иены соответиены соответственно с информационными подсчитывается количество выходны 1 с входами сумматора и второго блока памяком инации детектора 16) счетчик 21,выдает сигнал, по которому кодоваяти, выходы второго блока памяти соединены с соответствующими вторыми инфоркомбинация из регистра 22 поступаетмационными входамидекодера, выхо на выход устройства. После этого все 5д Р ф дсумматора соединен с первым входом блоки устройства приводятся в исход- программно-временного блока второй4У ное состояние но управляющему сигна- вход которого подключен к выходу приемлу программно-временного блока 23, ника, первый, второй, третий, четвер.каз 7272 иитета Сткрытий ВНИИПИ Государств по делам изобре13035, Москва Ж,ений и аущская Ряба и Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектна тый, пятый. шестой, =.дьмай восьмс;,девятью и десятый выходы программновременного блока соединены соответственно с входом генератора линейно изменяющегося напряжения, управляющими входамн первого регистра, декодера, коррелятора, второго регистра,блока сравнения, счетчика, вто.рым управляющим входом третьего регистра, управляющими входами второго блока памяти исумматора.

СмотретьЗаявка

3925028, 08.07.1985

ПРЕДПРИЯТИЕ ПЯ Г-4190

ЕФИМОВ ЕВГЕНИЙ АЛЕКСЕЕВИЧ, ЗУБКОВ ЮРИЙ ПЕТРОВИЧ, КЛЮЧКО ВЛАДИМИР ИГНАТЬЕВИЧ, НИКОЛАЕВ ЮРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G08C 19/28

Метки: градиентного, декодирования, избыточных, приема, сигналов

Опубликовано: 07.01.1987

Код ссылки

<a href="https://patents.su/4-1282184-ustrojjstvo-dlya-priema-i-gradientnogo-dekodirovaniya-izbytochnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для приема и градиентного декодирования избыточных сигналов</a>

Предыдущий патент: Устройство для передачи и приема сигналов

Следующий патент: Адаптивный передатчик телеметрической информации

Случайный патент: Механизм управления диафрагмой вулканизатора