Ттл-инвертор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

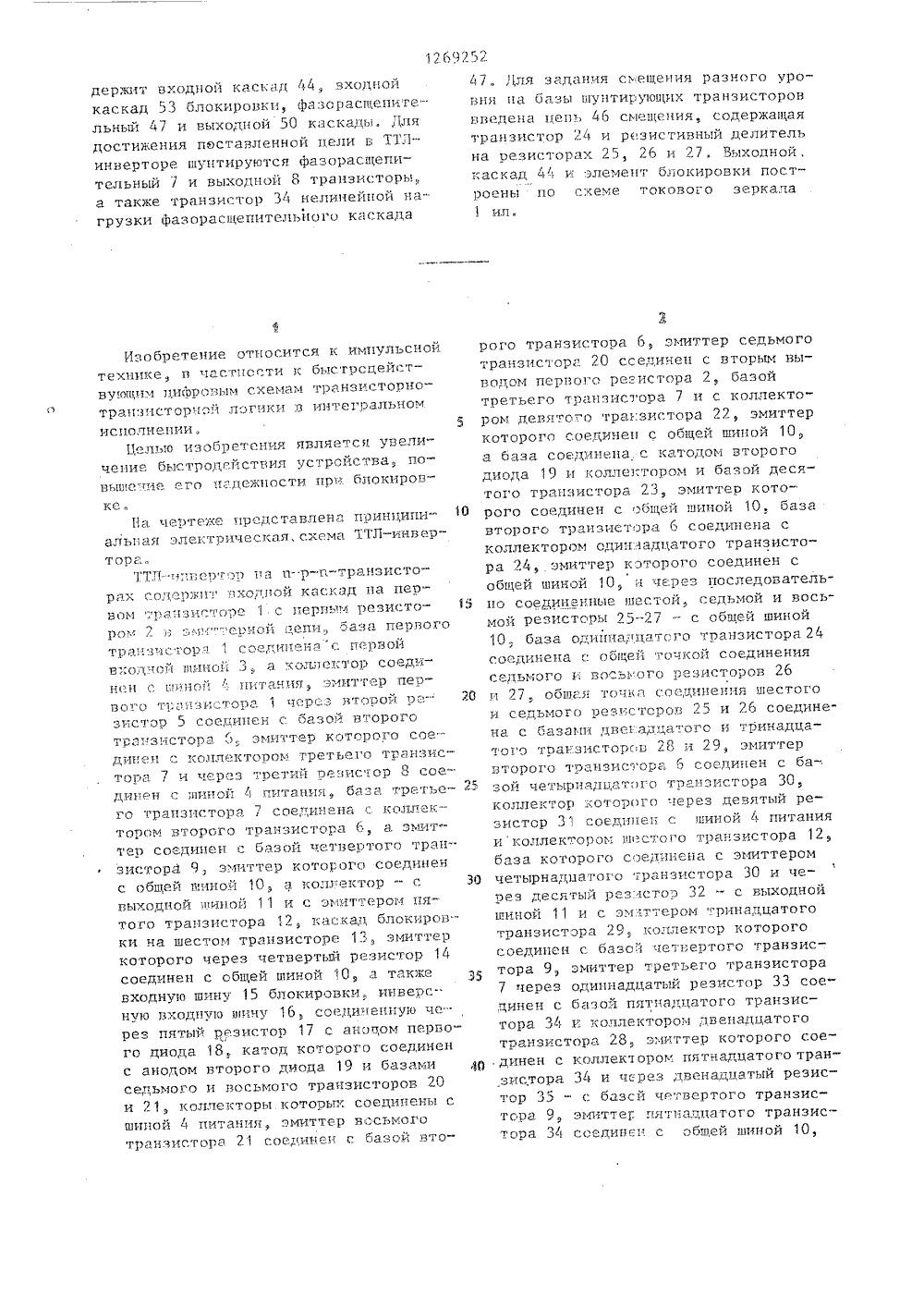

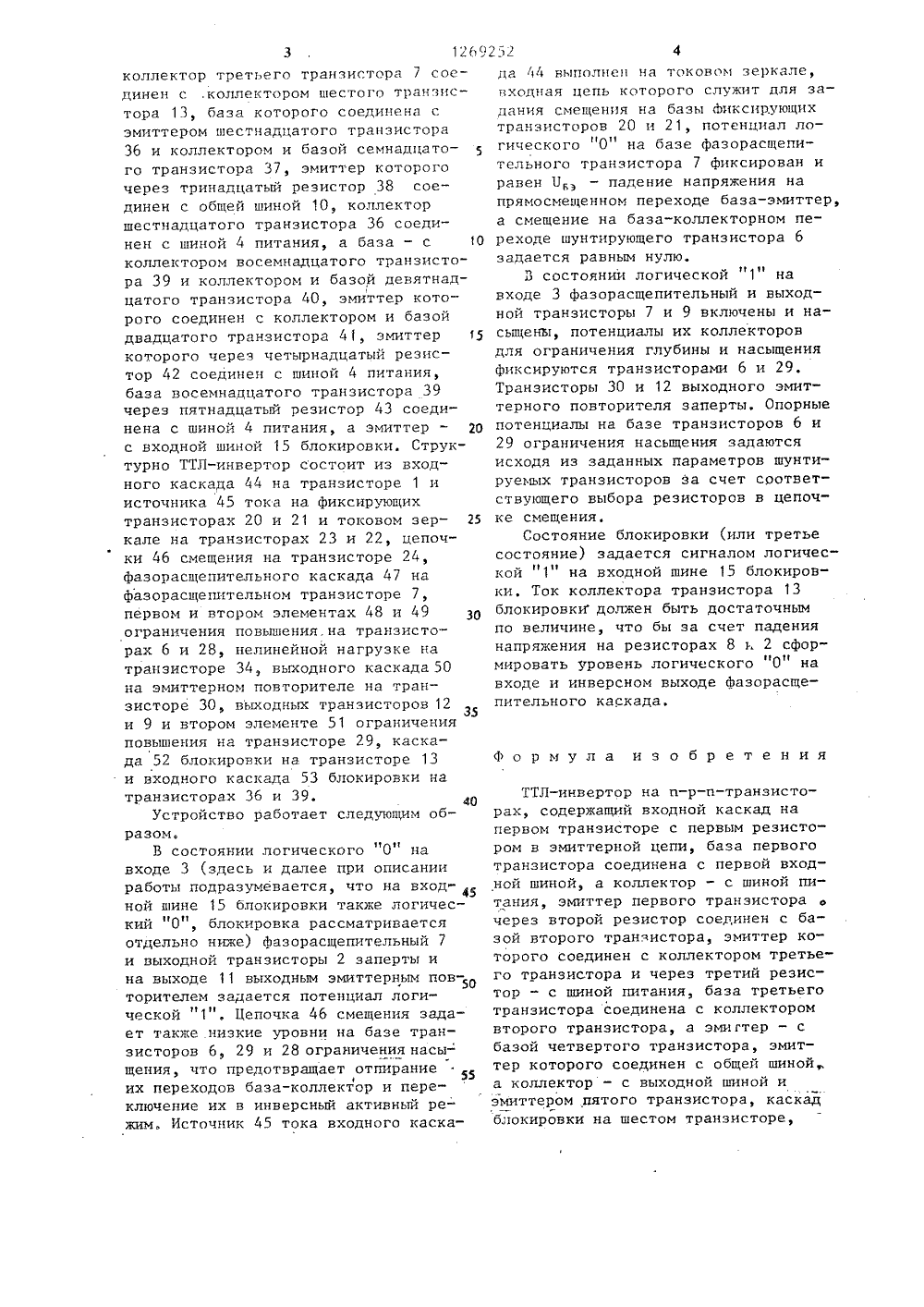

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК К 190 50 ПИСАНИ БРЕТЕ ЪИЬ,. ТЕЛЬСТВУ ой электро тченко,и Ю,П,Родиогральные ми здат, 198 00,УДАРСТВЕННЫЙ КОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Агаханян Т,М. Интеросхемы. М,: ЭнергоатомиПатент США Мф 4.376.9кл. Н 03 К 19/082, 1983(57) Изобретение относится к вычислительной технике, в частности к быстродействующим цифровым схемам транзисторно-транзисторной логики (ТТЛ)в интегральном исполнении, Цель изобретения - увеличение быстродействия.ТТЛ-инвертор со сложным выходным каскадом без диодов Шоттки с ограничением насыщения с помощью транзисторов,шунтирующих своей эмиттерно-коллекторной цепью база - коллекторные переходы переключательных транзисторов, со16 9 гдержит входной каскад 44, входнойкаскад 53 блокировки, фязорасп 1 епительный 47 и выходной 50 каскады. Длядостижения пеставленной пели в 11:,1-.инверторе шуцтируются т 17 азорасщепительный 7 и выходной 8 транзисторы,а также транзистор 34 нелинейной кагрузки Фазорасщепительного каскада Изобретение относится к импульсной техц 1 тсе, в частттости к бьтстрсдействутлщи л писурЯв 11 м схемам трякзисторно- тРаЦЗИСтОРЦОЙ ЛОГИКИ В ИцтЕГГтЯЛЬЦОМ ИСПО,т 1 НЕПИИ, 5Целт,ю изобретения является увеличение быстродействия устро 1 тства, повышеие его надежности при блокиротзко11 я чертеже цредставпеня принципи О аль 11 ая электричест",яя, схема 7.ТП-инвеутор;:П".тт 1 ПС 117 ГУ 7 та П"17-П.-ТРЯИЗИСТО"РЯХ СОДРжит ВХО,;тЦОЙ КЯС.КЯД т 1 а ПЕРвом г 17 Я;1 зисто 17 е 1 с 1 те 17 Г 1.тл резисторОМ., Этят.-.С 17 НО 1 т. тЕПт 1 баэа ПЕВВОГОтряцэттСТОря 1 Гоадццтвтзя С ттцрВОЙвходной итицой 1 3 Я кол 7 зтстор соедиН.и С 1;ИНОЙ ". ЦИтяццц, ЭМИттЕР ПЕтрвОГО ГГуяцзистО 17 Я 1 чер3 втовои т 7 е зистор 5 соет(1 лцек Г. базой. второго тряттзтлстора 6 эмиттер кото 1701 О сое динецколлектором третьего транзистора 7 и через третий резистор 8 сое 7диен с шицоц 4 Гтитания, бгзя трслтье - тТРЯЦЗИСТОРЯ ; СОЕттИНЕЦЯ С КСЛЛЕ 1 - тотртзм вто 17 ГГО трянзистОул 6 я. эмлт- тео соединен с базой четвертого транзистора 9, э 1 иттер которого соединен с общей Бьинои 10, а кол 7 ектор - с 30 Быхоцной тлцоЙ 11 и с эмиттеуом:пя то.со транзистора ",2 каскап, блокировки ца шестом транзисторе 13, эмиттеу которого через четвертый резистор соединен с общей шиной 10, я также входную шину 15 блокировки., инвеус." ную входную шину 16, соединенную че рез пятый резистор 17 с анодом первого диода 18 т, катод которого соединен с акодом второго диода 19 и базами 40 седьмого и восьмого трянзисторог 20 и 1, коллекторы которых соецинекы с шиной 4 питания, эмиттер восьмого тракзисторя 21 соединен с базой вто 47. Цля задания сьещения разкого уровня ца бязь Шуцтирующих транзистороввведена цепь 46 смещения, содержащаятранзистор 24 и резистивный делительна резисторах 25, 26 и 27. Выходной,т",аскад 44 и элемент блокировки построены по схеме токового зеркала1 ил. рого транзистора 6, эмиттер седьмого транзистора 20 сседицен с вторым выводом первого резистора 2, базой третьего транзистора 7 и с коллектором девятого транзистора 22, эмиттер которого соедицец с общей шиной 10, а база соединена с катодом втогого диода 19 и колле 1:тором и базой десятого транзистора. 23, эмтлттер которого соединен с )бщей шиной 10, база второгс трацзистэра 6 соединена с коллектором одиняадцатого транзистора 4, эмиттеу которого соединен с общей шиной 10, и через последователь- НО СОЕДИНС 1 тЦЫЕ ШЕСТОЙ СЕДЬМОЙ И ВОСЬ- мой резисторы 25-27 - с обшей шиной 10, база одиццалцятого транзистора 24 соединена с общей гочкой соединения седьмого и вось 1 ого резисторов 26 И 27 Об 1 ПЯ 11 ТОтцтя СОЕднцЕцця ШЕСТОГО и седьмого уезистсров 5 и 26 соединена с базЯМИ дветадцатогс и тринадцатого трягзисгорс,г 28 и 29, эмиттер второго туянзис.ора 6 соединен с базой четырнядцятс 1 гст транзистора 30, КОЛЛЕКТОР КОтОРстГС 7 .-ТЕРЕЗ ДЕВЯтЫй РЕ- зистор 3соедцце 1. с шинОЙ 4 питания иколлектором шестого ттрянзисторя 12, база которого соед:и:еца с эмиттером четырнадцатого транзистора 30 и через десятый рез:1 стоу 32 - с выходной шиной 11 и с эмлттером тринадцатого туанзистора 29., коллектор которого соединен с базой четвертого транзистора 9, эмиттер третьего транзистора 7 через одиннадцатый резистор 33 соединен с базой пятнадцатого транзистора 34 и коллектором двенатрцатого транзистора 28, эмиттер которого соединен с коллектором пятнадцатого транзистора 34 и через двенаццэ.тый резистор 35 - с бязсй четвертого транзистсря. 9, ь 7 митте 1 у пятнатпятого транзистсра 34 соединен с обпей шиной 10, 1269252коллектор третьего транзистора 7 сое- да 44 выполнен на токовом зеркале,динен с .коллектором шестого транзис- входная цепь которого служит для затора 13, база которого соединена с дания смещения на базы фиксирующихэмиттером шестнадцатого транзистора транзисторов 20 и 21, потенциал ло 11 1136 и коллектором и базой с емн адца то - 5 гич е с к о го 0 н а базе фаз о р асще пиг о транзистора 3 7 , эмитт ер которого тельного транзистора 7 фиксирован ичерез тринадцатый резистор 38 сое- Равен О, - падение напряжения надинен с общей шиной 10, коллектор прямосмещенном переходе база-эмиттер,шестнадцатого транзистора 36 соеди- а смещение на база-коллекторном пенен с шиной 4 питания, а база - с 10 реходе шунтирующего транзистора 6коллектором восемнадцатого транзисто- задается равным нулю,ра 39 и коллектором и базой девятнад- В состоянии логической "1" нацатого транзистора 40, эмиттер кото- входе 3 фазорасщепительный и выходрого соединен с коллектором и базой ной транзисторы 7 и 9 включены и надВадцатОГО траНЗИСтОра 41, ЭМИттЕР 15 СЬПцЕНь 1, ПОтЕНцИаЛЫ ИХ КОЛЛЕКтОрОВкоторого через четырнадцатый резис- для ограничения глубины и насыщениятор 42 соединен с шиной 4 питания, фиксируются транзисторами 6 и 29.база восемнадцатого транзистора 39 Транзисторы 30 и 12 выходного эмитчерез пятнадцатый резистор 43 соеди- терного повторителя заперты. Опорныеиена с шиной 4 питания, а эмиттер - 20 потенциалы на базе транзисторов 6 ис входной шиной 15 блокировки. Струк ограничения насыщения задаютсятурно ТТЛ-инвертор состоит из вход- исходя из заданных параметров шунтиного каскада 44 на транзисторе 1 и руемых транзисторов за счет соответисточника 45 тока на фиксирующих ствующего выбора резисторов в цепочтранзисторах 20 и 21 и токовом зер ке смещения,кале на транзисторах 23 и 22, цепоч- Состояние блокировки (или третьеки 46 смещения на транзисторе 24, состояние) задается сигналом логичесфазорасщепительного каскада 47 на кой "1" на входной шине 15 блокировфазорасщепительном транзисторе 7, ки, Ток коллектора транзистора 13первом и втором элементах 48 и 49 50 блокировки должен быть достаточнымограничения повышения,на транзисто- по величине, что бы за счет падениярах 6 и 28, нелинейной нагрузке на напряжения на резисторах 8 и 2 сфортранзисторе 34, выходного каскада 50 мировать уровень логического "0" нана эмиттерном повторителе на тран- входе и инверсном выходе фазорасщезисторе 30, выходных транзисторов 12 пительного каскада,35и 9 и втором элементе 51 ограниченияповышения на транзисторе 29, каскада 52 блокировки на транзисторе 13 Формула из обретенияи входного каскада 53 блокировки натранзисторах 36 и 39,40ТТЛ-инвертор на и-р-п-транзистоУстройство работает следующим об- рах, содержащий входной каскад наразом, первом транзисторе с первым резистоВ состоянии логического 1101 на ром в эмиттерной цепи, база первоговходе 3 (здесь и далее при описании транзистора соединена с первой входработы подразумевается что на вход- ной шиной а коллектор - с шиной пий 459ной шине 15 блокировки также логичес- тания, эмиттер первого транзисторакий "0", блокировка рассматривается через второй резистор соединен с баотдельно ниже) фазорасщепительный 7 зой второго транзистора, эмиттер кои выходной транзисторы 2 заперты и торого соединен с коллектором третьена выходе 11 выходным эмиттерным пов- го транзистора и через третий резис 50торителем задается потенциал логи- тор - с шиной питания, база третьегоческой "1". Цепочка 46 смещения зада- транзистора соединена с коллекторомет также низкие уровни на базе тран- второго транзистора, а эмигтер - сзисторов 6, 29 и 28 ограничения насы- базой четвертого транзистора, эмитщения, что предотвращает отпирание тер которого соединен с общей шиной,55их переходов база-коллектор и пере- а коллектор - с выходной шиной иключение их в инверсный активный ре- эмиттером пятого транзистора, каскаджим. Источник 45 тока входного каска- блокировки на шестом транзисторе,1269252 Ссставитель А,КабановТехред Л.Сердюкова Корректор М,Самборская Редактор В,Иванова Заказ 6045/57 Тираж 81 б ВНИИПИ Государственного кбмитета СССР по делам изобретений и открытий 113035, Москва, В(-35, Раушскзя наб д. 4/5Подписное Производственно-полиграФическое предприятие, г.ужгород, ул. Проектная,эмиттер которого через четвертый резистор соединен с общей шиной, атакже входную шину блокировки, о тл и ч а ю щ и й с я тем, что, сцелью увеличения быстродействия и повышения надежности при блокировке, внего введены инверсная входная шина,соединенная через пятый резистор санодом первого диода, катод которото соединен с анодом второго диода 1 Ои базами седьмого и восьмого транзис.торов, коллекторы которых соединеныс шиной питания, эмиттер восьмоготранзистора соединен с базой второготранзистора, эмиттер седьмого транзистора соединен с вторым выводомпервого резистора, базой третьеготранзистора и коллектором девятоготранзистора, эмиттер которого соединен с общей шиной, а база - с като Одом второго диода и коллектором ибазой десятого транзистора, эмиттеркоторого соединен с общей шиной, база второго транзистора соединена сколлектором одиннадцатого транзистора, эмиттер которого соединен с общей шиной, и через последовательносоединенные шестой, седьмой и восьмой резисторы - с общей шиной, базаодиннадцатого транзистора соединена ЗОс общей точкой соединения седьмого ивосьмого резисторов, общая точка соединения шестого и седьмого резисторов соединена с базами двенадцатогои тринадцатого транзисторов, эмиттервторого транзистора соединен с базойчетырнадцатого транзистора, коллектор1 которого через девятый резистор соединен с шиной питания и коллекторомпятого транзистора, база которогосоединена с эмиттером четырнадцатого транзистора и через десятый резистор - с выходной шиной и эмиттеромтринадцатого транзистора, коллекторкоторого соединен с базой четвертоготранзистора, эмиттер третьего транзистора через одиннадцатый резисторсоединен с базой пятнадцатого транзистора и коллектором двенадцатоготранзистора, эмиттер которого соединен с коллектором пятнадцатого транзистора и через двенадцатый резисторс базой четвертого транзистора, эмиттер пятнадцатого транзистора соединенс общей шиной, коллектор третьеготранзистора соединен с коллекторомшестого транзистора, база которогосоединена с эмиттером шестнадцатоготранзистора и коллектором и базойсемнадцатого транзистора, эмиттеркоторого через тринадцатый резисторсоединен с общей шиной, коллекторшестнадцатого транзистора соединен сшиной питания, а база - с коллектором восемнадцатого транзистора и коллектором и базой девятнадцатого транзистора, эмиттер которого соединенс коллектором и базой двадцатоготранзистора, эмиттер которого черезчетырнадцатый резистор соединен собщей шиной, база восемнадцатоготранзистора через пятнадцатый резистор соединена с шиной питания, а эмиттер - с входной шиной блокировки.

СмотретьЗаявка

3831343, 29.12.1984

МОСКОВСКИЙ ИНСТИТУТ ЭЛЕКТРОННОЙ ТЕХНИКИ

БАЛАШОВ СЕРГЕЙ МИХАЙЛОВИЧ, ДЯТЧЕНКО ВЛАДИМИР НИКОЛАЕВИЧ, СОКОЛОВ НИКОЛАЙ ВЛАДИМИРОВИЧ, СКВИРА АНАТОЛИЙ ВАСИЛЬЕВИЧ, РОДИОНОВ ЮРИЙ ПЕТРОВИЧ

МПК / Метки

МПК: H03K 19/088

Метки: ттл-инвертор

Опубликовано: 07.11.1986

Код ссылки

<a href="https://patents.su/4-1269252-ttl-invertor.html" target="_blank" rel="follow" title="База патентов СССР">Ттл-инвертор</a>

Предыдущий патент: Устройство выбора каналов

Следующий патент: Схема контроля на четность и л типа

Случайный патент: Способ получения смеси цис и трансизомеров 3, 7диметил-2, 6 октадиеннитрила