Система автоматического управления (ее варианты)

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

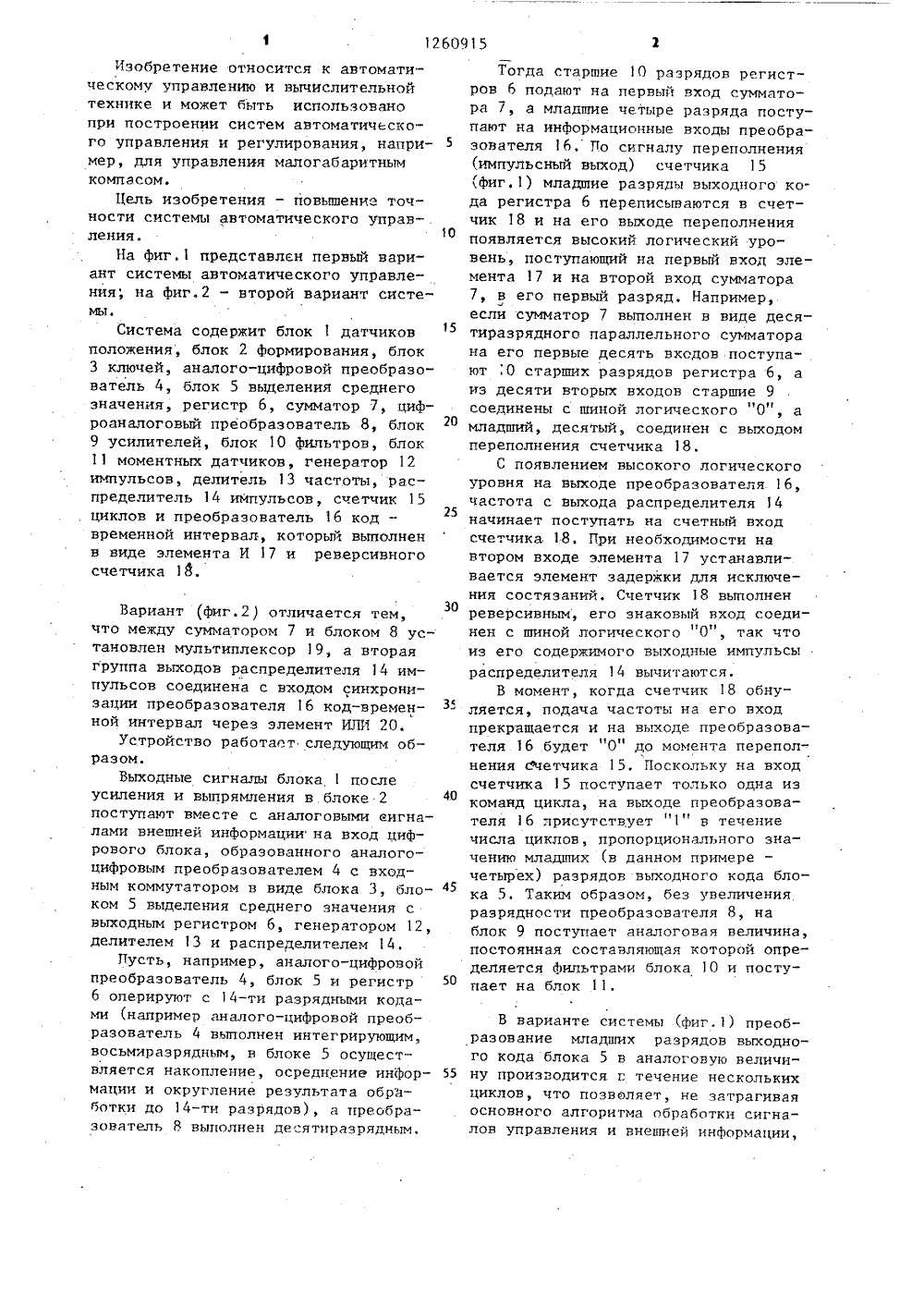

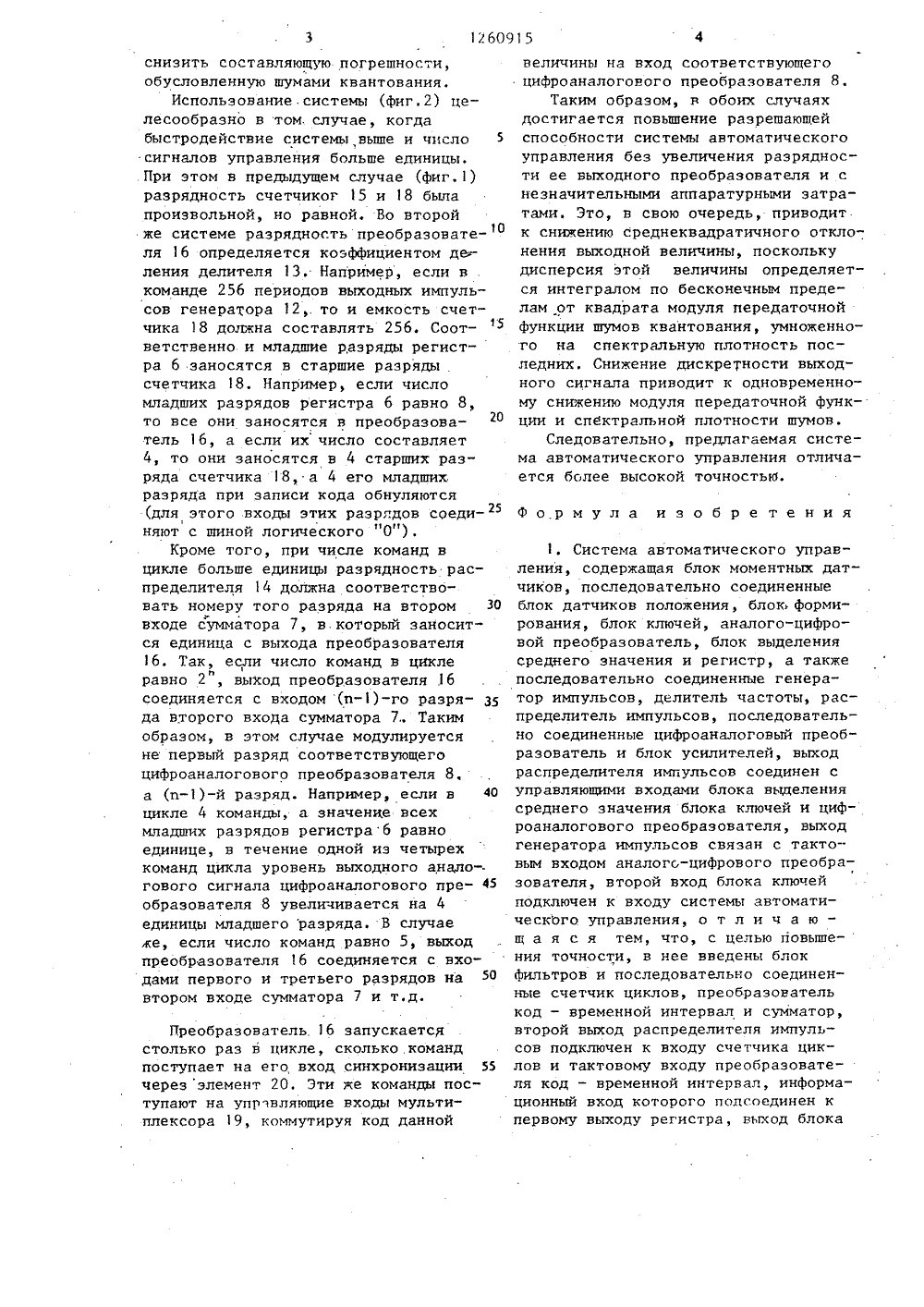

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК Д 1 4 С 05 В 11/01 КОМИТЕТ ССНий Ь ОТНРЫТ ГОСУДАРСТНЕННЫ ПО ДЕЛАМ ИЗОБРЕ ЕТЕНИЯ ЕЛЬСТВ ьзова- одвиж - по- счет ОПИСАНИЕ И К АВТОРСКОМУ СВИДЕ(56) Гироскопические системы. Под ред. Полонора Л.С. ч, 1. М.: Высшая школа, 1977, с. 22-23.Авторское свидетельство СССР Ф 1130830, кл. С 05 В 13/02, 1983. (54) СИСТЕМА АВТОМАТИЧЕСКОГО УЛРАВЛЕНИЯ (ЕЕ ВАРИАНТЫ)(57) Изобретение относится к автоматическому управлению и вычислитель" 80126 О 915 ной технике и может быть испол но для управления положением п ных объектов. Цель изобретения вышение точности управления за повышения запаса устойчивости и снижения составляющей погрешности, обус ловленной шумами квантования. Лостав ленная цель достигается тем, что за счет изменения разрешающей способнос ти цифроаналогового преобразователя изменено соотношение разрешающих спо собностей аналого-цифрового и цифроаналогового преобразователей, что приводит к повышению точности коррек ции, осуществляемой по каналу управления системы. 2 с. п, ф-лы, 2 ил,1260915 Тогда старшие О разрядов регистров 6 подают на первый вход сумматора 7, а младптие че.тыре разряда поступают на информационные входы преобразователя 16. По сигналу переполнения(фиг.1) младшие разряды выходного кода регистра 6 переписываются в счетчик 18 и на его выходе переполненияпоявляется высокий логический уровень, поступающий на первый вход элемента 17 и на второй вход сумматора7, в его первый разряд. Например,если сумматор 7 выполнен в виде десятиразрядного параллельного сумматорана его первые десять входов поступают .0 старших разрядов регистра б, аиз десяти вторых входов старшие 9соединены с шиной логического 10 , амладший, десятый, соединен с выходомпереполнения счетчика 18,С появлением высокого логическогоуровня на выходе преобразователя 16,частота с выхода распределителя 14начинает поступать на счетный входсчетчика. 18. При необходимости навтором входе элемента 17 устанавливается элемент задержки для исключения состязаний, Счетчик 18 выполненреверсивным, его знаковый вход соединен с шиной логического "О", так чтоиз его содержимого выходные имттульсыраспределителя 14 вычитаются,В момент, когда счетчик 18 обнуляется, подача частоты на его входпрекращается и на выходе преобразователя 1 б будет "0" до момента переполнения счетчика 15, Поскольку на входсчетчика 15 поступает только одна изкоманд цикла, на выходе преобразователя б присутствует "1" в течениечисла циклов, пропорционального значению младших (в данном примере -четырех) разрядов выходного кода блока 5. Таким образом, без увеличенияразрядности преобразователя 8, наблок 9 поступает аналоговая величина,постоянная составляющая которой определяется фильтрами блока 10 и поступает на блок 11. 30 Вариант (фиг.2) отличается тем, что между сумматором 7 и блоком 8 установлен мультиплексор 19, а вторая группа выходов распределителя 14 импульсов соединена с входом синхронизации преобразователя 16 код-временной интервал через элемент ИЛИ 20.Устройство работает следующим образом.Выходные сигналы блокапосле усиления и выпрямления в.блоке 240 поступают вместе с аналоговыми сигналами внешней информациина вход цифрового блока, образованного аналогоцифровым преобразователем 4 с входным коммутатором в виде блока 3, бло ком 5 выделения среднего значения с выходным регистром 6, генератором 12, делителем 3 и распределителем 14.Пусть, например, аналого-цифровой преобразователь 4, блок 5 и регистр 50 6 оперируют с 14-ти разрядными кодами (например аналого-цифровой преобразователь 4 выполнен интегрирующим, восьмиразрядным, в блоке 5 осуществляется накопление, осреднение инфор мации и округление результата обработки до 4-ти разрядов), а преобразователь 8 выполнен десятиразрядным,Изобретение относится к автоматическому управлению и вычислительной технике и может быть использовано при построении систем автоматического управления и регулирования, напри мер, для управления малогабаритным компасомЦель изобретения - повышение точности системы автоматического управления.На фиг.1 представлен первый вариант системы автоматического управления; на фиг.2 - второй вариант системыСистема содержит блокдатчиков положения, блок 2 формирования, бпок 3 ключей, аналого-цифровой преобразователь 4, блок 5 выделения среднего значения, регистр 6, сумматор 7, цифроаналоговый преобразователь 8, блок 9 усилителей, блок 10 фильтров, блок 11 моментных датчиков, генератор 12 импульсов, делитель 13 частоты, распределитель 14 импульсов, счетчик 15 . циклов и преобразователь 16 код -25 временной интервал, который выполнен в виде элемента И 17 и реверсивного счетчика 18. В варианте системы (фиг.1) преобразование младших разрядов выходного кода блока 5 в аналоговую величину производится в течение нескольких циклов, что позвеляет, не затрагивая основного алгоритма обработки сигналов управления и внешней информации, 1260915снизить составляющую погрешности,обусловленную шумами квантования.Использование.системы (фиг.2) целесообразно в том. случае, когдабыстродействие системы вьппе и число 5сигналов управления больше единицы.. При этом в предыдущем случае (фиг,1)разрядность счетчиког 15 и 18 былапроизвольной, но равной. Во второйже системе разрядность преобразовате 1 Оля 1 б определяется коэффициентом деления делителя 13, Например, если вкоманде 256 периодов выходных импульсов генератора 12,. то и емкость счетчика 18 должна составлять 256. Соответственно и младшие разряды регистра 6 заносятся в старшие разрядысчетчика 18. Например, если числомладших разрядов регистра 6 равно 8,то все они заносятся в преобразователь 16, а если ихчисло составляет4, то они заносятся в 4 старших разряда счетчика 18, а 4 его младшихразряда при записи кода обнуляются(для этого входы этих разрядов соединяют с шиной логического "0),Кроме того, при числе команд вцикле больше единицы разрядность распределителя 14 должна соответствовать номеру того разряда на втором ЗОвходе сумматора 7, в.который заносится единица с выхода преобразователя16. Так, если число команд в циклеравно 2 , выход преобразователя 1 бсоединяется с входом (и)-го разря- З 5да второго входа сумматора 7,. Такимобразом, в этом случае модулируетсяне первый разряд соответствующегоцифроаналогового преобразователя 8,а (и)-й разряд. Например, если в 40цикле 4 команды, а значение всехмладших разрядов регистра 6 равноединице, в течение одной из четырехкоманд цикла уровень выходного анало=гового сигнала цифроаналогового преобразователя 8 увеличивается на 4единицы младшего разряда. В случаеже, если число команд равно 5, выходпреобразователя 16 соединяется с входами первого и третьего разрядов навтором входе сумматора 7 и т.д. Преобразователь. 16 запускается столько раз в цикле, сколько команд поступает на его,вход синхронизации 55 через элемент 20. Эти же команды поступают на управляющие входы мультиплексора 19, коммутируя код данной величины на вход соответствующего цифроаналогового преобразователя Я.Таким образом, в обоих случаях достигается повьппение разрешаюшей способности системы автоматического управления без увеличения разрядности ее выходного преобразователя и с незначительными аппаратурными затратами, Это, в свою очередь, приводит к снижению среднеквадратичного отклонения выходной величины, поскольку дисперсия этой величины определяется интегралом по бесконечным пределам от квадрата модуля передаточной функции шумов квантования, умноженного на спектральную плотность последних. Снижение дискретности выходного сигнала приводит к одновременному снижению модуля передаточной функции и спектральной плотности шумов.Следовательно, предлагаемая система автоматического управления отличается более высокой точностью.Ф о.р м у л а и з о б р е т е н и яСистема автоматического управления, содержащая блок моментных датчиков, последовательно соединенные блок датчиков положения, блок формирования, блок ключей, аналого-цифровой преобразователь, блок выделения среднего значения и регистр, а также последовательно соединенные генератор импульсов, делителЬ частоты, распределитель импульсов, последовательно соединенные цифроаналоговый преобразователь и блок усилителей, выход распределителя импульсов соединен с управляющими входами блока выделения среднего значения блока ключей и цифроаналогового преобразователя, выход генератора импульсов связан с тактовым входом аналого-цифрового преобразователя, второй вход блока ключей подключен к входу системы автоматического управления, о т л и ч а ю - щ а я с я тем, что, с целью повьппе-ния точности, в нее введены блок фильтров и последовательно соединенные счетчик циклов, преобразователь код - временной интервал и сумматор, второй выход распределителя импульсов подключен к входу счетчика циклов и тактовому входу преобразователя код - временной интервал, информационный вход которого подсоединен к первому выходу регистра, выход блокафУ 8оставитель Г,Нефедоваехред А Кравчук Коррек дактор И.К атай Заказ 5230/ Тираж 83 ВНИИПИ Государственн по делам, изобретен 13035, Москва, Ж"-3ПодписноеСР ого комитета ий и открытийРаущская на д л. Проектная, 4 Производственно-полиграфическое предприятие, г. у 3усилителей через блок фильтров подключен к входу блока моментных датчи" ков, второй выход регистра подсоединен к второму входу сумматора, подключенного выходом к входу цифроаналогового преобразователя,2, Система автоматического управления, содержащая блок моментных датчиков, последовательно соединенные .блок датчиков положения, блок формирования, блок ключей, аналого-цифровой преобразователь, блок выделениясреднего значения и регистр, а такжепоследовательно соединенные генератор импульсов, делитель частоты, распределитель импульсов, последовательно соединенные цифроаналоговый преобразователь и блок усилителей, выходраспределителя импульсов соединен суправляющими входами блока выделения 20среднего значения, блока ключей ицифроаналогового преобразователя, выход генератора импульсов связан сСцгнав внвижц"имщрмждэ тактовым входом аналого-цифровогопреобразователя, второй вход блокаключей подключен к входу системы автоматического управления, о т л и -ч а ю щ а я с я тем, что, с цельюповьнпения точности, в нее введеныблок фильтров и последовательно соединенные элемент ИЛИ, преобразователь код - временной интервал, сумматор и мультиплексор, второй выходраспределителя импульсов связан свходом элемента ИЛИ, выход генератора импульсов соединен с тактовым входом преобразователя код - временнойинтервал, информационный вход которого подключен к первому выходу регистра, вьгход блока усилителей черезблок фильтров связан с входом блокамоментных датчиков выход мультиплексора подсоединен к входу цифроаналогового преобразователя, второй выходрегистра соединен с вторым входомсумматора.

СмотретьЗаявка

3894768, 17.05.1985

ПРЕДПРИЯТИЕ ПЯ В-8618

АЛЬТШУЛЕР ВИКТОР СЕРГЕЕВИЧ, ВАСЮХНО АНАТОЛИЙ АЛЕКСЕЕВИЧ, ВОЛКОВ ЛЕВ НИКОЛАЕВИЧ, ВОЛНЯНСКИЙ ВЛАДИМИР НИКОЛАЕВИЧ, ОРЛОВ АНДРЕЙ ВАЛЕНТИНОВИЧ, ФИЛАТОВ ВИКТОР МИТРОФАНОВИЧ

МПК / Метки

МПК: G05B 11/01

Опубликовано: 30.09.1986

Код ссылки

<a href="https://patents.su/4-1260915-sistema-avtomaticheskogo-upravleniya-ee-varianty.html" target="_blank" rel="follow" title="База патентов СССР">Система автоматического управления (ее варианты)</a>

Предыдущий патент: Схема управления автоматическими коробками скоростей металлорежущих станков

Следующий патент: Система оптимизации режимов работы объекта

Случайный патент: Состав для печати на триацетатных текстильных материалах