Последовательно-параллельное устройство для умножения чисел в дополнительном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1259252

Автор: Масленников

Текст

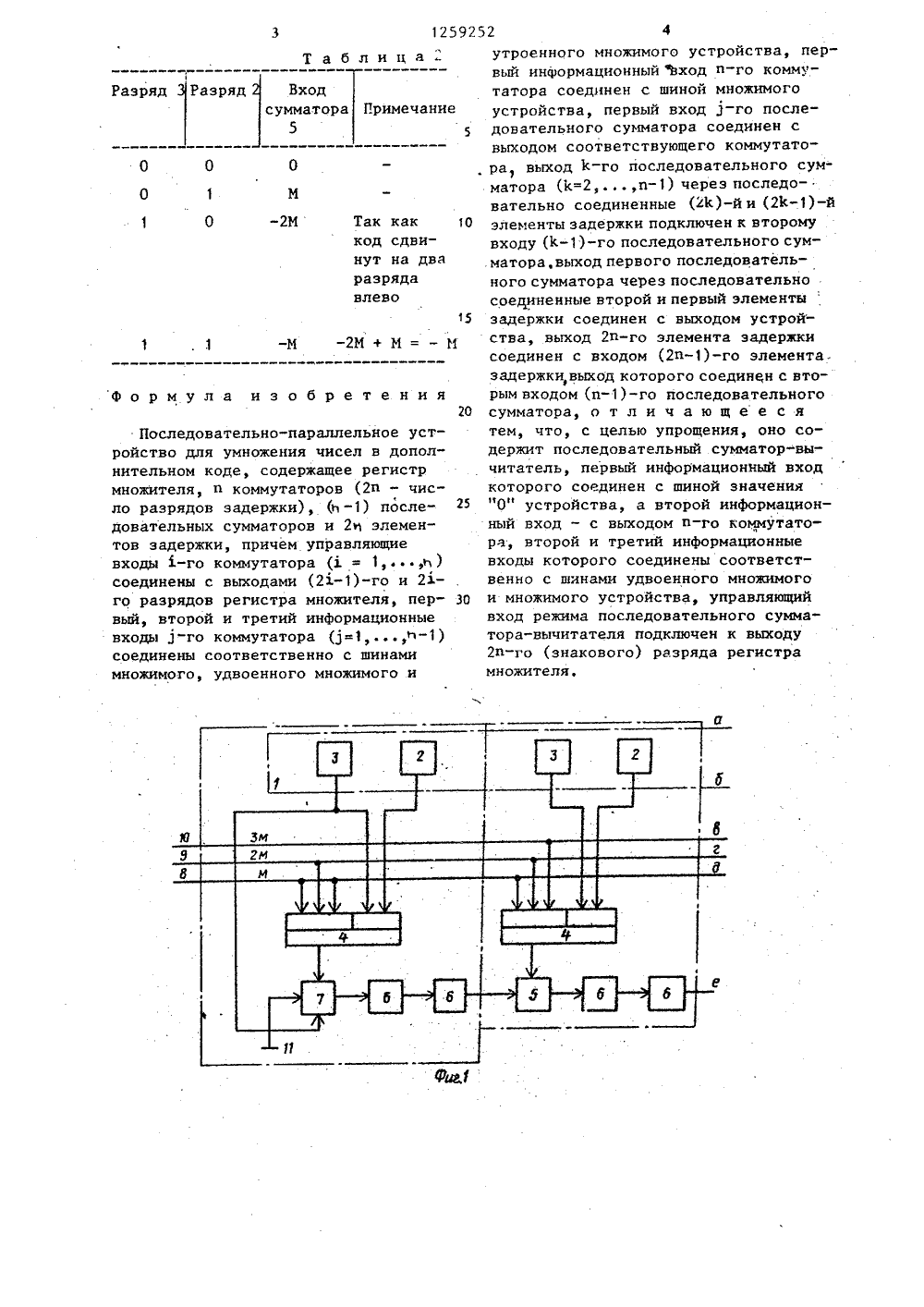

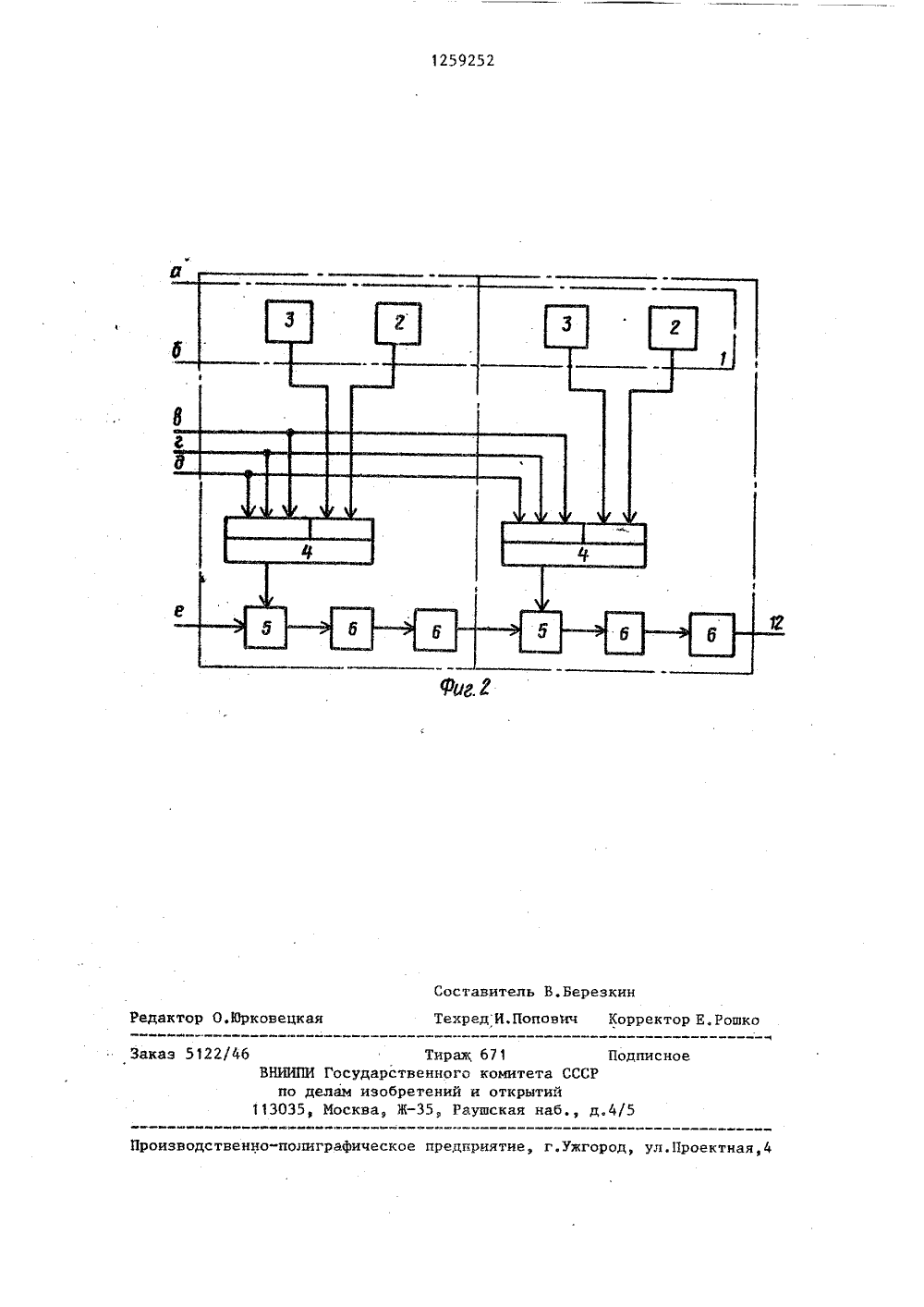

(54) ПОСЛЕДОВАТЕЛЬНОУСТРОЙСТВО ДЛЯ УМНОЖЕДОПОЛНИТЕЛЬНОМ КОДЕ(57) Изобретение относится к ости вычислительной техники, в чности к арифметическим устройсти предназначено для выполнениярации умножения двух двоичных чпредставленных в дополнительномде, Целью изобретения является у,801259252 щение устройства. Устройство содержит регистр множителя, коммутаторы, последовательные сумматоры, элементы задержки, последовательный сумматор-вычитатель , шины множимого, удвоенного,множимого, утроенного мно" жимого, значения "0" и выход. В устройстве использован метод умножения двоичных чисел в дополнительном коде с двумя корректирующими шагами, в соответствии с которыми определяется произведение мантисс сомножителей, т,е, кодов сомножителей без учета их знаков, Затем осуществляется коррекция произведения мантисс путем а вычитания множимого (если множитель отрицателен) либо вычитания множимого, множителя и единицы старшего разряда (если оба сомножителя отрицательны) из кода произведения мантисс. 2 ил., 2 табл,412592 0 0 О Изобретение относится к вычислительной технике, а конкретно к ариФ- метическим устройствам, и предназначено для умножения двух двоичных чисел, представленных в дополнительном 5 коде.Целью изобретения является упрощение устройства.На Фиг.1 и 2 приведена функциональная схема предлагаемого устройства,Устройство содержит регистр 1 множителя, имеющий нечетные и четные разряды 2 и 3 (последний четный разряд 3 регистра 1 является знаковым), коммутаторы 4, последовательные сумматоры 5, элементы б задержки, последовательный сумматор-вычитатель 7 шину 8 множимого, шину 9 удвоенного множимого, шину 10 утроенного множимого, шину 11 значения "0",выход 12. 20Устройство работает следующим образом.Множитель записывается в регистр и хранится в нем в течение всей операции умножения в параллельном коде. Мантисса множимого поступает в устройство в последовательном коде по шинам 8 (М), 9(2 М) и 10(ЗМ), В устройстве использован метод умножения двоичных чисел в дополнительном ко- ЗО де с двумя корректирующими шагами, в соответствии с которым определяется произведение мантисс сомножителей, т.е. кодов сомножителей без учета их знаков, затем осуществляется коррекция произведения мантисс путем вычитания множимого (если множитель отрицателен) либо вычитания множителя (если множимое отрицательно), либо вычитания множимого, множителя и еди ницы старшего разряда (если оба сомножителя отрицательны) из кода произведения мантисс.В зависимости от значения разрядов множителя, составляющих соответствующую пару, коммутатор 4 Формирует частичное произведение кода мантиссы множимого на данную пару разрядов множителя путем переключения кодов кратного множимого с шин 8 - 10 на первый вход соответствующего сумматора 5 в соответствии с табл,1. 52ю 2савтоматический сдвиг влево на дваразряда последовательного кода частичного произведения, полученного отболее старшей пары разрядов множителя. В результате аналогичных преоб-.разований получается последовательный код произведения мантиссы множимого на младшие 2( -1) разряда кодамножителя. Младший разряд (л)-й парырегистра 1 представляет собой старший разряд мантиссы множителя, астарший разряд - знак множителя, Преобразования относительно старшегоразряда мантиссы множителя аналогич,ны преобразованию в предыдущих звеньях,а преобразования относительнознака множителя сводятся к вычи-.танко кода мантиссы множимого вслучае отрицательного множителя,Таким образом, преобразование,приведенное к второму входу( -Иго сумматора 5, сводится ктабл.2,В соответствии с табл,2 и-й коммутатор 4 звена должен. подключить код с шины 8 (М) либо код с шины 9 (2 М). Сумматор-вычитатель 7 может передать код, снимаемый с коммутатора 4 в не" иэменном виде, либо вычесть этот код из нулевого кода, т.е. присвоить коду противоположный знак в зависимости от значения знакового разряда множителя, С этой целью сигнал с выхода и-го разряда 3 поступает на управляющий вход режима сумматора-вычитателя 7. Таким образом, устройство Формирует код произведения мантисс сомножителей и осуществляет коррекциюполученного кода на отрицательный множитель. Коррекция произведения в случае отрицательного множимого может быть осуществлена специальным вычитателем.В Таблица 1Разряд Разряд 2 Вход сумматора 555 2 М На второй вход сумматора 5 поступает накопленное частичное произведение с выхода последующего сумматора 5, задержанное на два такта элементами 6 задержки что обеспечивает12592 Т аблица Разряд Входсумматора Примечание55 Разряд О О О О Так как 10код сдвинут на дваразрядавлево О-2 М + И = - И Последовательно-параллельное устройство для умножения чисел в дополнительном коде, содержащее регистр множителя, и коммутаторов (2 п - число разрядов задержки), Ь -1) после довательных сумматоров и 2 элементов задержки, причем управляющие входы 1-го коммутатора (1 = 1, р) соединены с выходами (2 х)-го и 21- го разрядов регистра множителя, пер вый, второй и третий информационные входы 3-го коммутатора (=1п) соединены соответственно с шинами множимого, удвоенного множимого и Формула изобретения20 52 4утроенного множимого устройства, первый информационный вход п-го коммутатора соединен с шиной множимого устройства, первый вход 1-го последовательного сумматора соединен с выходом соответствующего коммутато. ра выход 1-го последовательного сумматора (к=2п) через последовательно соединенные (Ж)-йи (21-1)-й элементы задержки подключен к второму входу (-1)-го последовательного сумматора,выход первого последовательного сумматора через последовательно соециненные второй и первый элементы задержки соединен с выходом устрой- ства, выход 2 п-го элемента задержки соединен с входом (2 п)-го элемента.задержки, выход которого соединЕн с вторым входом (и) -го последовательного сумматора, о т л и ч а ю щ е е с я тем, что, с целью упрощения, оно содержит последовательный сумматор-вычитатель, первый информационный вход которого соединен с шиной значения "О" устройства, а второй информационный вход - с выходом и-го коммутатора, второй и третий информационные входы которого соединены соответственно с шинами удвоенного множимого и множимого устройства, управляющий вход режима последовательного сумматора-вычитателя подключен к выходу 2 п-го (знакового) разряда регистра множителя,оставитель В.Березки Редактор О,Юрковецкая ТехредИ,Попович Корректор Е.Рошк Тираж 671 Государственного коми лам изобретений и от Москва, Ж, Раушск каэ 5122 46 Подписета СССР рытиия наб, д по 03 Производственно-полиграфическое предприятие, г.ужгород, ул,Проектная,4

СмотретьЗаявка

3840519, 15.01.1985

ПРЕДПРИЯТИЕ ПЯ В-2887

МАСЛЕННИКОВ ВИТАЛИЙ БОРИСОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: дополнительном, коде, последовательно-параллельное, умножения, чисел

Опубликовано: 23.09.1986

Код ссылки

<a href="https://patents.su/4-1259252-posledovatelno-parallelnoe-ustrojjstvo-dlya-umnozheniya-chisel-v-dopolnitelnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Последовательно-параллельное устройство для умножения чисел в дополнительном коде</a>

Предыдущий патент: Устройство для деления

Следующий патент: Вычислительное устройство

Случайный патент: Установка для термопластического упрочнения деталей