Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

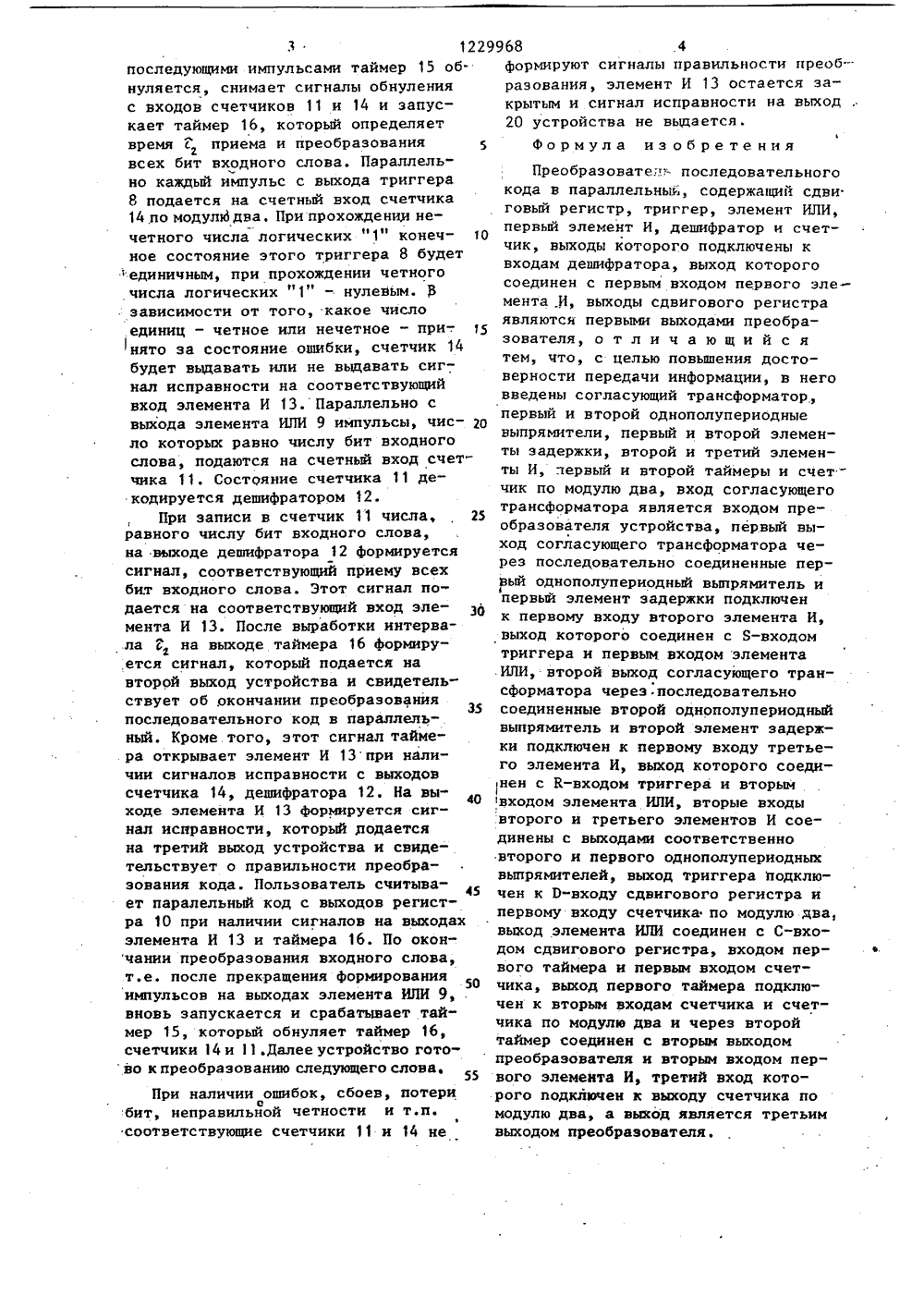

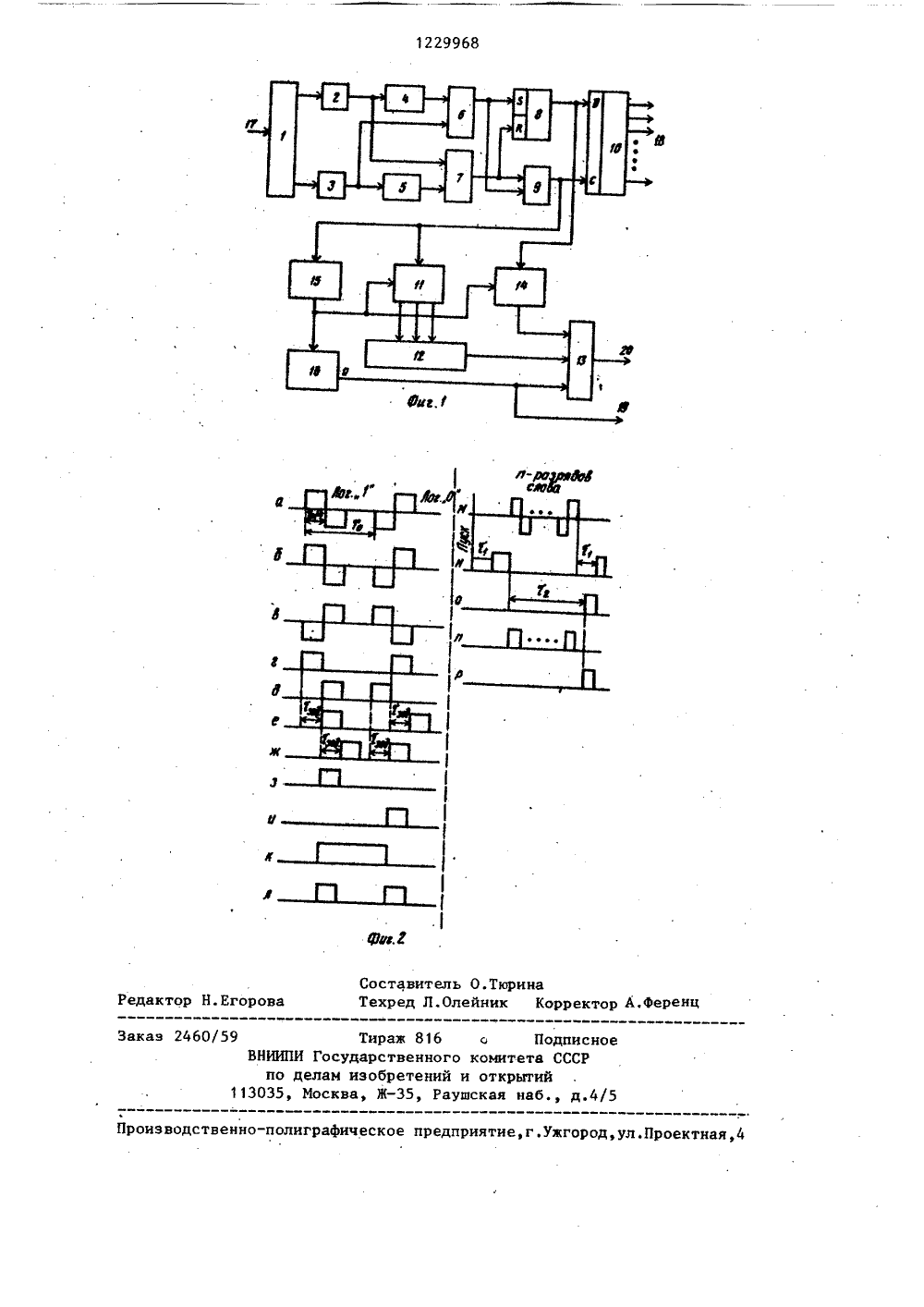

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИСПУ БЛИК 03 М 9/О АНИЕ ИЗОБРЕТЕНИЯ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ВТОРСКОМУ СВИДЕТЕЛЬС(56) Авторское свидетельство СССР л" 822175, кл. С 06 Р 5/04, 1981.Авторское свидетельство СССР У 924696, кл. С 06 Г 5/04, 1982, (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ (57) Изобретение относится к вычислительной технике и может быть использовано для передачи бинарной информации с помощью сигналов трех.овней напряжения между ЭВМ и периферийными устройствами, находящими- " ся на больших расстояниях одно от другого. Целью изобретения является повышение достоверности передачи информации в виде сигналов трех уровней напряжения (+0,-0,0) за счет выделения логического значения " 1" или "0" из двухполярных импульсов, подсчета числа бит в преобразуемом слове, контроля двоичного кода преобразуемого слова по четности, временного контроля преобразования, фиксирующего его начало и конец. Преобразователь содержит согласующий трансформатор, два однополупериодных выпрямителя, два элемента задержки, три элемента И, триггер, элемент ИЛИ,.О сдвиговый регистр, счетчик, дешифра- э тор, счетчик по модулю два, два таймера, вход и три выхода. 2 ил.С:50 551 Изобретение относится к вычислительной технике и может быть использовано для передачи бинарной информации с помощью сигналов трех уровней напряжения между ЭВМ и периферийными устройствами, находящимисяна больших расстояниях друг от друга,Целью изобретения является повышение достоверности передачи информации в виде сигналов трех уровнейнапряжения (+Ч,-П,О) за счет вьделения логического значения " 1" или,0" из двухполярных импульсов, подсчета числа бит в перобразуемом слове, контроля двоичного кода преобразуемого,слова по четности, временного контроля преобразования,фиксирующего его начало и конец.На фиг.1 дана функциональная схема устройства; на фиг.2 - временныедиаграммы работы устройства.Преобразователь содержит согласу-ющий трансформатор 1, первый и второйоднополупериодные выпрямители 2 и 3,первый элемент 4 задержки, второйэлемент 5 задержки, второй элементИ 6, третий элемент И 7, триггер 8,элемент ИПИ 9, сдвиговый регистр 10,счетчик 11, дешифратор 12, первыйэлемент И 13, счетчик 14 по модулюдва, первый таймер 15, второй таймер 16, вход 17 устройства, первый,второй и третий выходы 18 - 20 устройства,Устройство работает следующим об-.разом,В исходном состоянии при включении питания и отсутствии сигналовна выходе элемента ИЛИ 9 включаетсятаймер 15, который через заданноевремя с вырабатывает на своем выходе сигнал, устанавливающий в нулевое положение счетчики 11 и 14 итаймер 16 (фиг.2 н).Входное слово информации подаетсяна вход 17 устройства последовательно бит за битом, начиная с первогоразряда слова. При этом входные сигналы определяются тремя уровнями напряжения: +О, -П, О. Информация втечение бит-интервала Т представляоется двухполярными импульсами и соответствует фиг.2 а.Информационный бит "1" кодируется.как последовательное состояние уровней +П, -П, О, информационный бит "О,кодируется как последовательноесостояние уровней -П, +П, О. Двухполярный импульс бита подается на вход согласующего трансформатора 1.Согласующий трансформатор 1 формирупают импульсы с выхода элементаИЛИ 9, Таким образом, происходит на"капливание и сдвиг кодовых импульсов в сдвиговом регистре 10. Сдвигипродолжаются и тактов, где и - число разрядов входного слова.Импульсы с выхода элемента ИЛИ 9 подаются на вход установки в нулевое положение таймера 15. Первым и3 1229 последующими импульсами таймер 15 об. нуляется, снимает сигналы обнуления с входов счетчиков 11 и 14 и запускает таймер 16, который определяет время с приема н преобразованияг5 всех бит входного слова. Параллельно каждый импульс с выхода триггера 8 подается на счетный вход счетчика 14 по модулк 1 два, При прохождении нечетного числа логических "1" конеч О ное состояние этого триггера 8 будетединичным, при прохождении четного числа логических "1" - нулевым, Р зависимости от того, какое число единиц - четное или нечетное - при-. 15 нято за состояние ошибки, счетчик 14 будет выдавать или не выдавать сигнал исправности на соответствующий вход элемента И 13. Параллельно с выхода элемента ИЛИ 9 импульсы, чис о ло которых равно числу бит входного слова, подаются на счетный вход счетчика 11, Состояние счетчика 11 декодируется дешифратором 12.При записи в счетчик 1 1 числа, , 25 равного числу бит входного слова, на выходе дешифратора 12 формируется сигнал, соответствующий приему всех бит входного слова. Этот сигнал подается на соответствующий вход элемента И 13. После выработки интервала Г на выходе таймера 16 формиру,ется сигнал, который подается на второй выход устройства и свидетельствует об окончании преобразования последовательного код в параллельный, Кроме того, этот сигнал таймера открывает элемент И 13 при наличии сигналов исправности с выходов счетчика 14, дешифратора 12. На выходе элемента И 13 формируется сигнал исправности, который додается на третий выход устройства и свидетельствует о правильности преобразования кода. Пользователь считыва ет паралельный код с выходов регистра 10 при наличии сигналов на выходах элемента И 13 и таймера 16. По окончании преобразования входного слова, т.е. после прекращения формирования импульсов на выходах элемента ИПИ 9, . вновь запускается и срабатывает таймер 15, который обнуляет таймер 16, счетчики 14 и 11.Далее устройство гото во к преобразованию следующего слона.При наличии ошибок, сбоев, потериобит, неправильной четности и т.п. соответствующие счетчики 11 и 14 не 968 4формируют сигналы правильности преоб разования, элемент И 13 остается закрытым и сигнал исправности на выход 20 устройства не выдается.Формула из обретенияПреобразовате.г- последовательного кода в параллельньж содержащий сдви. говый регистр, триггер, элемент ИЛИ, первый элемент И, дешифратор и счетчик, выходы которого подключены к входам дещифратора, выход которого соединен с первым входом первого элемента .И, выходы сдвигового регистра являются первыми выходами преобразователя, о т л и ч а ю щ и й с я тем, что, с целью повьппения достоверности передачи информации, в него введены согласующий трансформатор., первый и второй однополупериодные выпрямители, первый и второй элементы задержки, второй и третий элементы И, первый и второй таймеры и счет - чик по модулю два, вход согласующего трансформатора является входом преобразователя устройства, первый выход согласующего трансформатора через последовательно соединенные первый однополупериодный выпрямитель и первый элемент задержки подключен к первому входу второго элемента И, выход которого соединен с Я-входом триггера и первым входом элемента ИЛИ, второй выход согласующего трансформатора через.последовательно соединенные второй однополупериодный выпрямитель и второй элемент задержки подключен к первому входу третьего элемента И, выход которого соединен с К-входом триггера и вторым входом элемента ИПИ, вторые входы второго и гретьего элементов И соединены с выходами соответственно второго и первого однополупериодных выпрямителей, выход триггера подключен к В-входу сдвигового регистра и первому входу счетчика по модулю два, выход элемента ИЛИ соединен с С-входом сдвигового регистра, входом первого таймера и первым входом счетчика, выход первого таймера подключен к вторым входам счетчика и счетчика по модулю два и через второй таймер соединен с вторым выходом преобразователя и вторым входом первого элемента И, третий вход которого подключен к выходу счетчика по модулю два, а выход является третьим выходом преобразователя.1229968 едактор Н.Егорова Заказ 2460/ полиграфическое предприятие,г,Ужгород,ул.Проектна Производстве ВНИИПИ 1 ос по делам 3035, МОсеСоставитель О.ТюринаТехред Л.Олейник Корректор А.ференц раж 816 о Подписноественного комитета СССРбретений и открытийЖ, Раушская наб., д.4/5

СмотретьЗаявка

3798268, 04.10.1984

ПРЕДПРИЯТИЕ ПЯ А-3706

РУКОДАНОВ ЮРИЙ ПЕТРОВИЧ, ДРУЗЬ ЛЕОНИД ВОЛЬФОВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 07.05.1986

Код ссылки

<a href="https://patents.su/4-1229968-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь кодов

Следующий патент: Устройство для декодирования составного корректирующего кода

Случайный патент: Пломба-запор