Устройство для вычисления функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

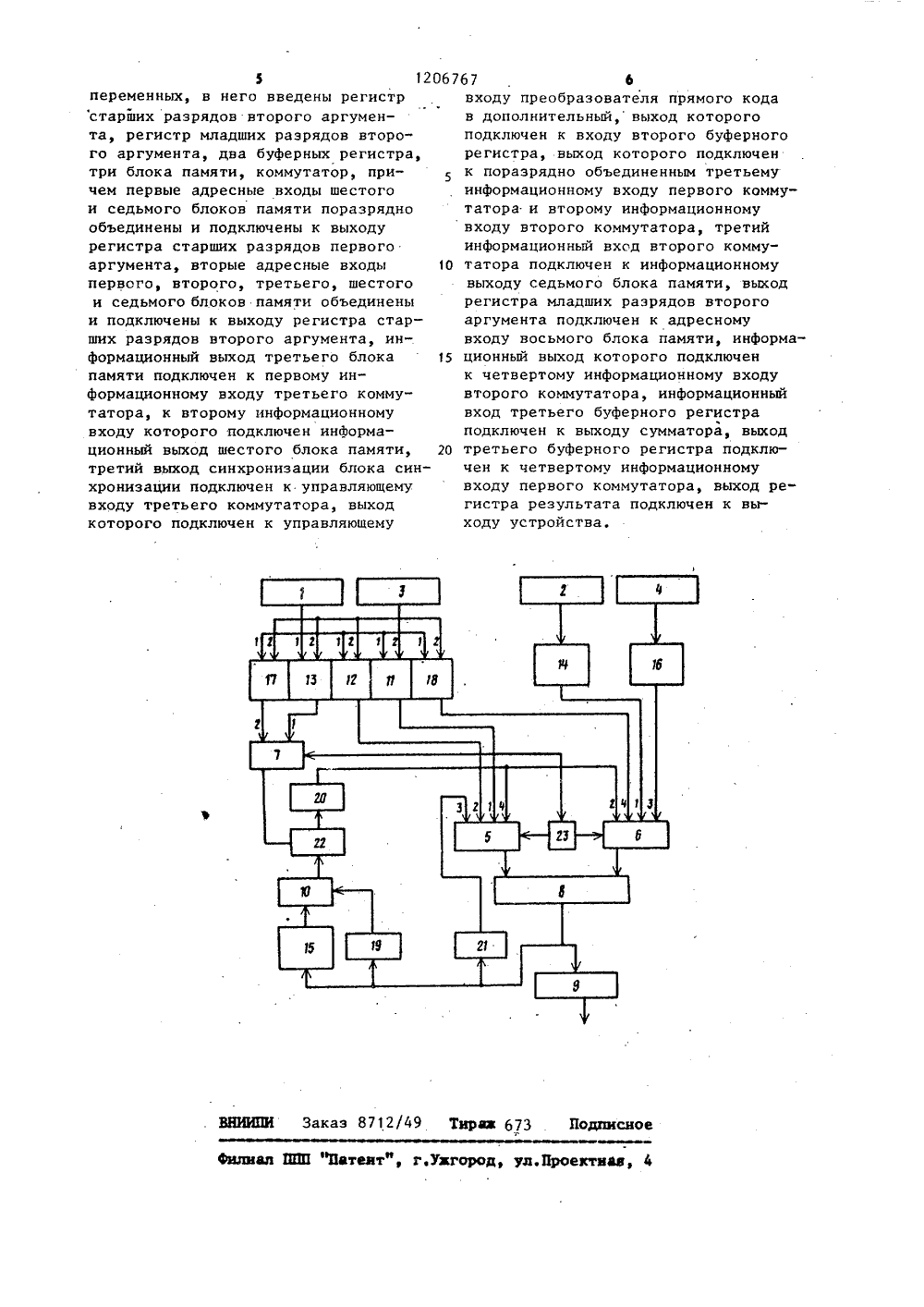

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСН ИХРЕСПУБЛИК 119) (11)15 4 С 06 Р 1/02 ОПИСАНИЕ ИЗОБРЕТЕ ЕТЕЛЬСТВ 21) 3792465/24-2422) 04.07.8446) 23.01.86. Бюл.71) Омский политехнич и инст Потапов ии141304к. 1975.во СССР2, 1980. ЕНИЯ ФУН ся к област может быть ного вычисдвух аргу- Цель изоб циональных ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЬ ТЮ(57) Изобретение относит вычислительной техники и использовано для ускорен ления функций Р (х,у) от ментов в специальных ЭВМ ретения - расширение фун возможностей устройства за счет вычисления функций двух переменных.Устройство содержит регистр старшихразрядов первого аргумента, регистрмладших разрядов первого аргумента,регистр старших разрядов второгоаргумента, регистр младших разрядоввторого аргумента, первый, второйи третий коммутаторы, сумматор,регистр результата, сдвигатель, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой блоки памяти, первый, второй и третийбуферные регистры, преобразовательпрямого кода в дополнительный иблок синхронизации. Вычисление функций двух переменных обеспечиваетсявведением регистров старших и младших разрядов второго аргумента,двух буферных регистров, трех блоков памяти и коммутатора. 1 ил.Изобретение относится к областивычислительной техники и может бытьиспользовано для ускоренного вычисления функций Р (х, у) от двух аргументов в специализированных ЭВМ.Цель изобретения - расширениефункциональных возможностей за счетвычисления функций двух переменных.На чертеже изображена блок-схемапредлагаемого устройства. 1 ОУстройство содержит регистр 1старших разрядов первого аргумента, регистр 2 младших разрядов первого аргумента, регистр 3 старшихразрядов второго аргумента, регистр 4 15младших разрядов второго аргумента,первый, второй и третий коммутаторы 5 - 7, соответственно, сумматор 8,регистр 9 результата, сдвигатель 10,первый, второй, третий, четвертый, . 20пятый, шестой, седьмой и восьмойблоки памяти 11 - 18 соответственно.Кроме того, в состав устройствавходят первый, второй и третийбуферные. регистры 19 - 21, преобразователь 22 прямого кода в дополнительный и блок 23 синхронизации.Устройство вычисляет значенияГ (х, у) функций на основе соотно Г (ха,.со) 30щения Р(х,у)=Р(ху, )+з 18 п(- в г)к) дГ(хц,к фе/,е, е35дегде х ь х определяются со,:.тветственно, старшими и младшими разрядамидвоичного кода первого аргумента х,а у ь определяются соответственностаршими и младшими разрядами двоичного кода второго аргумента ц,х=хо+4 х,=е + ь 1 и погРешностьсоотношения (1) может быть сделана. выходящей за пределы разрядной сеткипутем надлежащего разбиения двоичного кода аргументов на старшие и младшие разряды.Первый, второй, третий, четвертый,пятый, шестой, седьмой и восьмойблоки 11 - 18 памяти хранят таблицыЙР(х, 9 )значений 1 о / - - - ь-о - / 1 ояЛх ф гйГ(хо ц ) аГ(х, ц )о 2 е. 8о,г.дл - 1 оп ьх 2дР(хо ц ) . 558 дА". Р(х ее. ) соот 2 ф э оф;еоЧветственно, где функция Яя определяется соотношением 0 если 20,8 (2)= е1, если 2 с 1,На регистрах старших 1 и младших 2 разрядов первого аргументахранятся соответственно значения хи ьх, а на регистрах старших 3 имладших 4 разрядов второго аргумента хранятся соответственно значения у, и ьу. Преобразователь 22 в зависимости от значения на управляющемвходе передает поступающий на егоинформационный вход двоичный код безизменения, или преобразуя в дополнительный код числа с обратным знаком.Первый,второй и третий буферныерегистры запоминают поступившую наних информацию по концу тактовых импульсов от блока 23 синхронизации.,Устройство для вычисления функцийработает в пять тактов следующим образом. В первом такте по поступающим на входы первого, второго, третьего, седьмого и восьмого блоков 11,12, 13, 17 и 18 памяти значениям паркодов (х у ) в результате выборкина их выходах образуются соответстЙГ(х Уо )венно значения 1 ое / - в ее- )с 1 х/Р (ха ,о ) 1 Г (ходо )с(Г(ху, )Б 8 -- ; - , Р(ху, ), используе 3мые в последующих тактах. Одновременно в первом такте по поступающимна входы четвертого и шестого блоком памяти значениям Ь х и ь у на ихвыходах образуются значения 1 оя ьхи 1 оц ьу.Во втором такте сигналы, поступающие из блока 23 синхронизациина управляющие входы первого ивторого коммутаторов 5 и б, подключают к выходам первые их выходы.Поэтому через первый и второй коммутаторы 5 и 6 на первый и второйвходы сумматора 8 поступают значе( о )ния 1 о/- - г / и 1 оц ьх обраЙх.7 Фзующие на его выходе значение2 =1 оя (/ -- / ь х) целаяе 1 Р(х ео )х г ДхЭчасть 2 х, и дробная часть Ь 2 которого запоминаются в конце такта напервом буферном регистре 19 и навходе пятого блока 15 памяти,В третьем такте сигналы от блока 23 подключают к выходам первого, второго и третьего коммутаторов 5В пятом такте сигналы от блока 23 подключают к выходам первого и второго коммутаторов 5 и 6 третий и второй их входы соответственно. Поэтому на сумматоре 8 происходит сложение значения Р(х у, )+Р из третьего буферного регистра 21 и значения Р с второго буферного регистра 20.3 Результат, равный в соответствии с (1) значению функции Р(х, у), запоминается на регистре 9 результата. Устройство для вычисления функций, содержащее блок синхронизации, сумматор, регистр результата, регистр старших разрядов первого аргумента, регистр младших разрядов первого аргумента, сдвигатель преобразователь прямого кода в дополнительный, два коммутатора, первый буферный регистр, пять блоков памяти, причем выход регистра старших разрядов первого аргумента подключен к поразрядно объединенным первым адресным входам первого, второго и третьего блоков памяти, информационные выходы первого и второго блоков памяти подключены соответственно к первому и второму информационным входам первого коммутатора, выход которого подключен к первому информационному входу сумматора, выход регистра младших разрядов первого аргумента подключен к адресному входу четвертого блока памяти, выход которого подключен к первому информационному входу второго коммутатора, выход которого подключен к второму . информационному входу сумматора, выход которого подключен к поразрядно объединенным входам регистра результата, первого буферного регистра и адресному входу пятого блока памяти, информационный выход которого подключен к информационному входу сдвигателя, управляющий вход которого подключен к выходу первого буферного регистра, выход сдвигателя подключен к информационному входу преобразователя прямого кода в дополнительный, первый и второй выходы синхронизации блока синхронизации подключены соответственно к управляющим входам первого и второго коммутаторов, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей за счет вычислений функций двух 35 50 3 12067677 соответственно второй, третий ипервый их входы. Пятйи блок 15 памяти путем выборки из хранящейсяв нем таблицы значений 2 осуществляет преобразование а 2-2 , резульагтат которого поступает на информационный вход сдвигателя 10, а науправляющий его вход с выхода первого буферного регистра 19 подаетсязначение 2 Сдвигатель 10 сдвигает 1 Оагхзначение 2 на 2 О двоичных разРядов, образуя результат 2 =2а "2 " , который передается через преобразователь 22 кода, учитываюЫ(хуо )щий знак значения -- э-- так как на его управляющий вход через третий коммутатор 7 поступает значейР(х, ч, )ние Бя -- -- . Результат20с 1 Р(х, у, )Р ОАХ ах запоминается в концех с 1 хтакта на втором буферном регистре 20. Одновременно, на первый и второй входы сумматора 8 через первый и второй коммутаторы 5 и 6поступают значения 1 оя / в в в д/ЙР(х, у,)2 Д у и 1 о 8 ьобразующие на его выходес 1 Р(х, УЛзначение 2 =1 о 8 (/ в в -г-с-/а ) 30г 1 д целая часть 2, и дробная часть а"-Укоторого запоминаются по концу такта соответственно на первом буферном регистре 19 и входе пятого бло,ка 15 памяти.В четвертом такте сигналы от олока 23 подключают к выходам первого, второго и третьего коммутаторов 5 7 соответственно четвертый, четвертый и второй их входы. Поэтому на40 первый и второй входы сумматора 8 поступают значения Р и Р(хоУо ) Результат сложения которых Р+Р(хо,у, ) запоминается в конце такта на третьем буферном регистре 21. Одновремен но пятый блок 15 памяти выполняетгавпреобразование а 2 2 сдвигаУ ь 2 Утель 10 путем сдвига 2 " на 2Яодвоичных разрядов формирует значение 2 Упередаваемое через преобразователь 22, на управляющий вход которого через третий коммутатор 7дР(хо уо) поступает значение Зд в в -а - с об 1 УАР(хо Чо ) Раз ованием значения Р = ---- -с 1У запоминаемого на втором буферном регистре 20. Формула изобретения3 12067 переменных, в него введены регистрестарших разрядов второго аргумента, регистр младших разрядов второго аргумента, два буферных регистра, три блока памяти, коммутатор, причем первые адресные входы шестого и седьмого блоков памяти поразрядно объединены и подключены к выходу регистра старших разрядов первого аргумента, вторые адресные входы 1 О первого, второго, третьего, шестого и седьмого блоков памяти объединены и подключены к выходу регистра старших разрядов второго аргумента, информационный выход третьего блока 15 памяти подключен к первому информационному входу третьего коммутатора, к второму информационному входу которого подключен информационный выход шестого блока памяти, 20 третий выход синхронизации блока синхронизации подключен к управляющему входу третьего коммутатора, выход которого подключен к управляющему 67 Ьвходу преобразователя прямого кода в дополнительный, выход которого подключен к входу второго буферного регистра, выход которого подключен к поразрядно объединенным третьему информационному входу первого коммутатора и второму информационному входу второго коммутатора, третий информационный вход второго коммутатора подключен к информационному выходу седьмого блока памяти, выход регистра младших разрядов второго аргумента подключен к адресному входу восьмого блока памяти, информационный выход которого подключен к четвертому информационному входу второго коммутатора, информационный вход третьего буферного регистраЪ подключен к выходу сумматора, выход третьего буферного регистра подключен к четвертому информационному входу первого коммутатора, выход регистра результата подключен к выходу устройства.ВНИИПК Заказ 8712/49 Тираа 673 Подписное филиал ППП ффПатеитфг.Ужгород, уд.Проектирую, 4

СмотретьЗаявка

3792465, 04.07.1984

ОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ФЛОРЕНСОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ПОТАПОВ ВИКТОР ИЛЬИЧ, БЕЛЮТИН ЕВГЕНИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: вычисления, функций

Опубликовано: 23.01.1986

Код ссылки

<a href="https://patents.su/4-1206767-ustrojjstvo-dlya-vychisleniya-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функций</a>

Предыдущий патент: Механизм перемещения курсора

Следующий патент: Устройство для ввода информации

Случайный патент: Пороговое устройство