Устройство для вычисления разности двух чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1179320

Авторы: Грездов, Шимановский, Ярославкин

Текст

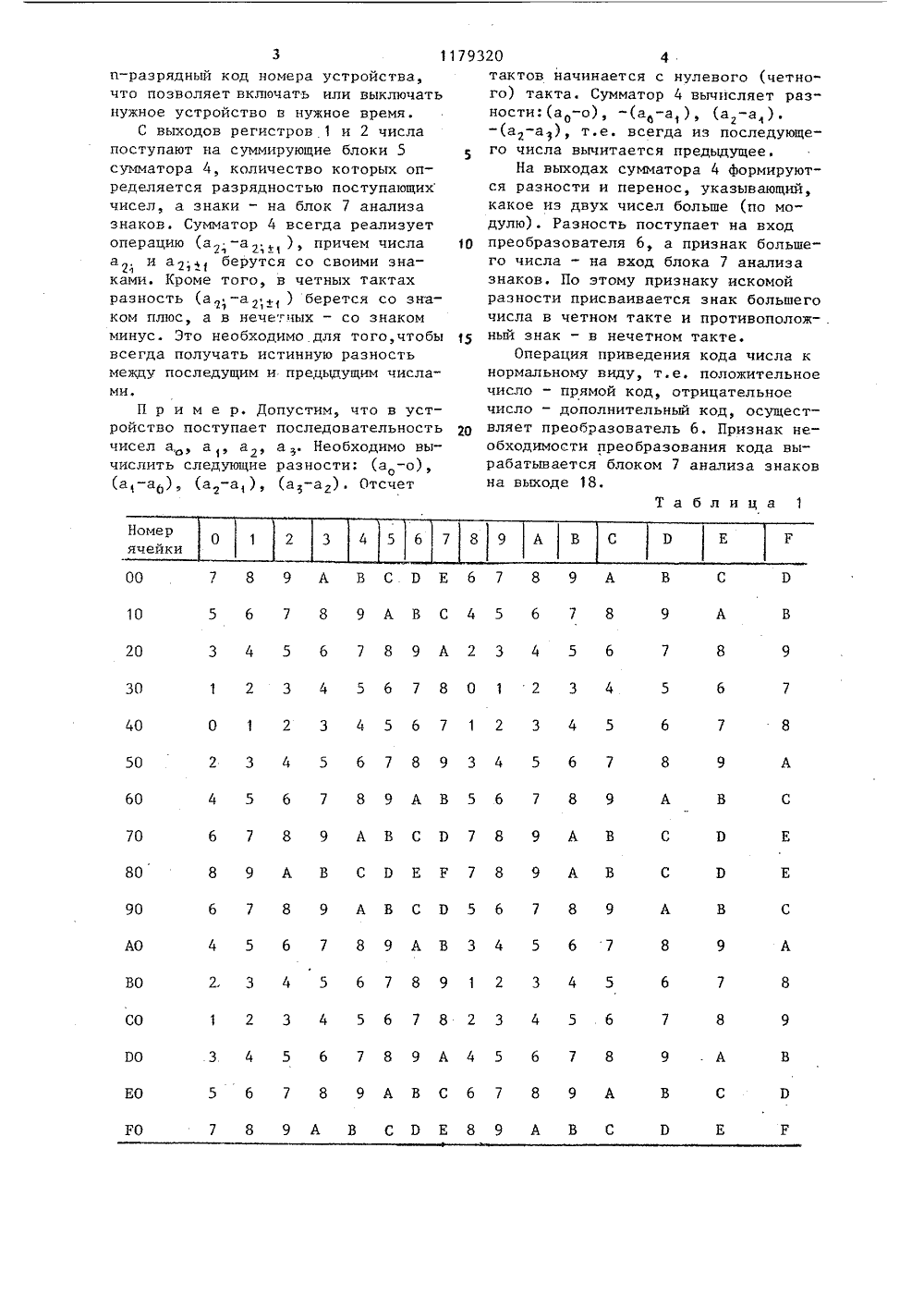

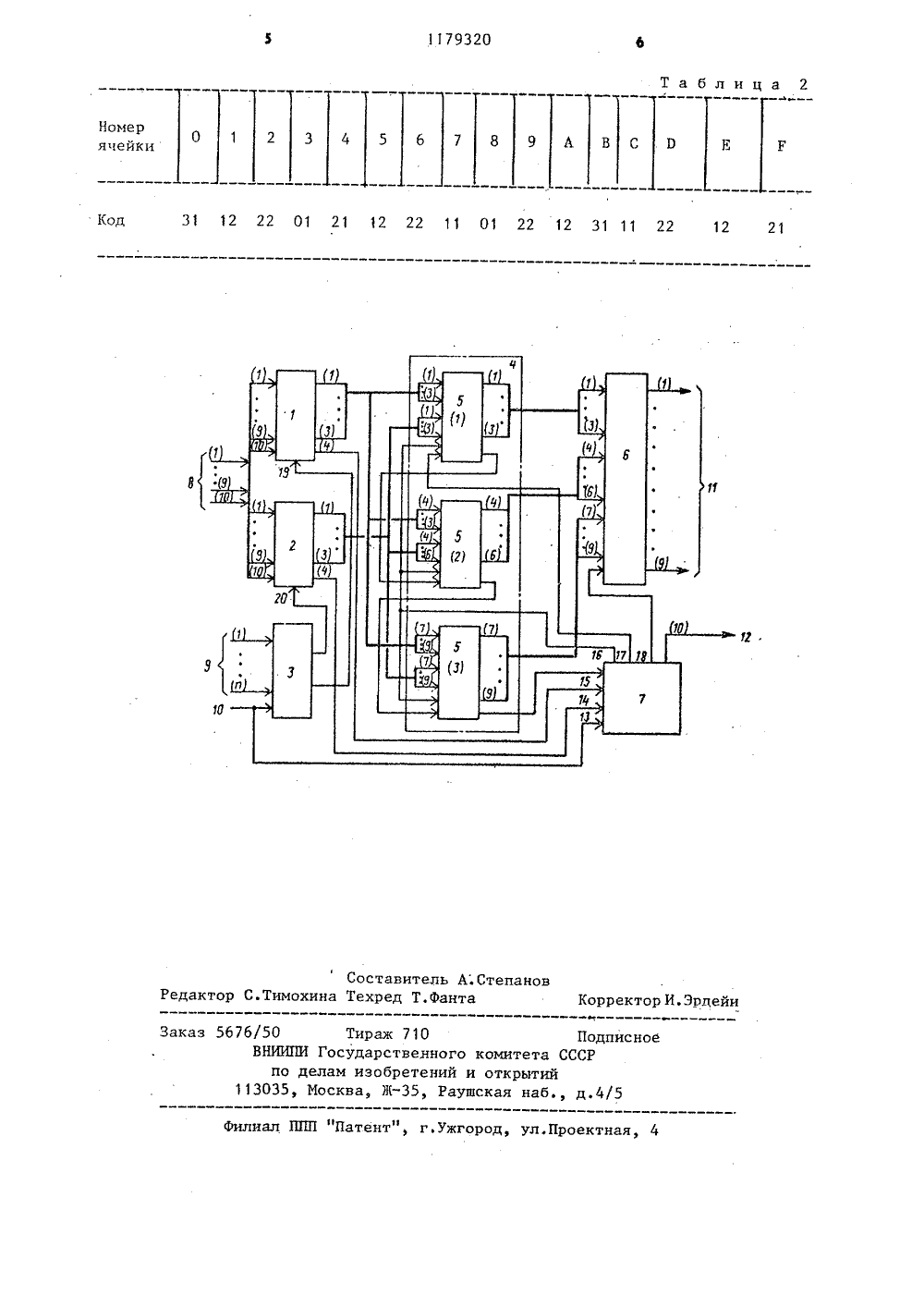

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКРЕСПУБЛИК 51) САНИЕ И ВТОРСНОМ оделир му ро ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРпо делАм изОБРетений и откРытий(71) Институт проблем мованияв энергетике АН УССР(56) Патент США Кд 3424898,кл. 6 06 Р 7/50, опублик. 1969.Карцев М.А. Арифметика цифровыхмашин. М.: Наука, 1969, с. 294,рис. 3-1 а.(54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯРАЗНОСТИ ДВУХ ЧИСЕЛ, содержащее первый и второй регистры, сумматор иблок анализа знаков, причем выходыразрядов регистров соединены с соответствующими разрядами соответственно первого и второго входов сумматора, выходы разрядов знака первогои второго регистров соединены соответственно с первым и вторым входамиблока анализа .знаков, выход переноса сумматора соединен с третьим входом блока анализа знаков, первый выход которого подключен к управляющевходу операции сумматора, а втой - к входу переноса младшего раз.,80117932 ряда сумматора, третий выход блокаанализа знаков соединен с выходомзнака устройства, о т л и ч а ю щ ее с я тем, что, с целью повышениябыстродействия при обработке потокачисел, устройство содержит дешифратор и преобразователь прямого кодав дополнительный, причем входы разрядов первого и второго регистровсоединены с соответствующими разрядами входной шины устройства, входыразрешения записи первого и второгорегистров соединены с соответствующими выходами дешифратора, первыйвход которого соединен с входом номера такта устройства, а остальныевходы соединены с шиной номера устройства, выходы разрядов сумматорасоединены с входами разрядов преобразователя прямого кода в дополнительный, управляющий вход которогосоединен с четвертым выходом блокаанализа знаков, четвертый вход которого соединен с входом номера тактаустройства, выходы разрядов преобразователя прямого кода в дополнительный соединены с соответствующими разрядами выходной шины устройства.1179320 цели. бр 5 р 4 р Зр 2 р 1 р Подаваемая ве- Перенос Код операции Триада кодаличина первого числа Триада кода второгочисла Зр 4 р 2 р Разряды адреса Подаваемаявеличина Вход 10 Вход 15 Вход 14 Вход 13 40дующая . 4 р Зр бр 2 р 1 р Разряд Номер выходаблока 7 16 17 18 12 Изобретение относится к вычислительной технике и может быть использовано при обработке потока чисел, например, в интерполяторах и устройствах вычисления координат. 5Целью изобретения является повышение быстродействия устройства при обработке потока чисел,На чертеже представлена структурная схема устройства для вычисления разности двух чисел для случая вычисления разности десятиразрядных чисел, причем десятый разряд является знаковым.Устройство содержит регистры 1 и 2, дешифратор 3, сумматор 4, состоящий из трех одинаковых трехразрядных суммирующих блоков 5, преобразователь 6 прямого кода в дополнительный и блоканализа знаков, Устройство имеет входную шину 8, шину 9 номера Разряды адреса 8 р 7 Р В табл.1 приведена карта программирования блока постоянной памяти, реализующего блок 5. Номер ячейки и записанный код заданы в 16-ричной системе счисления. Структура выходного кода слеВ табл.2 приведена карта программирования блока постоянной памяти для реализации на нем блока 7. 5 ОУстройство работает следующим образом.На информационные входы регистров 1 и 2 поступает поток чисел, разность между которыми нужно вычислить. Обоз начим последовательность поступающих чисел, как а а , а а;. Эта последовательность чисел сопровожцаетустройства, вход 10 номера такта,выходную шину 11 и выход 12 знака.Блок 7 анализа знаков имеет входы 13и 14, соединенные с выходами разрядовзнака регистров 2 и 1, вход 15, соединенный с выходом переноса сумматора4, и выход 16, подключенный к управляющему входу операции сумматора 4,выход 17, подключенный ко входу младшего разряда сумматора 4 и выход 18,подключенный к управляющему входупреобразователя 6. Регистры 1 и 2имеют входы 19 и 20 разрешения записи. Бло 1 и 5, входящие в состав сумматора 4, могут быть реализованы, например, на базе блока постоянной памяти, Ниже приведена структура адреса блока постоянной памяти для этой Старший разряд выходного кода блока 5 кодирует перенос (заем) в следующий разрядБлок 7 анализа знаков также может быть выполнен на базе блока постоянной памяти. Структура адреса в этом случае следующая: ся признаком того, в каком (четном или нечетном) такте чаходится данное число, Числа, находящиеся в четных тактах - ао, а 2, , а 2 - заносятся в регистр 1, числа, находящиеся внечетных тактах - а 1 у а 35 3 а 2 Ф 1Ъ заносятся в регистр 2. Управляет занес нием чисел в регистры 1 и 2 дешифратор 3, на вход 10 которого подается признак четного или нечетного такта, а на другие входы -1179320 4 Таблица 1 0 1 2 3 4 5 6 7 8ячейки 9 А В С В С 9 А 7 8 5 б 6 7 8 9 7 8 9 А 008 9 А В С 0 Е б 5 6 7 8 5 6 7 8 9 А В С 4 10 3 4 5 6 3 4 5 6 7 8 9 А 2 20 1 2 3 4 1 2 3 4 5 6 7 8 0 30 2 3 4 5 0 1 2 3 4 5 6 7 1 40 4 5 б 7 2 3 4 5 6 7 8 9 3 50 8 9 А В А В С 0 А В С Э 8 9 А В 6 7 4 5 б 7 8 9 А В 5 60 6 7 8 9 А В С Э 7 8 9 70 80 8 9 А В С 0 Е Р 7 8 9 8 9 А В С 0 5 6 7 б 7 90 6 7 8 9 6 7 7 8 6 7 8 9 А В 3 АО 4 5 6 7 8 9 1 4 5 2 3 ВО СО 3 4 5 6 1 2 3 4 5 6 7 8 2 9 . А 3 4 5 6 7 8 9 А 4 5 б 7 8 РО 5 6 7 8 9 А В С 6 В С 0 Е 7 8 9 А ЕО 9 А В С 7 8 9 А В С 0 Е 8 РО и-разрядный код номера устройства, что позволяет включать или выключать нужное устройство в нужное время.С выходов регистров 1 и 2 числа поступают на суммирующие блоки 5 сумматора 4, количество которых определяется разрядностью поступающих чисел, а знаки - на блок 7 анализа знаков. Сумматор 4 всегда реализует операцию (а -а ., ), причем числа а 2. и а;1 берутся со своими знаками. Кроме того, в четных тактах разность (а-а+ ) берется со знаком плюс, а в нечетных - со знаком минус. Это необходимо для того, чтобы всегда получать истинную разность между последущим и прецыдущим числами.П р и м е р, Допустим, что в устройство поступает последовательность чисел а а 1, а, а . Необходимо вычислить следующие разности: (а-о), (а аб) (а а) (а а)Отсчет 5 10 15 20 тактов начинается с нулевого (четного) такта. Сумматор 4 вычисляет разности:(а 0-о), -(ао-а,), (а-а) -(а-а), т.е. всегда из последующего числа вычитается предыдущее,На выходах сумматора 4 формируются разности и перенос, указывающий, какое из двух чисел больше (по модулю). Разность поступает на вход преобразователя 6, а признак большего числа - на вход блока 7 анализа знаков. По этому признаку искомой разности присваивается знак большего числа в четном такте и противоположный знак - в нечетном такте.Операция приведения кода числа к нормальному виду, т.е. положительное число - прямой код, отрицательное число - дополнительный код, осуществляет преобразователь 6. Признак необходимости преобразования кода вырабатывается блоком 7 анализа знаков на выходе 18.1179320 Таблица 2 Номерячейки 0 3 4 Код тг Составитель А;Степанов Редактор С.Тимохина Техред Т.Фанта Корректор И.Эрдейи фЗаказ 5 б 76/50 Тираж 710 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д.4/5

СмотретьЗаявка

3692437, 19.01.1984

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ГРЕЗДОВ ГЕННАДИЙ ИВАНОВИЧ, ШИМАНОВСКИЙ ЮРИЙ ОЛЕГОВИЧ, ЯРОСЛАВКИН ВАЛЕРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: вычисления, двух, разности, чисел

Опубликовано: 15.09.1985

Код ссылки

<a href="https://patents.su/4-1179320-ustrojjstvo-dlya-vychisleniya-raznosti-dvukh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления разности двух чисел</a>

Предыдущий патент: Устройство для фиксации переполнения сдвигателя

Следующий патент: Конвейерное устройство для деления интерационного типа

Случайный патент: Устройство для синтеза оптимальных управляющих