Генератор функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1166148

Автор: Калинин

Текст

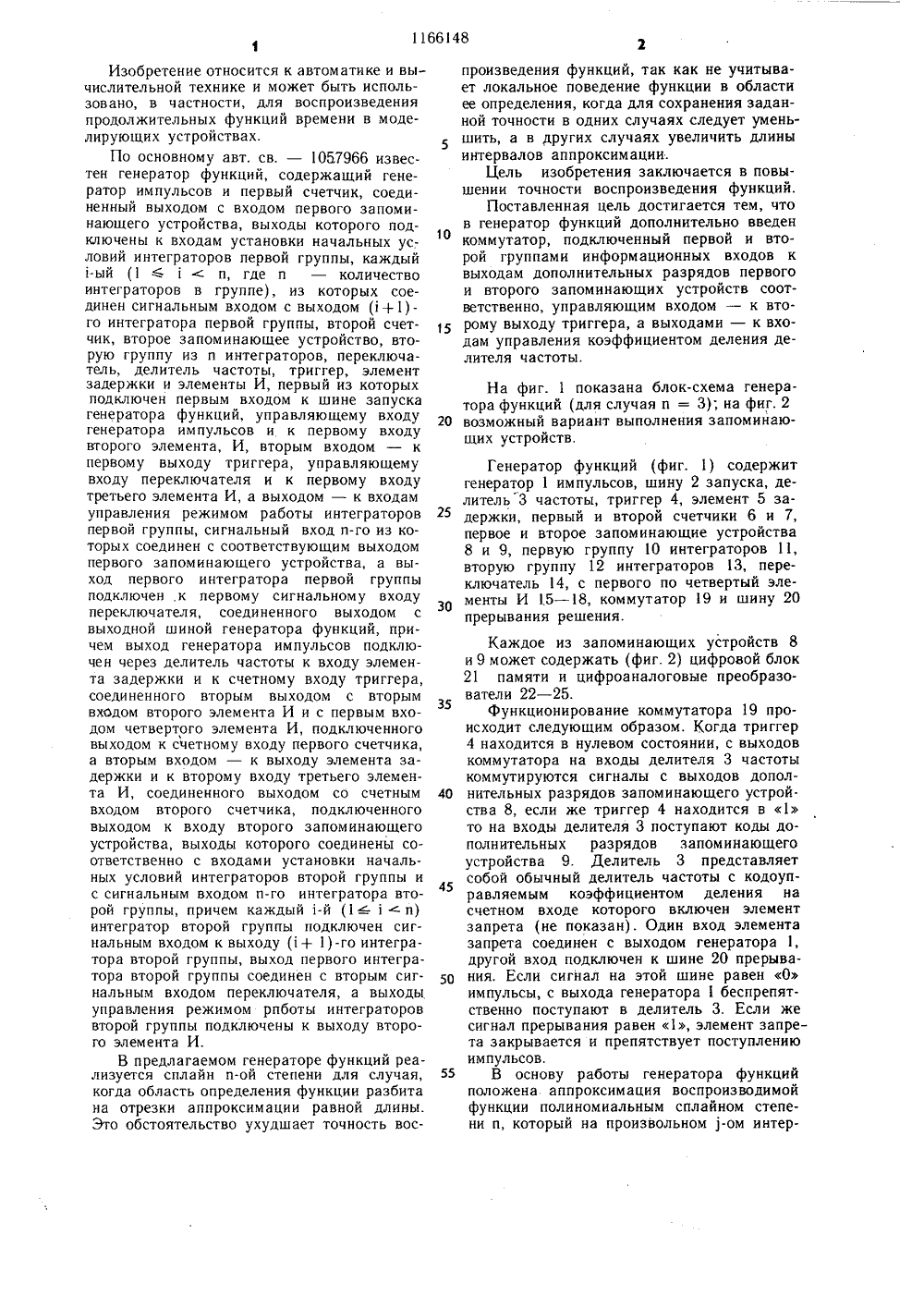

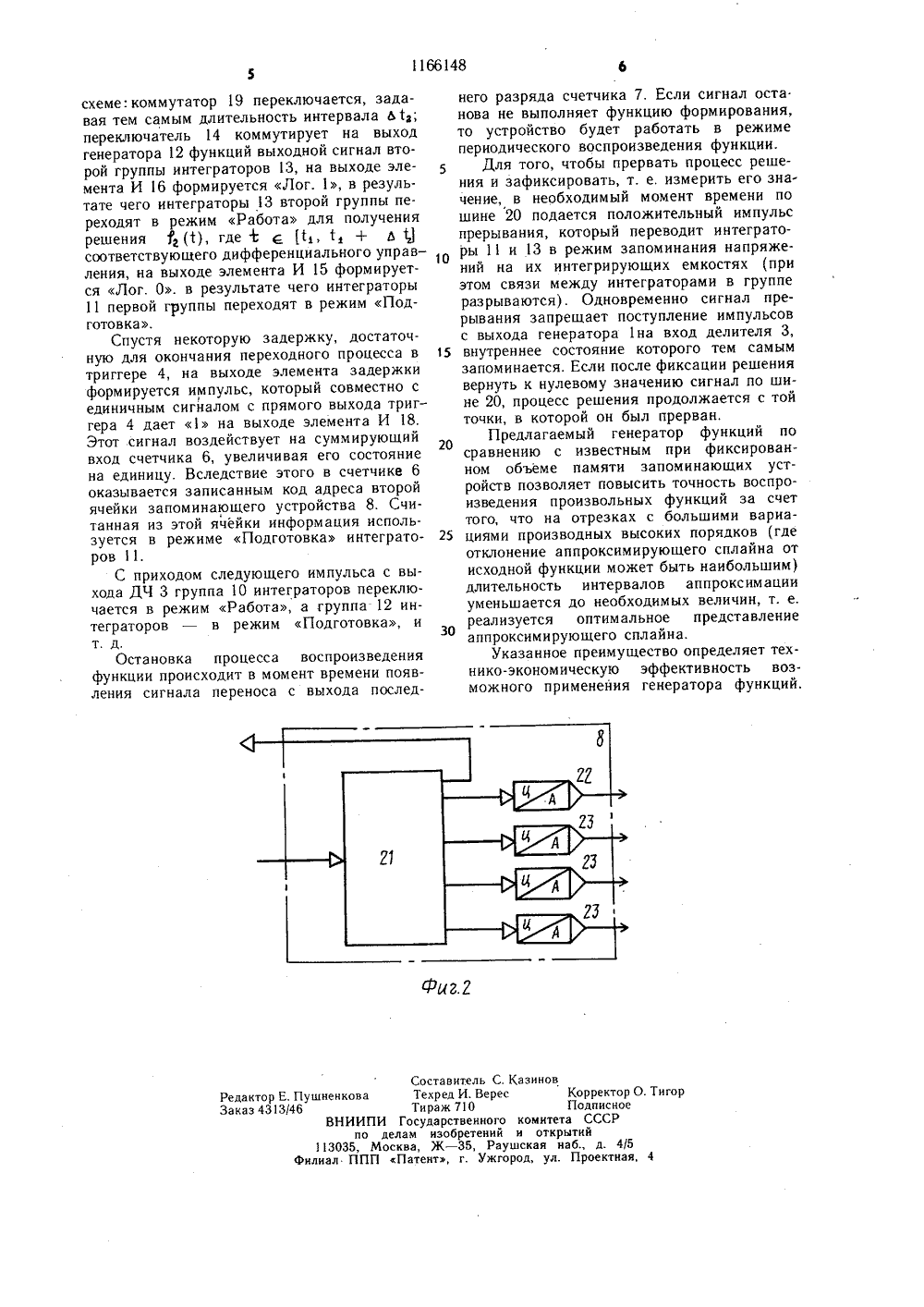

(19) 6 4(511 б 0 ОП ИЕ ИЗОБРЕТЕНИЯ рудового Кра диоэлект 1 оник;Вф ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОРСКОМУ СВИДЕТЕЛЬСТВ(71) Харьковский ордена Т сного Знамени институт раим, акад. М. К. Янгеля(54) (57) ГЕНЕ св.1057966, целью повышен функций, в него мутатор, подкл группами инфор дам дополните второго запоми ственно, управл выходу триггер управления коэ теля частоты. РАТОР ФУНКЦИЙ по авт.отличающийся тем, что, с я точности воспроизведения дополнительно введен комюченный первой и второй мационных входов к выхольных разрядов первого и наюших устройств соответяюшим входом - к второму а, а выходами -- к входам ффициентом деления дели 1166485 10 15 20 25 30 35 40 45 50 55 Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, для воспроизведения продолжительных функций времени в моделирующих устройствах,По основному авт. св. - 1057966 известен генератор функций, содержащий генератор импульсов и первый счетчик, соединенный выходом с входом первого запоминающего устройства, выходы которого подключены к входам установки начальных условий интеграторов первой группы, каждый 1-ый (11 ( п, где и - количество интеграторов в группе), из которых соединен сигнальным входом с выходом (1+1)- го интегратора первой группы, второй счетчик, второе запоминающее устройство, вторую группу из п интеграторов, переключатель, делитель частоты, триггер, элемент задержки и элементы И, первый из которых подключен первым входом к шине запуска генератора функций, управляющему входу генератора импульсов и к первому входу второго элемента, И, вторым входом - к первому выходу триггера, управляющему входу переключателя и к первому входу третьего элемента И, а выходом - к входам управления режимом работы интеграторов первой группы, сигнальный вход п-го из которых соединен с соответствующим выходом первого запоминающего устройства, а выход первого интегратора первой группы подключен,к первому сигнальному входу переключателя, соединенного выходом с выходной шиной генератора функций, причем выход генератора импульсов подключен через делитель частоты к входу элемента задержки и к счетному входу триггера, соединенного вторым выходом с вторым входом второго элемента И и с первым входом четвертого элемента И, подключенного выходом к счетному входу первого счетчика, а вторым входом - к выходу элемента задержки и к второму входу третьего элемента И, соединенного выходом со счетным входом второго счетчика, подключенного выходом к входу второго запоминающего устройства, выходы которого соединены соответственно с входами установки начальных условий интеграторов второй группы и с сигнальным входом и-го интегратора второй группы, причем каждый 1-й (1. - 1и) интегратор второй группы подключен сигнальным входом к выходу (1+ 1) -го интегратора второй группы, выход первого интегратора второй группы соединен с вторым сигнальным входом переключателя, а выходы управления режимом рпботы интеграторов второй группы подключены к выходу второго элемента И.В предлагаемом генераторе функций реализуется сплайн п-ой степени для случая, когда область определения функции разбита иа отрезки аппроксимации равной длины. Это обстоятельство ухудшает точность воспроизведения функций, так как не учитывает локальное поведение функции в области ее определения, когда для сохранения заданной точности в одних случаях следует уменьшить, а в других случаях увеличить длины интервалов аппроксимации.Цель изобретения заключается в повышении точности воспроизведения функций.Поставленная цель достигается тем, что в генератор функций дополнительно введен коммутатор, подключенный первой и второй группами информационных входов к выходам дополнительных разрядов первого и второго запоминающих устройств соответственно, управляющим входом - к второму выходу триггера, а выходами - к входам управления коэффициентом деления делителя частоты. На фиг. 1 показана блок-схема генератора функций (для случая и = 3); на фиг. 2 возможный вариант выполнения запоминающих устройств. Генератор функций (фиг. 1) содержит генератор 1 импульсов, шину 2 запуска, делитель 3 частоты, триггер 4, элемент 5 задержки, первый и второй счетчики 6 и 7, первое и второе запоминающие устройства 8 и 9, первую группу 10 интеграторов 11, вторую группу 12 интеграторов 13, переключатель 14, с первого по четвертый элементы И 15 - 18, коммутатор 19 и шину 20 прерывания решения. Каждое из запоминающих устройств 8 и 9 может содержать (фиг. 2) цифровой блок 21 памяти и цифроаналоговые преобразователи 22 - 25.Функционирование коммутатора 19 происходит следующим образом. Когда триггер 4 находится в нулевом состоянии, с выходов коммутатора на входы делителя 3 частоты коммутируются сигналы с выходов дополнительных разрядов запоминающего устройства 8, если же триггер 4 находится в 1 то на входы делителя 3 поступают коды дополнительных разрядов запоминающего устройства 9. Делитель 3 представляет собой обычный делитель частоты с кодоуправляемым коэффициентом деления на счетном входе которого включен элемент запрета (не показан). Один вход элемента запрета соединен с выходом генератора 1, другой вход подключен к шине 20 прерывания. Если сигнал на этой шине равен О импульсы, с выхода генератора 1 беспрепятственно поступают в делитель 3. Если же сигнал прерывания равен 1, элемент запрета закрывается и препятствует поступлению импульсов.В основу работы генератора функций положена аппроксимация воспроизводимой функции полиномиальным сплайном степени и, который на произвольном 1-ом интер,+ ,вале аппроксимации длины д 11имеет вид вз, -где аз,О 1,л(коэффициенты сплайна;С; - значение левой границы интервала аппроксимации.Степень сплайна определяется числом последовательно соединенных интеграторов в группах 10 и 12. На фиг. 1 изображена схема генератора функций для случая воспроизведения кубических сплайнов. Длина ь 1 каждого интервала аппроксимации регулируется путем изменения коэффициента деления делителя 3. При заданных значениях коэффициентов афункции (1) и единичных коэффициентах передачи интеграторов 11 и 13 на сигнальные входы первых интеграторов каждой группы должно подаваться напряжение, пропорциональное Ьы= (-1)" иа" а на входы установи начальных условий интеграторов напряжение, пропорциональное Ь 1= (-1)1" 1 а 1, где 1 - текущий порядок производной на выходе интегратора относительной функции(1).Первая группа 10 интеграторов 11, запоминающее устройство 8 и счетчик 6 предназначены для воспроизведения сплайна на всех нечетных интервалах аппроксимации, а блоки 7, 9 и 12 - на четных интервалах аппроксимации,Каждый из интеграторов 11 и 13 имеет три режима функционировании: Подготовка, Работа и Прерывание. Переход из одного режима в другой происходит при изменении двоичных переменных на управляющих входах интеграторов 11 и 13. Если на шине 20 и выходах элементах И 15 и 16 сформирован Лог. О, то реализуется режим Подготовка, при котором входные цепи интеграторов разрываются и осуществляется заряд интегрирующих емкостей до тех значений напряжений начальных условий, которые устанавливаются на выходах запоминающих устройств.В режиме Работе на выходе элемента И 15/ИЛИ 16 устанавливается Лог, 1, При этом входные цепи интеграторов замыкаются, что фактически означает решение неоднородного дифференциального уравнения и-го порядка с заданными начальными условиями.Переход из режима Работа в режим Прерывание происходит при поступлении Лог. 1 по шине 20. В этом режиме интегрирующие емкости в цепях обратной связи интеграторов сохраняют те напряжения, которые сформировались на них к моменту подачи сигнала прерывания.Выходная шина генератора функций связана с выходом переключателя 14. Логи 5 1 О5 ка работы переключателя такова: если двоичный сигнал на его управляющем входе равен , то на выход переключателя коммутируется напряжение с выхода группы 10 интеграторов 11; в противном случае на выход переключателя коммутируется напряжение с выхода группы 12 интеграторов 13.Непосредственно перед началом формирования заданной функции времени на устройство подается сигнал Начальная установка, который обнуляет делитель 3, триггер 4, счетчики 6 и 7, а также разрешает считывание информации из запоминающих устройств 8 и 9. Теперь в счетчиках 6 и 7 будет сформирован код адреса первой ячейки, который воздействует на адресные входы цифровых блоков памяти 21. В результате этого происходит считывание информации из первых ячеек блоков 2 цифровой памяти на цифровые входы преобразователей 22 - 25, а также на информационные входы коммутатора 19.Каждый из преобразователей 22 - 25преобразует код соответствующего коэффициента в пропорциональное ему 25напряжение с требуемым знаком. Поскольку сигнал запуска по шине 2 отсутствует, то на выходах элементов И 15 и 16 формируются нулевые двоичные сигналы, которые переводят в режим Подготовка все интеграторы, интегрирующие емкости кото рых (не показаны) заряжаются до напряжений начальных условий. При этом на выходной шине генератора функций появляется напряжение, пропорциональное 1(0), поскольку переключатель 14 коммутирует на выход напряжение с восхода первой группы 10 интеграторов 11.В связи с тем, что на втором инверсном выходе триггера 4 сформирован сигнал Лог. 1, коммутатор 20 коммутирует на входы управления коэффициентом деле ния делителя 3 цифровой код с выхода запоминающего устройства 8. Тем самым задается д 1, - длительность первого интервала аппроксимации.С поступлением по шине 2 сигнала запуска включается генератор 1, выходные сиг налы которого воздействуют на делитель 3.Одновременно сигнал запуска формирует 1 на выходе элемента И 15, в результате чего первая группа 10 интеграторов 11 переводится в режим Работа. При этом входные цели интеграторов замыкаются и образуется аналоговая вычислительная система для решения соответствующего дифференциального управления при заданных начальных условиях на первом интервале 1 е О, д.55 Спустя время д 1, на выходе делителя 3появляется импульс, который устанавливает в 1 триггер 4. Последнее обстоятельство влечет за собой следующие изменения в1166148 Фиг.2 Составитель С. КазиновТехред И. Верес Корректор О. ТигорТираж 710 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж - 35, Раушская наб., д. 4/оФилиал ППП Патент, г. Ужгород, ул. Проектная, 4 Редактор Е. Пушненкова Заказ 4313/46 схеме:коммутатор 19 переключается, задавая тем самым длительность интервала 61 а; переключатель 14 коммутирует на выход генератора 12 функций выходной сигнал второй группы интеграторов 13, на выходе элемента И 16 формируется Лог. 1, в результате чего интеграторы 13 второй группы переходят в режим Работа для получения решения Х (1), где Ь1 1+ Ь Ц соответствующего дифференциального управления, на выходе элемента И 15 формируется Лог. О. в результате чего интеграторы 11 первой группы переходят в режим Подготовка.Спустя некоторую задержку, достаточную для окончания переходного процесса в триггере 4, на выходе элемента задержки формируется импульс, который совместно с единичным сигналом с прямого выхода триггера 4 дает 1 на выходе элемента И 18, Этот сигнал воздействует на суммирующий вход счетчика 6, увеличивая его состояние на единицу. Вследствие этого в счетчике 6 оказывается записанным код адреса второй ячейки запоминающего устройства 8. Считанная из этой ячейки информация используется в режиме Подготовка интеграторов 11.С приходом следующего импульса с выхода ДЧ 3 группа 10 интеграторов переключается в режим Работа, а группа 12 интеграторов - в режим Подготовка, и т, д.Остановка процесса воспроизведения функции происходит в момент времени появления сигнала переноса с выхода последнего разряда счетчика 7. Если сигнал оста.нова не выполняет функцию формирования, то устройство будет работать в режиме периодического воспроизведения функции.Для того, чтобы прервать процесс решения и зафиксировать, т. е. измерить его значение, в необходимый момент времени по шине 20 подается положительный импульс прерывания, который переводит интеграторы 11 и 13 в режим запоминания напряжений на их интегрирующих емкостях (при этом связи между интеграторами в группе разрываются). Одновременно сигнал прерывания запрещает поступление импульсов с выхода генератора 1 на вход делителя 3, 15 внутреннее состояние которого тем самымзапоминается. Если после фиксации решения вернуть к нулевому значению сигнал по шине 20, процесс решения продолжается с той точки, в которой он был прерван.Предлагаемый генератор функций посравнению с известным при фиксированном объеме памяти запоминающих устройств позволяет повысить точность воспроизведения произвольных функций за счет того, что на отрезках с большими вариа циями производных высоких порядков (гдеотклонение аппроксимирующего сплайна от исходной функции может быть наибольшим) длительность интервалов аппроксимации уменьшается до необходимых величин, т. е.реализуется оптимальное представление 30аппроксимирующего сплаина.Указанное преимущество определяет технико-экономическую эффективность возможного применения генератора функций.

СмотретьЗаявка

3694534, 20.01.1984

ХАРЬКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ РАДИОЭЛЕКТРОНИКИ ИМ. АКАД. М. К. ЯНГЕЛЯ

КАЛИНИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06G 7/26

Опубликовано: 07.07.1985

Код ссылки

<a href="https://patents.su/4-1166148-generator-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор функций</a>

Предыдущий патент: Функциональный преобразователь

Следующий патент: Устройство для определения момента изменения свойств случайного процесса

Случайный патент: 336420