Дифференциальный кодер модулятора

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1075428

Автор: Антонов

Текст

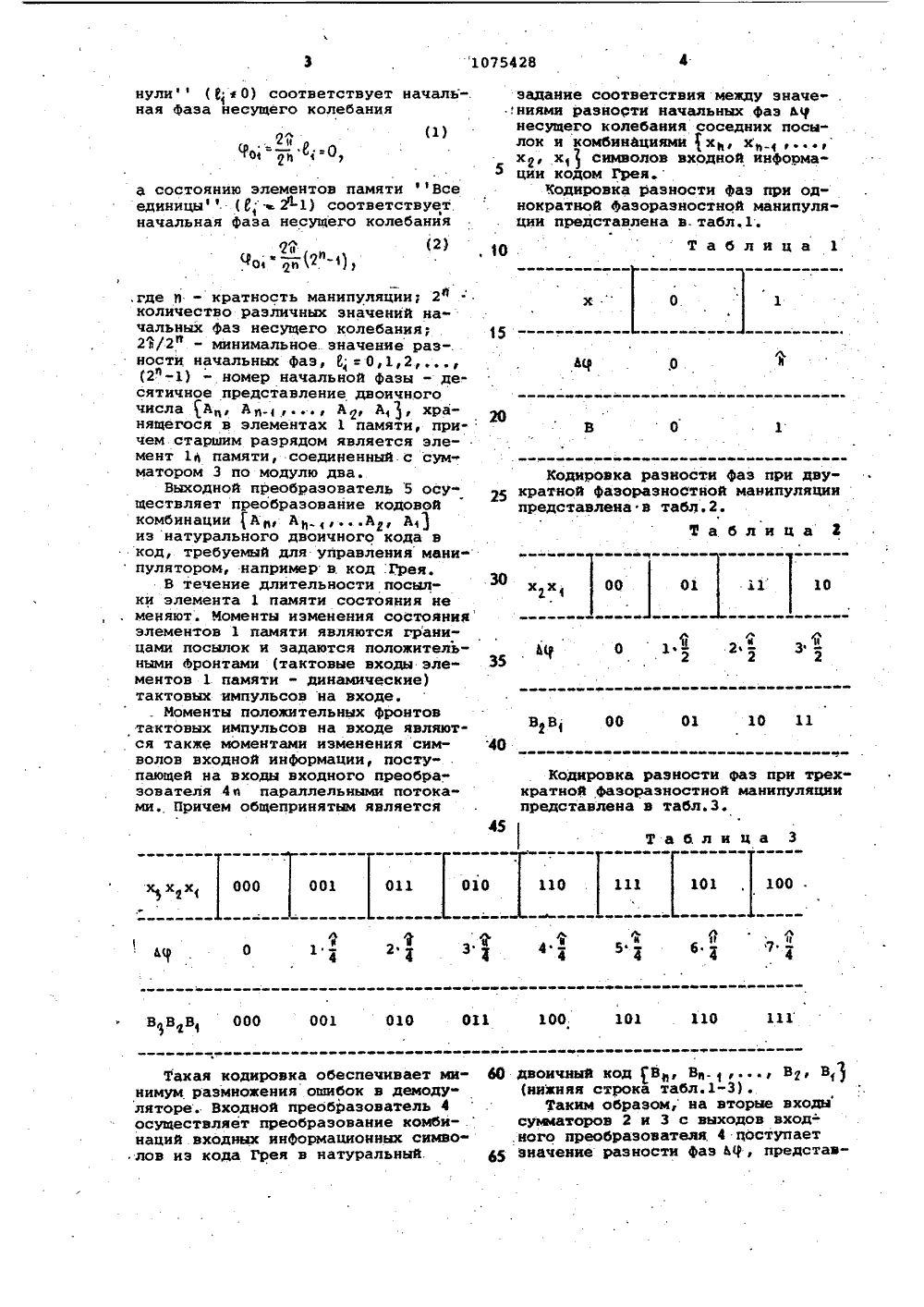

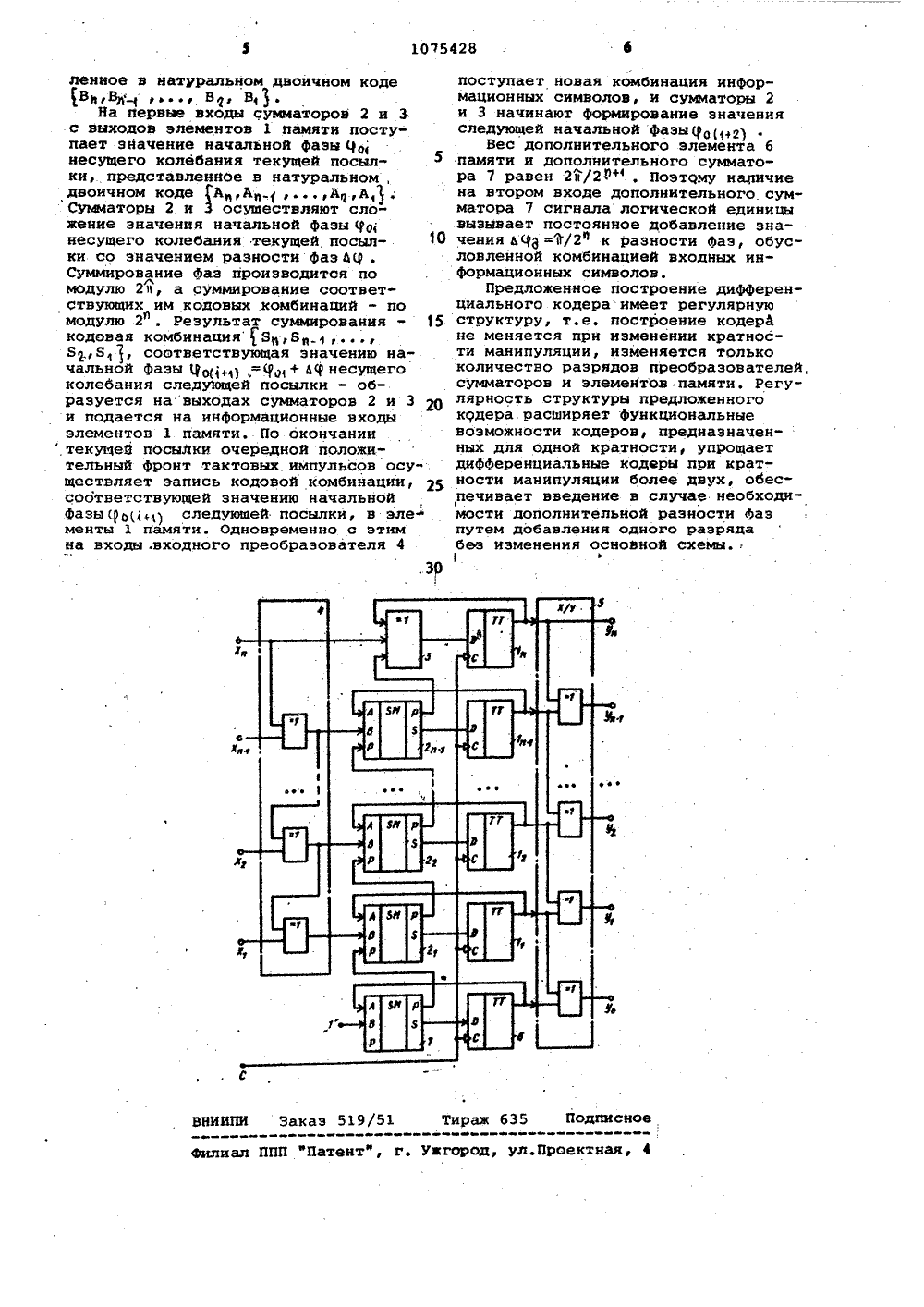

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК А ао 2 4 ОЛИСАНИ К АВТОРСКОМУ ИЗОБРЕТЕИДЕТЕЛЬСТВУ . тейу УДАРСТВЕННЫЙ КОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТЙРЫТИЙ(71) Ленинградский электротехнический институт связи им. проФ. М.А.Бонч-Бруевича(56) 1. Авторское свидетельство СССР 9 331496, кл. Н 04 Ь 3/04, 1972.2. Цифровое телевидение. Под ред. М,И.Кривошеева. М Связь, 1980, с.72-73 (прототип).(54)(57)1.ДИФФЕРЕНЦИАЛЬНЫИ КОДЕРМОДУЛЯТОРА, содержащнй элемент памяти и сумматор по модулю два, первый вход и выход которого соединены соответственно с выходом и входом элемента памяти, о т л и ч а ю - щ и й с я тем, что, с целью расширения Функциональных возможнос путем увеличения кратности манип ляции, введены (п) элементов памяти, (и -1) сумматоров, входной преобразователь кода Грея в натуральный двоичный код и выходной преобразователь натурального двоичного кода, при этом первый вход и выход каждого из (П"1) сумматоров соединены соответственно с выходом и входом соответствующего элемента памяти, выход переноса каждого м -го сувеатора (где ка 1,2, я) соединен с входом переноса (1+1) сумматора, вторые входы сум матора по модулю два и (и) сумматоров соединены с выходами соответствукицих разрядов входного преобразователя кода Грея в натуральный двоичный код, выходы И элементов памяти соединены с входами соответствукицих разрядов выходногопреобразователя натурального двоичного кода, причем выход переноса(Ь) сумматора подключен к дополнительному входу суьваатора по модулю два, а.тактовые входы и элементов памяти объединены и являютсявходом тактового сигнала.2. Кодер модулятора по п.1,о т л и ч а ю щ и й с я тем; чтос целью обеспечения дополнительного 8сдвига фазы модулированного сигнала,введены дополнительные элемент памяти и сумматор, при этом первый входи выход дополнительного сумматорасоединены соответственно с выходоми входом дополнительного элемента Япамяти, выход которого подключенк входу дополнительного. разряда входного преобразователя натурального двоичного кода, выход переноса дополнительного сумматора сое- (динен с входом переноса первого сумматора, второй вход дополнитель-,ного сумматора является входом сиг- С 73нала ф 1., а тактовый вход допол- ф,нительного элемента памяти объеди,нен с соответствующим входом перво- СЪФго элемента памяти. ООИзобретение относится к области связи и может быть использовано для перехода от абсолютного кодирова" иия символов входной информации к от носительному в модуляторах с )1 -кратной Фазораэностной манипуляцией.Известны двукратный дифференциальный кодер. модулятора, содер" жащий два элемента памятии два сумматора по модулю два, выходы которых соединены с входайи соответствующих элементов памяти, первые входы сумматоров ло модулю два соединены с информационными входами устройства через соответствующие элементы совпадения, выходы элементовсовпадения соединены с входами третьего сумматора по модулю два, выход которого соединен с входом делителя на два, выходы которого соединены с вторыми входами сумматора по модулю два 11 .Недостатком данного дифференциального кодера является невозможность его использования при увеличении кратности манипуляции.Наиболее близким техническим решением к изобретению является дифференциальный кодер модулятора, содержащий элемент памяти и сумматор по модулю два, первый вход и выход которого соединены соответственно с выходом и входом элемента памяти, второй вход сумматора по модулю два является информационным входом., а выход элемента памяти выходом дифференциального кодера модулятора 2).Недостатком известного дифференциального кодера модулятора является невомзожность его использования при увеличениикратности манипуляции, что сужает его Функциональные воэможности, а также невозможность обеспечения дополнительного сдвига Фазы модулированного сигнала при передаче длинных последова-тельностей нулей.Цель изобретения - расширение Функциональных возможностей путем увеличения кратности манипуляции и обеспечение дополнительного сдвига Фазы модулированного сигнала.С этой целью в дифференциальный кодер модулятора, содержащий элемент памяти и сумматор по модулю два, первый вход и выход которого соединены соответственно с выходом и входом элемента памяти, введены И) элементов памяти, (й"1) сумматоров, входной преобразователь кода Грея в натуральный двоичный код и выходной преобразователь натурального двоичного кода, при этом первый вход и выход каждого из (ц-.1) сумматоров соединены соответственно с выходом и входом соответствую щего элемента памяти, выход переноса каждого К -го сумматора (где1=1,2,Ь) соединен с входомпереноса (К+1) сумматора, вторые 5входы сумматора по модулю два и(П) сумматоров соединены с выходами соответствующих разрядов входного преобразователя кода Греяв натуральный двоичный код, выходыО элементов памяти соединены с 0.входами соответствующих разрядов выходного преобразователя натурального двоичного кода, причем выходпереноса (й) сумматора подключен кдополнительному входу сумматора по (5 модулю два, а тактовые входы п элементов памяти объединены и являютсявходом тактового сигнала. Кроме того, в кодер модулятора 20 введены дополнительные элемент памяти и сумматор, при этом первыйвход и выход дополнительного сумматора соединены соответственно свыходом и входом дополнительного 25 элемента памяти, выход которогоподключен к входу дополнительногоразряда выходного преобразователянатурального двоичного кода, выход переноса дополнительного сумматора соединен с входом переносапервого сумматора, второй входдополнительного сумматора является входом сигнала 11, а тактовы вход дополнительного элемента памяти объединен с соответствующим входом первого элемента памяти. 40 45 50 55 60 65 На чертеже представлена струк,турная электрическая. схема дифференциального кодера модулятора.Дифференциальный кодер модулятора содержит О элементов 1 памяти ( 11 17 1 в), (0-1) суюиаторов 2 (2,27,;2 . ), сумматор 3 по модулюдва, входной преобразователь 4 кода Грея в натуральный двоичный код, выходной преобразователь 5 натурального двоичного кода, дополнительный элемент б памяти и дополнительный сумматор 7. Дифференциальный кодер модулятора работает следующим образом.Совокупность состояний Ь элементов 1 памяти на текущей посылке определяет значение начальной фазы колебания несущей частоты на текущей посылке, так как выходы дифференциального кодера являются управляющими входами манипулятора Фаз несущего колебания. Элементы 1 памяти хранят информацию о начальйой Фазе Цщ несущего колебания текущей посылки в натуральном двоичном коде А, А,нФ 7 ф Ь 1 Состоянию элементов 1 памяти Все(нижняя строка табл.1-3).Таким образом, на вторые входисуавюаторов 2 и 3 с выходов вход-.ного преобразователя 4 поступаету значение разности фаз Щ , представнули (0) соответствует началь-ная фаза несущего колебания а состоянию элементов памяти фВсеединицы. ( 2 ф 1) соответствуетначальная Фаза несущего колебаниядв (2)Ч 0; " - 2"-1) ).где И - кратность манипуляции; 2 Зколичество различных значений начальных Фаз несущего .колебания;2/2" - минимальное. значение разности начальных Фаз, 3 ф 0,12.(2 -1) - номер начальной фазы - десятичное представление двоичногочисла ААп,А, А хранящегося в элементах 1 памяти, причем старшим разрядом является элемент 1 памяти, соединенный с сумматором 3 по модулю два.Выходной преобразователь 5 осуществляет преобразование кодовойкомбинации Ая, А ,А, А,из натурального двоичного кода вкод, требуемый для управления манипулятором, например в, код:Грея.В течение длительности посылки элемента 1 памяти состояния неменяют. Моменты изменения состоянияэлементов 1 памяти являются границами посылок и задаются положительными фронтами (тактовые входы элементов 1 памяти - динамические)тактовых импульсов на входе.. Моменты положительных фронтовтактовых импульсов на входе являются также моментами изменения символов входной информации, поступающей на входы входного преобразователя 4 а параллельными потоками. Причем общепринятым является Такая кодировка обеспечивает минимум размножения ошибок в демодуляторе. Входной преобразователь 4 осуществляет преобразование комбкнаций. входных информационных символов иэ кода Грея в натуральный. задание соответствия между значе- . ,ниями разности начальных фаэ ау несущего колебания соседних посылок и комбинациями хк, х 1 х, х символов входной информации кодом Грея.Кодировка разности фаз при однократной Фазоразностной манипуляции представлена в.табл.1. Кодировка разности Фаз при дву 25 кратной фазоразностной манипуляцки представлена в табл.2. Т а б л и ц а 3Кодировка разности фаз при трехкратной фазоразностной манипуляции представлена в табл.З.1075428 зр Тираж 635 Подписное Заказ 519/ д, ул.Проектная, 4 иал ППП фПатент У ленное в натуральном двоичном кодев,в, в, в, .На первые входы сумматоров 2 и 3 с выходов элементов 1 памяти поступает значение начальной Фазы Ц; несущего колебания текущей посылки, представленное в натуральном, двоичном коде А,Аэ. ,АцА,Сумматоры 2 и 3 осуществляют сложение значения начальной фазы о; несущего колебания текущей посылки со значением разности фаз АЩ . Суммйрование Фаз производится полмодулю 2 и, а суммирование соответствующих им кодовых, комбинаций - по модулю 2 . Результат суммирования - 15Йкодовая комбинация 88 эВ,Я, соответствующая значению начальной фазы Щ +1 =(ц, + ьф несущего колебания следующей посылки - образуется на выходах сумматоров 2 и 3 20 и подается на информационные входы элементов 1 памяти. По окончании ,текущей посылки очередной положительный Фронт тактовых. импульсов осуществляет запись кодовой комбинации, соответствующей значению начальной Фазы Чьдч следующей посылки, в элементы 1 памяти. Одновременно с этим на входы .входного преобразователя 4 поступает новая комбинация информационных символов, и сумматоры 2 и 3 начинают Формирование значения следующей начальной Фазы до ,21Вес дополнительного элемента б памяти и дополнительного сумматора 7 равен 2 п/26 ф, Поэтому наличие на втором входе дополнительного сумматора 7 сигнала логической единицы вызЫвает постоянное добавление значения а 9 =Ъ/2 я к разности Фаз, обусловленной комбинацией входных инФормационных символов.Предложенное построение дифференциального кодера имеет регулярную структуру, т.е. построение кодерА не меняется при изменении кратности манипуляции, изменяется только количество разрядов преобразователей, сумматоров и элементов памяти. Регулярность структуры предложенного кодера расширяет функциональные воэможности кодеров, предназначенных для одной кратности, упрощает дифференциальные кодеры при кратности манипуляции более двух, обеспечивает введение в случае необходимости дополнительной разности Фаз путем добавления одного разряда без изменения основной схемы.:Ь

СмотретьЗаявка

3311833, 23.06.1981

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

АНТОНОВ ГЕННАДИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04L 3/02

Метки: дифференциальный, кодер, модулятора

Опубликовано: 23.02.1984

Код ссылки

<a href="https://patents.su/4-1075428-differencialnyjj-koder-modulyatora.html" target="_blank" rel="follow" title="База патентов СССР">Дифференциальный кодер модулятора</a>

Предыдущий патент: Устройство для контроля чувствительности радиоприемника

Следующий патент: Многоканальная система передачи двоичной информации с временным уплотнением

Случайный патент: Сепаратор для отделения жидкости отгаза