Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 995091

Автор: Соколов

Текст

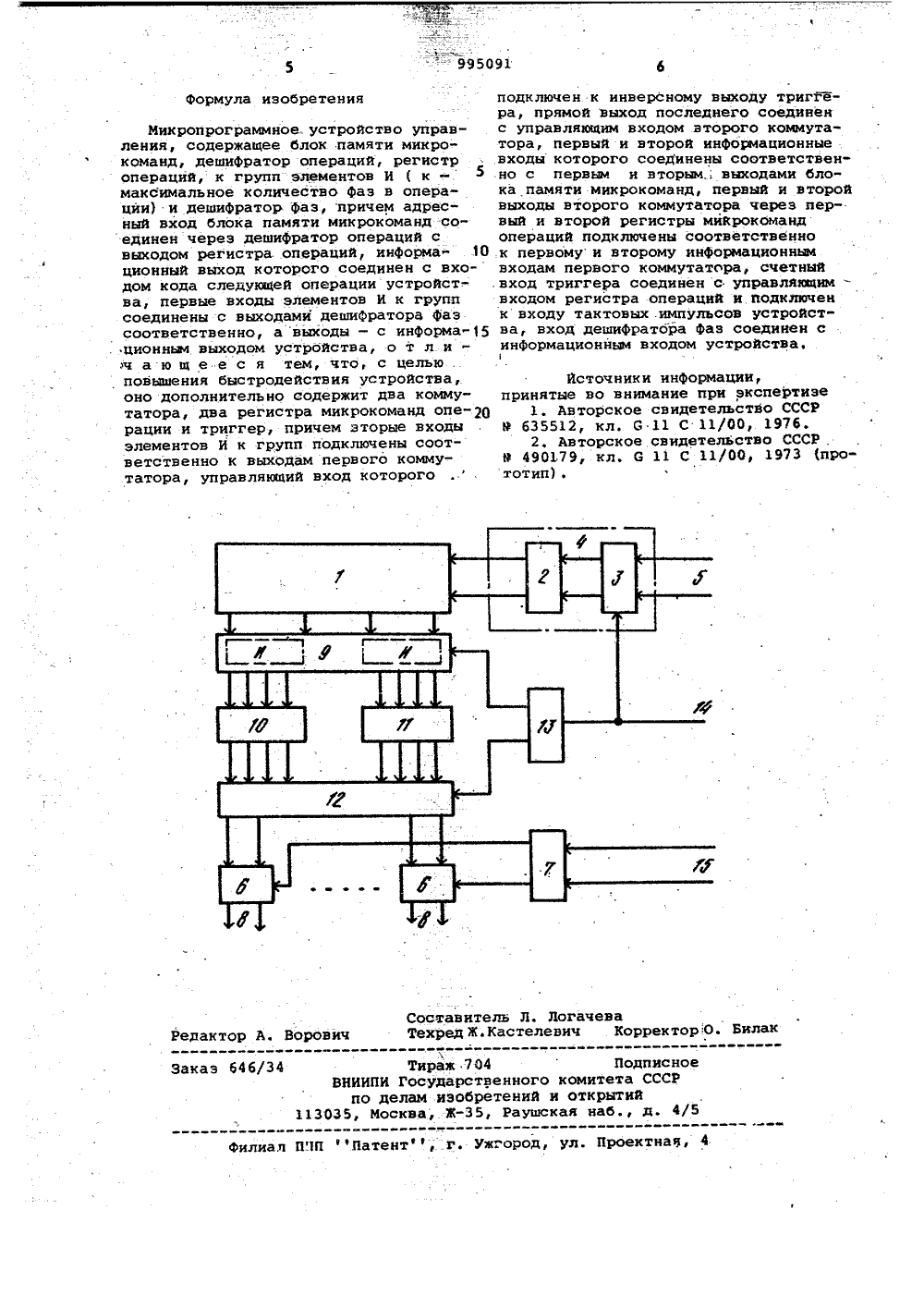

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п 995091 Союз СоветскикСециалистическихРеспублик(ИМ Кл з 0 06 Р 9/22 с присоединением заявки Ио Государственный комитет СССР по делам. изобретений и открытийОпубликовано 07.0283. Бюллетень М 5 Дата опубликования описания 07,0233(54) МИКРОПРОГРАММНОЕ УСТРОИСТВОУПРАВЛЕНИЯ Изобретение относится к вычислительной технике и может быть использо-.вано в микропрограммных устройствахуправления. 5Известно запоминающее устройствомикрокоманд, содержащее накопительмикрокоманд, коммутаторы, дешифраторфаз операций, Формирователь адреса,счетчик фаз операций и накопитель эа- рщиты фазы операции (1,Недостатком устройства является то,что быстродействие его работы такжеопределяется временем обращения к накопителю за выбором микрокоманд длявыполняемой операции, что не позволяет использовать его в составе быст. родействующих ЦВМ.Наиболее близким по техническойсущности и предлагаемому являетсязапоминакщее устройство микрокоманд,которое содержит накопитель, адресные шины которого связаны через дешифратор операций и регистр операцийформирователя адреса с первьаки входа-.ми запоминающего устройства микрокоманд, первые выходы .накопителя соединены с соответствующими входамик-групп коммутаторов, вторые выходыкоторого соединены через дешифраторфаз с управляющими входами к-групп ЗО коммутаторов, выходы которого являются выходами запоминающего устрой" ства микрокоманд (2.Быстродействие работы этого устройства ограничивается временем обращения к накопителю за последовательнык выбором всех микрокоманддля выполняемой операции, что не позволяет использовать его в быстродействующих сис-. темах, в которых быстродействие определяется временем передачи информации через базовые логические элЕмен ты И, ИЛИ и,НЕ.Цель изобретения - повышение быст родействия работы устройства.Поставленная цель достигается тем, что микропрограммное устройство управления., содержащее блок памяти микрокоманд, дешифратор операций, регистр операций, к-групп элементов И (к - максимальное количество фаэ в операции) и дешифратор Фаз, причем ар ресный вход блока памяти микрокоманд соединен через дешифратор операций с выходом регистра операций, информационный вход которого соединен с входом кода следующей операции устройства, первые входы элементов И к групп соединены с выходами дешифратора фаз соответственно, а выходы - с инфоркационным выходом устройства, дополнительно содержит два коммутатора, .дварегистра микрокоманд операции и триггер, причем вторые входы элементов Ик групп подключены соответственно квыходам первого коммутатора, управляю-щий вход которого подключен к инверсжому выходу триггера, прямой выходкоторого соединен с управляющим входом второго коммутатора, первый и второй информационные входы соединены со-)Оответственно с первым и вторьм выходами блока памяти микрокоманд, первый ивторой выходы второго коммутатора через первый и второй регистры микрокоманд операций подключены соответствен 15но к первому и второму информационным входам первого коммутатора, счетный вход триггера соединен с управляющим входом регистра операций иподключен х входу тактовых импульсовустройства, вход дешифратора фаз сое-динен с информационным входом устройства.На чертеже представлена функциональная схема предлагаемого устройст-.ва.25Устройство содержит блок 1 микрокоманд, дешифратор 2 операции и регистр 3 операций формирователя 4 адреса, вход 5 кода следующей операцииустройства, к-.групп элементов И б ЗО(к - максимальное количество фаз воперации), дешифратор 7 фаз, информационный выход 8 устройства, коммутатор 9, регистры 10 и 11 микрокоманд.о.1 ераций, коммутатор 12, триггер 13, 35вход 14 тактовых импульсов устройства, информационный вход 15,Предлагаемое устройство работаетследующим образом.Предположим, что в исходном состоОянии счетный триггер 13 подключаетинформационные выходы блока 1 черезкоммутатор 9 к информационным входампервого регистра 10 микрокоманд операции, а информационные выходы второгорегистра 11 микрокоманд операции подключает через коммутатор 12 к вкодамк-групп элементов И б, 1.огда в регистре 10 микрокоманд операции записанаинформация о всех микрокомандах, рас-определенная строго по Фазам, котораядолжна быть использована только привыполнении следующей по порядку операции Б регистре 11 микрокоманд операции записана информация о всех микрокомандах, распределенная также строго по Фазам, которая была использована при выполнении текущей операции.При поступлении каждого импульсаиз внешнего устройства управления навход 14 в регистр 3 операции со входа 5 записывается код следующей попорядку операции, который формируется во внешнем устройстве управления,а счетный триггер 13 устанавливаетсяв следующее по порядку состояние., Пос 65 ле поступления первого импульса на вход 14 (относительно исходного состояния, приведенного выше) счетный триггер 13 устанавливается в следующее о порядку состояние.При этом счетный триггер 13 подключает информационные выходы блока 1 через коммутатор 9 к информационным входам второго регистра 11 микро- команд операции, Формируя информацию о всех микрокомандах для следующей по порядку операции, и подключает ин,Формационные выходыпервого регистра 10 микрокоманд операции, в котором записана информация о всех микрокомандах для текущей операции, через коммутатор 12 к входам к-групп элементов И 6. При выполнении каждой из фаз операции информация с выхода коммутатора 12 проходит только через одну из к-групп элементов И б (т,е. часть информации,. но которая соответствует микрокоманде) на выходы 8 запоминаю"щего устройства микрокоманд, Управление порядком подключения групп И б осуществляется из внешнего устройства управления через. дешифратор 7 фаз. При каждом постуйлении следующего импульса на вход 14 коммутатор 9.и коммутатор 12 устанавливаются в противоположное положение, а регистры 10 и 11 микрокоманд операции меняются ро лями (запись - 10, а считывание - 11 или наоборот считывание - 10, а запись - 11). Положительный технический эФфект от использования предлагаемого устрой ства заключается в повышении быстро . действия работы устройства эа счет выбора из блока 1 по одному обращению к нему (10-0,1 мкс) сразу всех микро- команд, необходимых для выполнения операции, не.увеличивая длину слова, выбираемого из накопителя, что достигнуто благодаря группировке всех управляющих сигналов строго по фазам,а за-" тем это слово записывается в регистр микрокоманд операции и дешифруется по фазам (т.е. преобразуется в микро- команды) на выходе устройства без обращения к блоку 1 т.е. через время, равное считыванию из регистра 0,1- 0,05 мксусовмещения во времени медленногопроцесса записи всех микрокоманд изблока 1 в один из регистров микрокоманд операции для следующей по порядку операции (10"0,1 мкс) с быстрым процессом формирования микрокоманд (количество которых может достигать 8-10 - по числу фаз) для выполнения текущей операции (0,1-0,5 мкс) путемсчитывания ее из другого регистрамикрокоманд операции строго по фазам(т.е, по микрокомандам) на выходыустройства без обращения к медленнодействующему блоку 1.995091 формула изобретения оставитель Л. Логачева ехред Ж.Кастелевич К клак Редактор А, Ворович ек тор .О. Тираж 704Государствелам изобре ква, Ж,Подписноенного комитета СССРений и открытийРаушская наб., д. 4/5 Заказ б 4 б/3 ВНИИПИ по д 113035, МоФилиал П1 П ффПатентф, .г. Ужгород, ул. Проектная, 4 Микропрограммное устройство управления, содержащее блок памяти микро- команд, дешифратор операций, регистр операций, к групп- элементов И ( к - .максимальное количество фаз в операции) и дешифратор фаз, причем адресный вход блока памяти микрокоманд соединен через дешифратор операций с выходом регистра. операций, информа .10 ционный выход которого соединен с входом кода следующей операции устройст-. ва, первые входы элементов И к групп соединены с выходами дешифратора Фаз соответственно, а выходы - с информационньм выходом устройства, о т л ичающеес я тем, что, с целью. повышения быстродействия устройства, оно дополнительно аодержит два коммутатора, два регистра микрокоманд операции и триггер, причем вторые входы элементов И к групп подключены соответственно к выходам первого коммутатора, управляющий вход которого подключен к инверсному выходу триггера, прямой выход последнего соединенс управляющим входом второго коммутатора, первый и второй информационные .входй которого соединены соответственно с первые н вторым,; выходами бло"ка памяти микрокоманд, первый и второйвыходы второго коммутатора через первый и второй регистры мийрокомандопераций подключены соответственнок первомуи второму информационнымвходам первого коммутатора, счетныйвход триггера соединен с управляющим -входом регистра операций и подключенк входу тактовых .импульсов устройства, вход дешифратора фаз соединен синформационным входом устройства,Источники инФормации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР 9 б 35512, кл. О 11 С 11/00, 1976. 2, Авторское свидетелЬство СССР . В 490179, кл. 0 11 С 11/00, 1973 (прототип) .

СмотретьЗаявка

3333898, 09.09.1981

ПРЕДПРИЯТИЕ ПЯ А-7162

СОКОЛОВ ИГОРЬ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.02.1983

Код ссылки

<a href="https://patents.su/3-995091-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство управления

Следующий патент: Устройство динамического приоритета

Случайный патент: Устройство для маркировки бирок из термопластичной трубки