Устройство для вычисления функции х= +

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 964634

Автор: Чекушкин

Текст

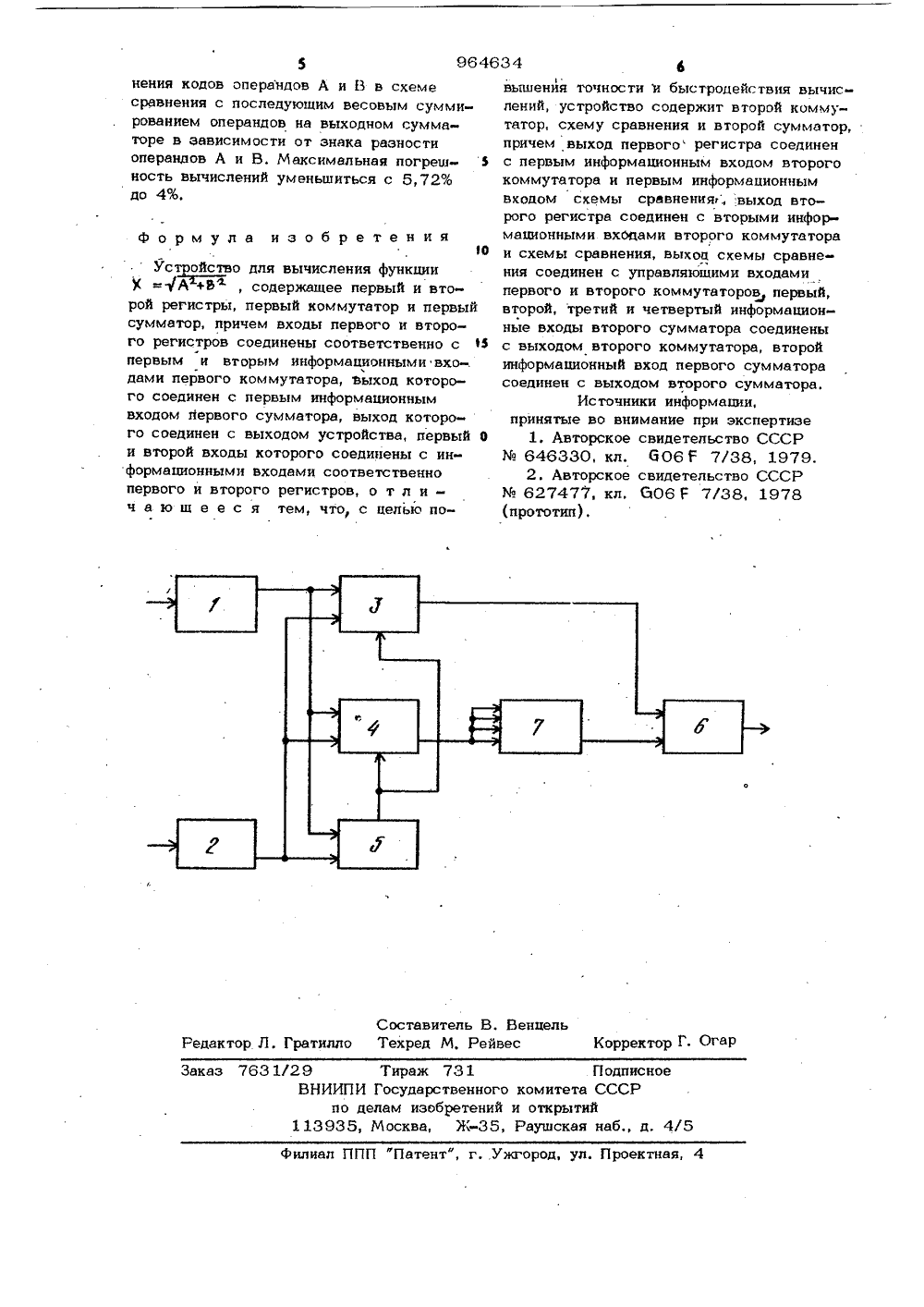

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Софоэ Сов етскмнСоцмалмстмчеснмнРеспублик пц 964634(22) Заявлено 02,03.81 (21) 3251645/18-24с присоединением заявки РВ(51)М. Кл. О 06 Г 7/552 Вжударетвснньб) квинтет СССР ао делан нзобретеннЯ н втнрытнй(088.8) Дата опубликования описания 10. 10.82(7) Заяви 54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ фУНКЦИ Х УГАвт Вп+ а Извес тн кже устрой тво для вычиссуммы квад- вычисление ленин кв ратов дв адратного корня из х чисел, в которо 1Изобретение относится к вь 1 числитевтфй ной технике и может быть исполъзовано в специализированных устройствах обработки информации.Известно устройство для вычисления фУннии И -чАв+Ьй, в петером выпив ление функции производится эа т 1 циклов с вычислением эа каждый цикл одной значашей пирры результата путем выполнении в каждом цикле трех операций с разрядны.10ми цифрами очередных разрядов С 1 и Ь 1 операндов А и В и содержашее блок суммирования, регистр левого сдвига на два разряда, три регистра левого сдвига на один разряд, три коммутатора, элементы15 ИЛИ, И и счетчик 1 .Недостатком такого устройства является низкое быстродействие, так как для, получения т 1 разрядов результата необходимо выполнить И циклов вычислений,фуннпии осушествпиетси путем реви и приближенной зависимости 1,5 оА и м ФА + В+ 0,5 //А/ + /В/,Недостатком устройства является его низкое быстродействие.Наиболее близким к изобретению по технической сушности является устройство, содержашее распределитель импульсов, коммутатор, состоящий иэ группы элементов И и ИЛИ, накапливающий сумматор, элемент И и регистры операндов сдвигаЯНедостатком известного устройства яв. ляется низкое быстродействие, так как вычисление осуществляется эа девять тактов путем последовательного вычисления разности (А) - (В) сдвига разности на один разряд вправо с последующей перезаписью значения 0,5 УА -/В// в накапливаюший сумматор и суммированием его с кодами операндов А и В, а также низкая точность вычислений, обусловленная реализацией приближенного алгоритма, .максимальная погрешность вычислений составляет 5,72%.Целью изобретения является повышениебыстр-действия в устройстве за счет сокра 1 цения числа тактов вычислений и повышение точности вычислений,Поставленная цель достигается тем, 5что в устройство для вычисления функции. регистры, первый коммутатор и первыйсумматор, причем выходы первого и второго регистров соединены соответственно 1 Ос.первым и вторым информационными входами первого коммутатора, выход которого соединен с первым информационнымвходом первого сумматора, выход которого соединен с выходом устройства, первыйБи второй входы которого соединены информашюнными входами соответственно первого и второго регистров, введены второйкоммутатор, схема сравнения и второйсумматор, причем выход первого регистра 20соединен с первым информационным входом второго коммутатора и с первым ин-формационным входом схемы сравнения,выход второго регистра соединен с вторыми информационными входами второго коммутатора и схемы сравнения, выход схемысравнения соединен с управляющими входами,первого и второго коммутаторов, первый, второй, третий и четвертый информационные входы второго сумматора соединены с выходом второго коммутатора, второй информационный вход первого сумматора соединен с выходом второго сумматора.Устройство реализует приближенныйалгоритм в соответствии с выражением. 1,04 А+В = (А + 0,4143 В) при АЪВ;1,041 тАстВи - В + 0,4143 А) сРи В С А.Ьа чертеже представлена функциональная схема устройства,Устройство содержит регистры 1 и 2,40первый и второй коммутаторы 3 и 4, схе-му 5 сравнения, первый и второй сумматоры 6 и 7.Выход регистра 1 соединен с первымвходом коммутаторов 3 и 4 и схемы 5сравнения. Выход регистра 2 соединен свторым входом коммутаторов 3 и 4 исхемы 5 сравнения. Выход схемы 5 сравнения соединен с третьям входом коммутатора 3, соединен с первым входом сумматора 6, второй вход которого соединенс выходом сумматора 7, входы которогосоединены с выходом коммутатора 4.Устройство работает следующим образом.55В регистры 1 и 2 засылаются кодыоперандов А и В, С выходов регистров 1и 2 коды операндов А и В подаются на соответствующие коды коммутаторов 3и 4 и схемы 5 сравнения. В зависимостиот знака равности А -В осуществляетсяподключение на входы сумматора 7 илиоперанда А, или операнда В. При АВна входы сумматора 7 подается код опе-ранда В; а на выходе сумматора 7 формируется значение кода 0,4143 В. Значение кода 0,4143 В получается путемодновременного суммирования значений-0 -В 72 В и 2 В 2 В и 2 В с последующим формированием окончательного результата 04143 В=В(2 +2+2 0+2 ),Сдвиг операнда В вправо на требуемоечисло разрядов (два, три, пять и семь)осуществляется соответствующим подключением выхода коммутатора 4 на входысумматора 7. Значение 0,4143 В подаетсяна второй вход выходного сумматора 6.На первый вход сумматора 6 в этом случае подается значение операнда А. Такимобразом, на выходе сумматора 6 получаемзначение (А + 0,4143 В). Получаемое насумматоре 6 число равняется знач=ниюискомой функции, помноженному на коэфициент 1,04 Коэффициент можно рассматривать как масштабный и учитывать;в дальнейших вычислениях,Эффективность изобретения заключается в повышении быстродействия за счетвычисления функции за один такт на проходе. Это позволяет применить устройствов быстродействующих и вычислительныхустройствах. Так, например, при использовании в известном устройстве тактирующих импульсов 10 мГц время вычисленияфуиисии Х:с 4 В и ссставит 0,9 мис.В предложенном устройстве время вычислений вы функции составляет 7;цццц ==ГСХХРОЬН.+ сУЕМКОмМ+сУМмй 1где - время вычисления функции;- время выполнения операциисравнения;сГ- время выполнения операции;суммирования в первом и втором сумматорах;время задержки сигнала вком мутаторе.При применении в сумматорах стандартных микросхем четырехразрядных полных сумматоров 155 ИМЗ для восьмиразрядных операндов время вычисленияСь 1 ф= 0,3 мкс.Таким образом, быстродействие предложенного устройства повышается в 3 раза,Повьпцена точность вьчислений засчет осуществления предварительного сравЗаказ 763 29 Тираж 73 1 ВНИИПИ Государственнопо делам изобретени 113935 Москва, Жи открытийРаушская наб., д. филиал ППП "Патент", г, Ужгород, ул. Проектная 5 9646 нения кодов операндов А и В в схеме сравнения с последующим весовым суммированием операндов на выходном сумма торе в зависимости от знака разности операндов А и В. Максимальная погреш ность вычислений уменьшиться с 572 одо 4 ,формула изобретения0Устойство дпв вычисленн функдии Х 1/А +В, содержашее первый и второй регистры, первый коммутатор и первый сумматор, причем входы первого и второго регистров соединены соответственно с 13дпервым и вторым информационными вхо-. дами первого коммутатора, выход которого соединен с первым информационным входом Первого сумматора, выход которого соединен с выходом устройства, первый О и второй входы которого соединены с информационными входами соответственно первого и второго регистров, о т л ич а ю ш е е с я тем, что, с целью по 34 бвышения точности и быстродействия вычислений, устройство содержит второй коммутатор, схему сравнения и второй сумматор,причем выход первого регистра соединенс первым информационным входом второгокоммутатора и первым информационнымвходом схемы сравнениявыход второго регистра соединен с вторыми информационными входами второго коммутатораи схемы сравнения, выход схемы сравнения соединен с управляюшими входамипервого и второго коммутаторов первый,второй, третий и четвертый информационные входы второго сумматора соединеныс выходом второго коммутатора, второйинформационный вход первого сумматорасоединен с выходом второго сумматора.Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРй 646330, кл. 606 г 7/38, 1979.2. Авторское свидетельство СССРЛь 627477, кл. 506 Р 7/38, 1978

СмотретьЗаявка

3251645, 02.03.1981

ПРЕДПРИЯТИЕ ПЯ В-2588

ЧЕКУШКИН ВСЕВОЛОД ВИКТОРОВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, функции

Опубликовано: 07.10.1982

Код ссылки

<a href="https://patents.su/3-964634-ustrojjstvo-dlya-vychisleniya-funkcii-kh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции х= +</a>

Предыдущий патент: Устройство для вычисления обратных тригонометрических функций

Следующий патент: Конвейерное устройство для вычисления функции =

Случайный патент: Распылитель