Конвейерное устройство для вычисления функции =

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

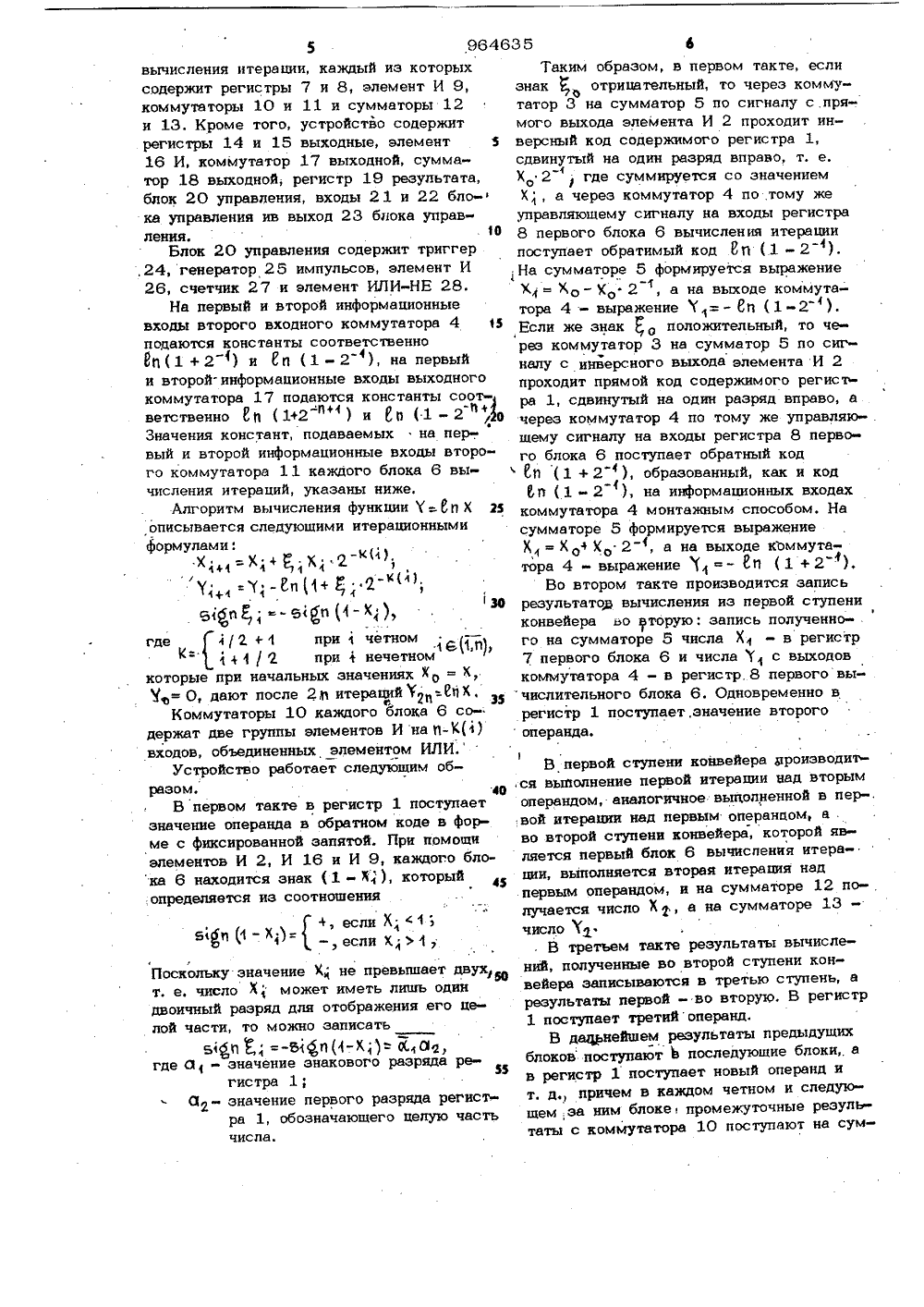

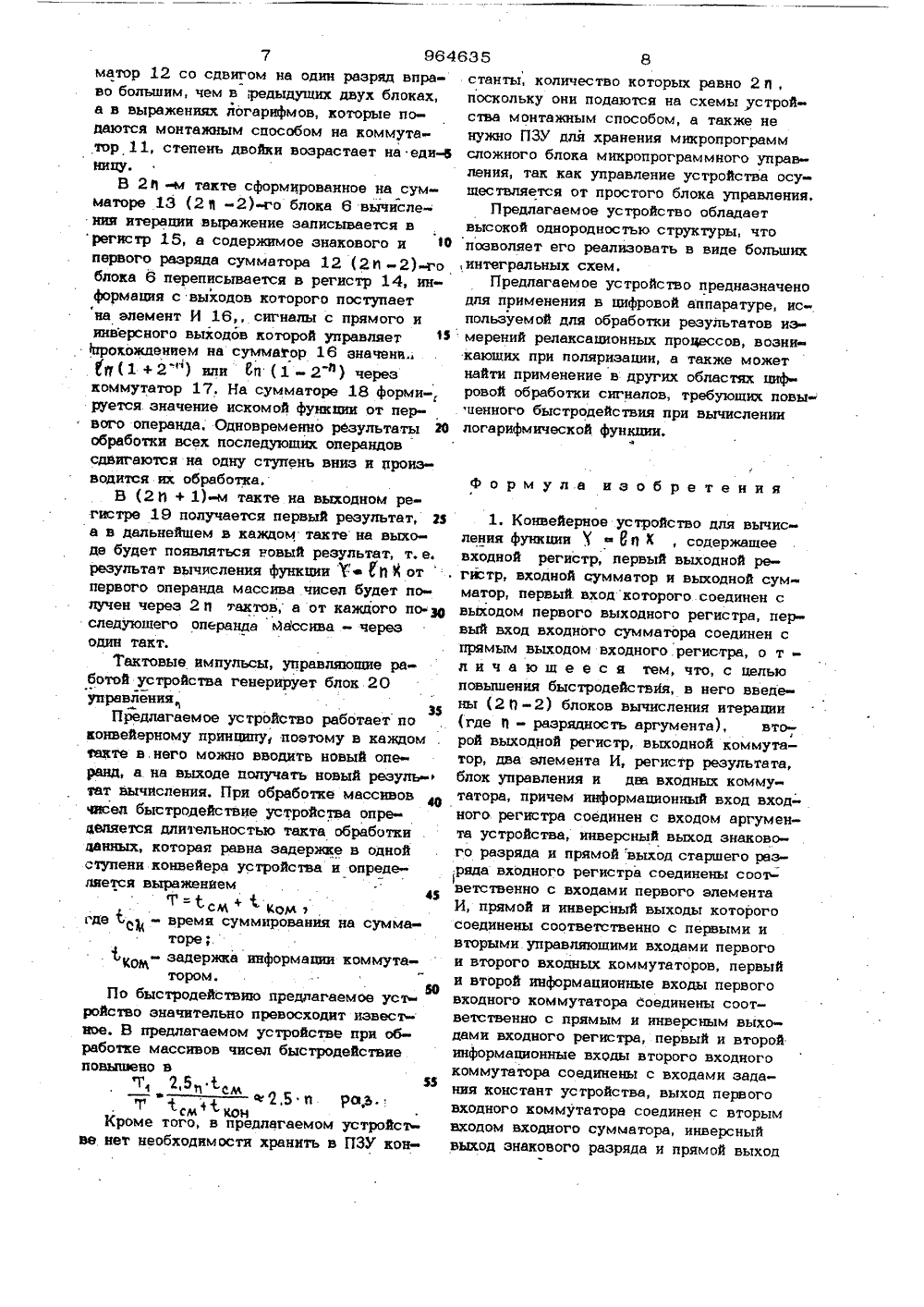

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистическиеРеспублик и 964635 К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(5 )И. Кд,06 Г 7/556 с присоединением заявки М Веудэрежнад кеитет СССР в делэи изобретений и открытий(71) Заявитель, Львовский ордена Ленина политехннчес им. Ленинского комсомолаий институт НВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИ фУНКЦ ИИ 1 = Ь Х5 Недостатком данного устройства является низкое быстродействие, поскольку логарифм числа выполняется за количество тактов, равное разрядности данного числа. к вычи Изобретение относится технике и может быть ис чес тве специалиэированно вычислительной сис темы водительности, построенн щих,интегральных схем д функцииф ЬХ. ельной польэован го процес высокой и ой на осно ля вычисл в каораоиэве больния Наиболее близким к изобретению по технической сущности является устройство, содержащее входной регистр, первый выходной регистр, входной сумматор и выходной сумматор, первый вход которого соединен с выходом первого выходного регистра, первый вход входного сумматора соединен с прямым выходом входного регистра, блок сдвига, вспомогательный: регистр для кратковременного хранения констант, постоянное запоминающее устройство (ПЗУ) для хранения констант, счетчик адреса, блок микропрограммного управления. Известизует операциБыстродейснии функции При цифровой обработке сигналов, на. пример, в задачах, связанных с обработкой физической информации, требуется выпол нять операции вычислении логарифмической функции над массивами чисел. Причем, в системах реального времени при исследовании быстропротекающих процессов требования к быстродействию выполнения 15 данной операции очень высоки.Известно устройство для вычисления логарифмов чисел, содержащее регистрчисла, накопитель, блок деления, схему сравнения, кольцевой сдвигающий регистр, регистры результата и блок управления., Алгоритм работы устройства основан на .методе проб и оценок 11 ое устройство аппаратно реал ю вычисления функции Х=Ь твие устройства при вычисле 1 = сй )- .не превышает вринверсным выходом знакового разряда ивыходом старшего разряда первого регистра, прямой выход которого соединен с первым входом первого сумматора, второйвход которого соединен с выходом первого коммутатора, первый и второй управляющие входы которого соединены соответственно с инверсным и прямым выходами элемента И и соответственно с первым и вторым управляющими входами второго коммутатора, первый и второй информационные входы которого соединены второй входы второго сумматора соединены соответственно с выходом второгорегистра и выходом второго коммутатора,первый и второй информационные входыпервого коммутатора соединены соответст венно с прямым и инверсным выходамипервого регистра, выходы первого и второго сумматоров 2-го блока вычисленияитерации ( 1 1, 2, , 2 П -3), соединены соответственно с информационнымивходами первого и второго регистров(+1)-го блока вычисления итераций,выходы входного сумматора и входногокоммутатора соединены соответственно с информационными входами первого и второго регистров первого блока вычисленияитераций, выходы первого и второго суммматоров (2 -2)-го блока вычисленияитераций соединены соответственно с информационными входами второго и первого выходных регистров, выход блока управления соединен с управляющими входами всех регистров, первый и второй входы блока управления соединены соотблок управления содержит счетчик, элемент ИЛИ-НЕ, триггер, генератор импульсов и элемент И, первый и второй входы которого соединены соответственно с выходом генератора импульсов и выходом триггера, первый и второй входы которого соединеНЕ, вход которого соединен с выходомсчетчика, вход записи которого соединен ный вход счетчика соединен с выходом элемента и выходом блока управления,На фиг, 1 представлена блок-схема устройства; на фиг. 2 - вариант выполнения блока управления.Конвейерное устройство для вычисления фукции (1 содержит регистр 1 входной элемент И 2, коммутаторы 3 и 4 входные, сумматор 5 входной, блоки 6 3 964635 4мени Г2,5 П , где й - разрядность обрабатываемых операторов; 1 с,- время суммирования двух чисел на сумматоре. При реализации известного устройства необходимо ПЗУ для хранения 2 пконстант, а также микропрограмм блокамикропрограммного управления 2Недостатком известного устройства является низкое быстродействие и большие1объемы дорогостоящих ПЗУ для хранения 1 Оконстант и микропрограмм,11 елью изобретения является повьпцениебыстродействия, с входами констант устройства, первый иПоставленная цель достигается тем,что в конвейерное устройство для вычиспения функции У = Ь Х, содержащее входной регистр, первый входной регистр, входной сумматор и выходной сумматор, первыйвход которого соединен с выходом первого выходного регистра, первый вход вход ного сумматора соединен с прямым выходом входного регистра, дополнительновведены (2 й -2) блоков вычисления ите, рации (где й - разрядность аргумента),второй выходной регистр, выходной комму-у 5татор, два элемента И, регистр результата, блок управления и два входных коммутатора, причеы информационный вход входного регистра соединен с входом аргумента устройства, инверсный выход знакового 5(,разряда и прямой выход старшего разрядавходного регистра соединены соответственно с входами первого элемента И, прямойи инверсный выходы которого соединенысоответственно с первыми и вторыми управ 35ляющими входами первого и второго вход.ных коммутаторов, первый и второй информационные входы первого входногО комму- ветственно с входом задания длины мастатора соединены соответственно с прямым сива и входом пуска устройства, причеми инверсным выходами входного регистра,40первый и второй информационные входывторого входного коммутатора соединеныс входами задания констант устройства,выход первого входного коммутатора соединен с вторым входом входного сумма 45тора, инверсный выход знакового разряда ны соответственно с вторым входом блои прямой выход старшего разряда второго ка управления и выходом элемента ИЛИвыходного регистра соединены соответственно с первым и вторым управляющимивходами выходного коммутатора, информа- с первым входом блока управления, счетционные входы которого соединены с вхо Одами задании констант устройства, выходвыходного коммутатора соединен с вторымвходом выходного сумматора, выход которого соединен с информационным входомрегистра результата, причем каждый блоквычисления итерации содержит два регистра, два коммутатора, два сумматора иэлемент И, входы которого соединены с35 Таким образом, в первом такте, если знак К отрицательный, то через коммуЬтатор 3 на сумматор 5 по сигналу с прямого выхода элемента И 2 проходит инверсный код содержимого регистра 1, сдвинутый на один разряд вправо, т. е, Х, 2 где суммируется со значением Х, а через коммутатор 4 по тому же управляющему сигналу на входы регистра 8 первого блока 6 вычисления итерации поступает обратимый код 3 п (1 -2 "). , На сумматоре 5 формируется выражение Х = Хо- Х 2, а на выходе коммутатора 4 - выражение 1: - Сп (1-2 ). Если же знакположительный, то через коммутатор 3 на сумматор 5 по сигналу с инверсного выхода элемента И 2 проходит прямой код содержимого регист ра 1, сдвинутый на один разряд вправо, а через коммутатор 4 по тому же управляющему сигналу на входы регистра 8 первого блока 6 поступает обратный кодЬ (1+2 ), образованный, как и код6 п (1 - 2 ), на информационных входах коммутатора 4 монтажным способом. На сумматоре 5 формируется выражение Х = Хо Хо 2 1, а на выходе кьммутатора 4 - выражение Ч =- 1 п (1+2 ),фВо втором такте производится запись результатов вычисления из первой ступени1 конвейера о вторую: запись полученного на сумматоре 5 числа )( - в регистр 7 первого блока 6 и числа 1 с выходов коммутатора 4 - в регистр, 8 первого вычислительного блока 6. Одновременно в регистр 1 поступает, значение второгооперанда. 1В первой ступени конвейера производится выполнение первой итерации над вторым операндом, аналогичное выцолненной в пер-. .вой итерации над первым операндом, а . во второй ступени конвейера, которой является первый блок 6 вычисления итерации, выполняется вторая итерация над первым операндом, и на сумматоре 12 получается число Х, а на сумматоре 13- число У 2.В третьем такте результаты вычислений, полученные во второй ступени конвейера записываются в третью ступень, а результаты первой - во вторую, В регистр 1 поступает третий операнд.В дащнейшем результаты предыдуших блоков поступают в последующие блоки, а в регистр 1 поступает новый операнд и т. дпричем в каждом четном и следующем,за ним блоке. промежуточные результаты с коммутатора 10 поступают на сум 5 9646вычисления итерации, каждый из которыхсодержит регистры 7 и 8, элемент И 9,коммутаторы 10 и 11 и сумматоры 12и 13. Кроме того, устройство содержитрегистры 14 и 15 выходные, элемент 516 И, коммутатор 17 выходной, сумматор 18 выходной; регистр 19 результата,блок 20 управления, входы 21 и 22 бло ка управления ив выход 23 блока управления. оБлок 20 управления содержит триггер,24, генератор 25 импульсов, элемент И26, счетчик 27 и элемент ИЛИ-НЕ 28.На первый и второй информационныевходы второго входного коммутатора 4 3подаются константы соответственно8 П(1+2 1) и (:и (1-2 ), на первыйи второй информационные входы выходногокоммутатора 17 подаются константы соот-ветственно ЯП (1+2 " ") и п (1-2 ЯоЗначения констант, подаваемых на первый и второй информационные входы второго коммутатора 11 каждого блока 6 вычисления итераций, указаны ниже.Алгоритм вычисления функции У: 1 и Х 25описывается следующими итерационнымиформулами:Х = Х. Г,Х. а-;, Еп ,(+ , -к,8 фп Е,; - бфп (4- Х;),Зфгде(2 1 при четномф ( Ф 1 (2 принечетномкоторые при начальных значениях хо = Х,У,= О, дают после 2 п итераций У=ИХ,Коммутаторы 10 каждого блока 6 содержат две группы элементов И на и-Квходов, объединенных элементом ИЛИ,Устройство работает следующим об 46В первом такте в регистр 1 поступаетзначение операнда в обратном коде в форме с фиксированной запятой. При помощиэлементов И 2, И 16 и И 9, каждого блока 6 находится знак (1- Ц), которыйопределяется из соотношенияГ , если )(-,ест Х)1,Поскольку значение Х не превышает двухт. е. число Мможет иметь лишь одиндвоичный разряд для отображения .его целой части, то можно записать54 п В ь(Фп И . 0 саяргде О- значение знакового разряда регистра 1;02- значение первого разряда регистра 1, обозначающего целую частьчисла.7 964матор 12 со сдвигом на один разряд вправо большим, чем в редыдущих двух блоках,а в выражениях логарифмов, которые подаются монтажным способом на коммутатор 11, степень двойки возрастает на еди ницу эВ 2 й -м такте сформированное на сумматоре 13 (2 5 -2)-го блока 6 вйчисления итерации выражение записывается врегистр 15, а содержимое знакового и 0первого разряда сумматора 12 (2 п -2)-гоблока 6 переписывается в регистр 14, информация с выходов которого поступаетна элемент И 16,сигналы с прямого иинверсного выходов которой управляет 1 фпрохождением на сумматор 16 эначени6 у ( 1 + 2 ") или 6 п ( 1 - 2"и. ) черезкоммутатор 17. На сумматоре 18 форми-,руется значение искомой функции от первого операнда, Одновременно результаты 20обработки всех последующих операндовсдвигаются на одну ступень вниз и производится их обработка.В (2 п + 1) м такте на выходном регистре 19 получается первый результат, 25а в дальнейшем в каждом такте на выходе будет появляться новый результат, т, е.результат вычисления функции Те Ь 1 отпервого операнда массива чисел будет получен через 2 П тактов; а от каждого по-З 0следующего операнда массива - черезодин такт,Тактовые импульсы, управляющие работой устройства генерирует блок 20управления33Предлагаемое устройство работает поконвейерному принципу, поэтому в каждомтакте в.него можно вводить новый операнд, а на выходе получать новый результат вычисления, При обработке массивовчисел быстродействие устройства определяется длительностью такта обработкиданных, которая равна задержке в однойступени конвейера устройства и определяется выражением43Т=Ссм+где 1- время суммирования на сумматоре;- задержка информации коммутатором.По быстродействию предлагаемое уст60ройс тво значительно превосходит иэвестиое. В предлагаемом устройстве при обработке массивов чисел быстродействиеповышено в72,5 и 1 смо 25 п Роьсм койКроме того, в предлагаемом устройстве иег необходимости хранить в ПЗУ константы, количество которых равно 2 и,поскольку они подаются на схемы устройства монтажным способом, а также ненужно ПЗУ для хранения микропрограммсложного блока микропрограммного управления, так как управление устройства осуществляется от простого блока управления,Предлагаемое устройство обладаетвысокой однородностью структуры, чтопозволяет его реализовать в виде больших,интегральных схем,Предлагаемое устройство предназначенодля применения в цифровой аппаратуре, используемой для обработки результатов измерений релаксационных процессов, возникающих при поляризации, а также можетнайти применение в других областях цифровой обработки сигналов, требующих повыценного быстродействия при вычислениилогарифмической функции,формула изобретения1. Конвейерное устройство для вычисления функции У3 и Х, содержащее входной регистр, первый выходной регистр, входной сумматор и выходной сумматор, первый вход которого соединен с выходом первого выходного регистра, первый вход входного сумматора соединен с прямым выходом входного регистра, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены (2 0 -2) блоков вычисления итерации (где й - разрядность аргумента), второй выходной регистр, выходной коммутатор, два элемента И, регистр результата, блок управления и два входных коммутатора, причем информационный вход входного регистра соединен с входом аргумента устройства, инверсный выход знакового разряда и прямой выход старшего разряда входного регистра соединены соответственно с входами первого элемента И, прямой и инверсный выходы которого соединены соответственно с первыми и вторыми управляющими входами первого и второго входных коммутаторов, первый и второй информационные входы первого входного коммутатора соединены соответственно с прямым и инверсным выходами входного регистра, первый и второй информационные входы второго входного коммутатора соединены с входами задания констант устройства, выход первого входного коммутатора соединен с вторым входом входного сумматора, инверсный выход знакового разряда и прямой выход964635 10, старшего разряда второго выходного регистра соединены соответственно с первым и вторым управляющими входами выходного коммутатора, информационные входы которого соединены с входами за дания констант устройства, вьмод выходного коммутатора соединен с вторым входом выходного сумматора, выход которого соединен с информационным входом регистра результата причем каждый блок вы- ф числения итерации содержит два регистра, два коммутатора, два сумматора и элемент И, входы которого соединены с ин версным выходом знакового разряда и выходом старшего разряда первого регистра,1 прямой выход которого соединен с первым входом .первого сумматора, второй вход которого соединен с выходом первого коммутатора, первый и второй управляющие входы которого соединены соответсъ ,венно с инверсным и прямым выходами элемента И и соответственно с первым и вторым управляющими входами второго коммутатора, первый и второй информационные входы которого соединены с входами констант устройства, первый и второй входы второго сумматора соединены соответственно с выходом второго регистра и выходом второго коммутатора, первый и второй информационные входы первого 5 а коммутатора соединены соответственно с прямым и инверсным выходами первого регистра, выходы первого и второго сум. маторов с -го блока вычисления итерации (Ф1, 2,) 2 и -фЗ) соединены соот-55 ветственно с информационными входами первого и второго регистров ( 4 + 1)-го блока вычисления итераций, выходы вход ного сумматора и входного коммутатора соединены соответственно с информационными входами первого и второго регистров первого блока вычисления итераций, выходы первого и второго сумматоров (2 Л)-го блока вычисления итераций соединены соответственно с информационными входами второго и первого вьмодных регистров, выход блока управления соединен с управляющими входами всех регист- ров, первый и второй входы блока управления соединены соответственно с входом задания длины массива и входом пуска устройства.2. Устройство по п, 1, о т л и ч а ющ е е с я тем, что блок управления содержит счетчик, элемент ИЛИ-НЕ, триггер, генератор импульсов и элемент И, первый и второй входы которого соединены соответственно с выходом генератора импульсов и выходом триггера, первый и второй входы которого соединены соответственно с вторым входом блока управления и выходом элемента ИЛИ-НЕ, вход которого соединен с вьмодом счетчика, вход записи которого соединен с пер вым входом блока управления, счетный ,вход счетчика соединен с вьмодом элемента и выходом блока управления.Источники информаций, принятые во внимание при экспертизе 1. Авторское свидетельство СССР % 590733, кл. 4 06 Р 7/38, 1978.2. Байков В. Д., Смолов В. Б. "Аппаратная реедизация элементарных функций в БВМ".Изд-во ЛГУ 1975.964635 Составитель А. ЗоринТехредМ, Рейвес . Корректор Г. Ог дактор Л. Гра Заказ 763 1/ Подписноеого комитета СССРний и открытийРаушскаа наб., д. 4/5. 2 9 Тираж 73 ВНИИПИ Государственнпо делам изобрете 13035, Москва, Жиал ППП Патент", г. Ужгород, ул. Проектна

СмотретьЗаявка

3255903, 09.03.1981

ЛЬВОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

МЕЛЬНИК АНАТОЛИЙ АЛЕКСЕЕВИЧ, ОСИПИШИН ИВАН САВВОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, конвейерное, функции

Опубликовано: 07.10.1982

Код ссылки

<a href="https://patents.su/7-964635-konvejjernoe-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Конвейерное устройство для вычисления функции =</a>

Предыдущий патент: Устройство для вычисления функции х= +

Следующий патент: Устройство для вычисления экспоненциальной функции

Случайный патент: Устройство для автоматической остановки вагонов при разрыве поезда