Преобразователь кода грея в двоичныйкод

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 842783

Автор: Ходаков

Текст

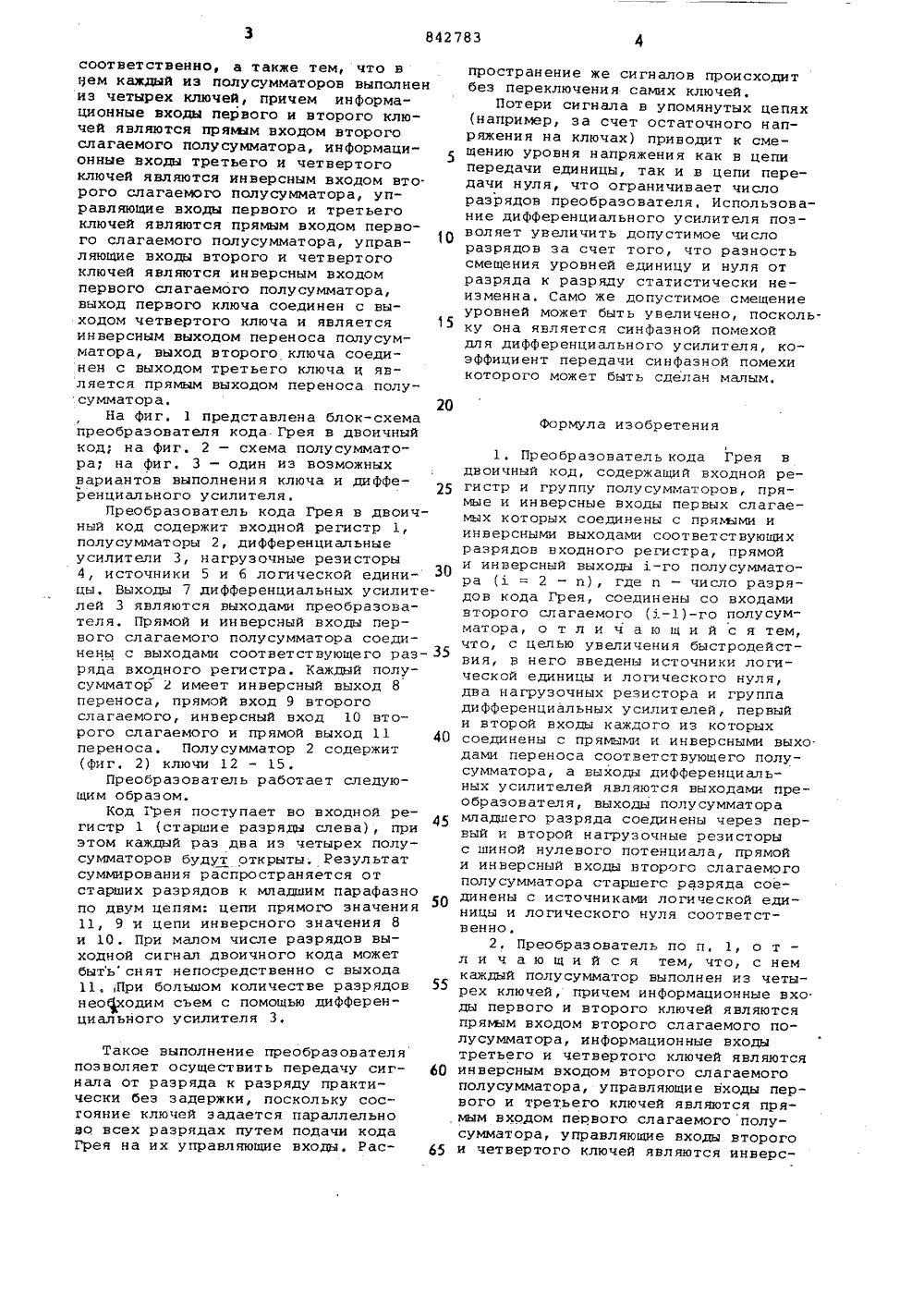

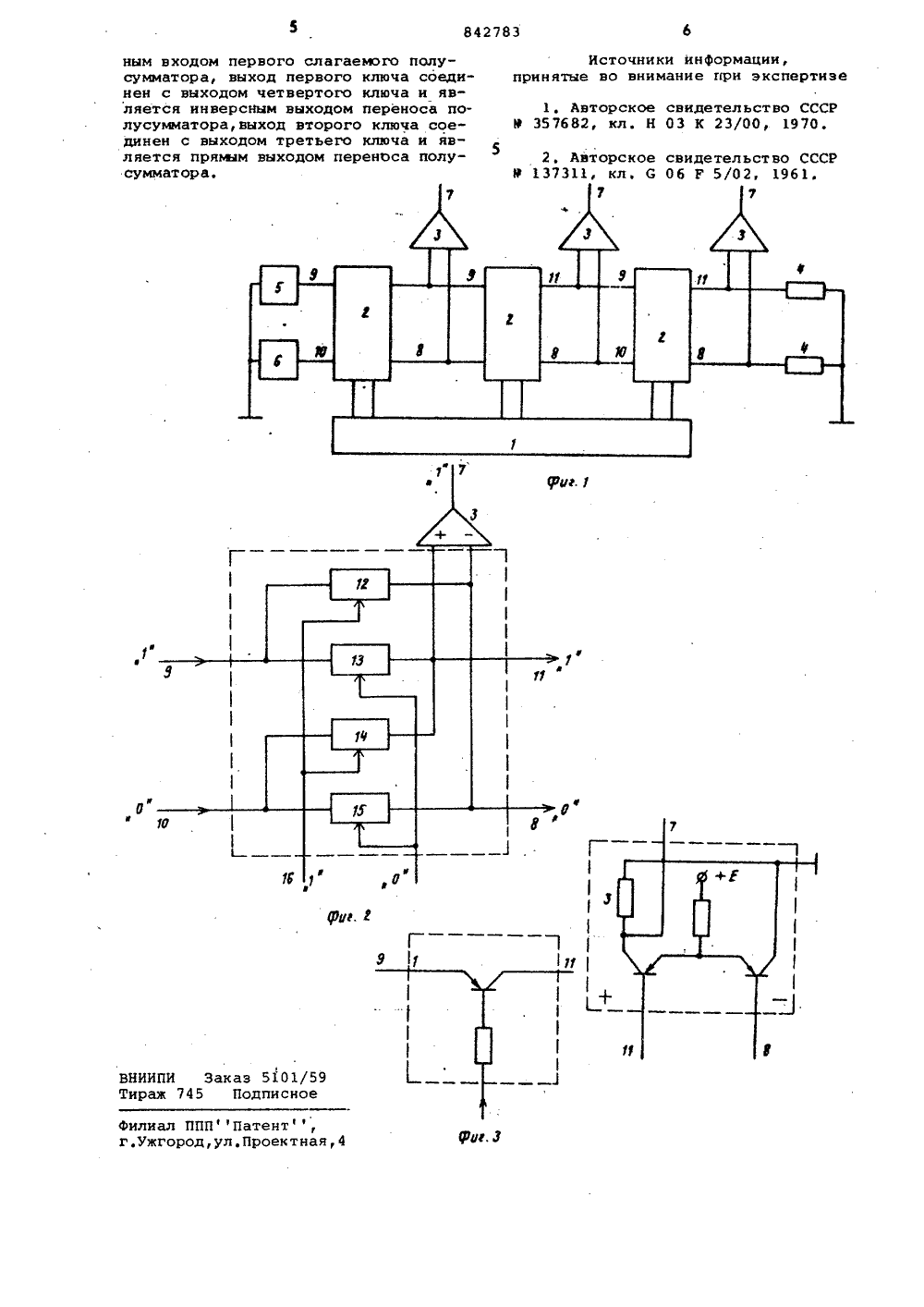

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕЧЕЛЬСТВУ и 184283 Союз Соеетскм Социалнстическик Республик(53)М. Кл. с присоединением заявк 06 Г 5 02 осударствениыЯ комите СССР ио делам изобретений и открытий(72) Автор из обретен и одако(71) Заявитель 4) ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ДВОИЧНЫЙ КОД о пчеобразонизком быстИз обре те ние относит ся к автоматике и вычислительной технике и можетбыть использовано при построении преобразователей кода Грея, аналого-цифровых преобразователей и узлов контроля по четности,Известно устройство для преобразования кода Грея в двоичный код,содержащее ряд последовательно соединенных полусумматоров 1).Недостаток этого преобразователясотоит в низком быстродействии,Наиболее близким к предлагаемомуизобретению по технической сущностии схемному решению является преобразователь кода Грея в двоичный код,содержащий входной регистр и группуполусумматоров, прямые и инверсныевходы первых слагаемых которых соединены с прямыми и инверсными выходамисоответствующих разрядов входногорегистра, прямой и инверсный выходыпереноса -го (1 = 2 - , п) полусумматора (где и - число разрядов кодаГрея) соединены со входами второгослагаемого (1-1)-го полусумматора2) .Недостаток известногвателя также состоит вродействии,Цель изобретения - повышение быстродействия преобразователя.Поставленная цель достигаетсяза счет того, что в преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полусумма- торов, прямые и инверсные входы первых слагаемых которых соединены с прямыми и инверсными выходами соответствующих разрядов входного регистра, прямой и инверсный выходы переноса 1-го (1 = 2 - и) полусумматора, где и - число разрядов кода Грея, сое динены со входами второго слагаемого (1-1)-ого полусумматора, введены источники логической единицы и логического нуля, два нагрузочных резистора и группа дифференциальных усилителей, первый и второй входы каждого из ко-, торых соединены с пряьыми и инверсными выходами переноса соответствующего полусумматора, а выходы дифференциальных усилителей являются выходами преобразователя, выходы полусумматора мпадшего разряда соединены через первый и второй резисторы с шиной нулевого потенциала, прямой и инверсный вход второго слагаемого полусумматора старшего разряда соединены со входами ЗО логической единицы и логического нулясоответственно, а также тем, что внем каждый из полусумматоров выполнениэ четырех ключей, причем информационные входы первого и второго ключей являются пряьим входом второгослагаемого полусумматора, информационные входы третьего и четвертогоключей являются инверсным входом вто.рого слагаемого полусумматора, управляющие входы первого и третьегоключей являются прямым входом первого слагаемого полусумматора, управляющие входы второго и четвертогоключей являются инверсным входомпервого слагаемого полусумматора,выход первого ключа соединен с выходом четвертого ключа и является 15ин нер сным выходом пер ен оса полусумматора, выход второго ключа соединен с выходом третьего ключа и является прямым выходом переноса полусумматор а. 20На фиг. 1 представлена блок-схемапреобразователя кода Грея в двоичныйкод; на фиг. 2 - схема полусумматора; на фиг. 3 - один иэ возможныхнариантон выполнения ключа и дифференциального усилителя,Преобразователь кода Грея в двоичный код содержит входной регистр 1,палусумматоры 2, дифференциальныеусилители 3, нагрузочные резисторы4, источники 5 и б логической едини- ЗОцы. Выходы 7 дифференциальных усилителей 3 являются выходами преобразователя. Прямой и инверсный входы первого слагаемого полусумматора соединены с выходами соответствующего раэ- З 5ряда входного регистра. Каждый полусумматор 2 имеет инверсный выход 8переноса, прямой вход 9 второгослагаемого, инверсный вход 10 второго слагаемого и прямой выход 11 4 Опереноса, Полусумматор 2 содержит(фиг. 2) ключи 12 - 15,Преобразователь работает следующим образом.Код Грея поступает во входной регистр 1 (старшие разряды слева), приэтом каждый раэ два иэ четырех полусумматоров будут открыты, Результатсуммирования распространяется отстарших разрядов к младшим парафазнопо двум цепям: цепи прямого значения11, 9 и цепи инверсного значения 8и 10. При малом числе разрядов выходной сигнал двоичного кода можетбытьснят непосредственно с выхода11.,При большом количестве разрядов 55необходим съем с помощью дифференциального усилителя 3,Формула изобретения 60 инверсным входом второго слагаемого полусумматора, управляющие входы перного и третьего ключей являются прямым входом первого. слагаемого полу- сумматора, управляющие входы второгоЯ и четвертого ключей являются инверсТакое выполнение преобразователя позволяет осуществить передачу сигнала от разряда к разряду практически беэ задержки, поскольку сосгояние ключей задается параллельно во всех разрядах путем подачи кода Грея на их управляющие входы. Распространение же сигналов происходитбез переключения самих ключей.Потери сигнала в упомянутых цепях(например, за счет остаточного напряжения на ключах) приводит к смещению уровня напряжения как в цепипередачи единицы, так и в цепи передачи нуля, что ограничивает число разрядов преобразователя, Использование дифференциального усилителя поэ -воляет увеличить допустимое числоразрядов за счет того, что разностьсмещения уровней единицу и нуля отразряда к разряду статистически неизменна. Само же допустимое смещение уровней может быть увеличено, поскольку она является синфазной помехойдля дифференциального усилителя, коэффициент передачи синфазной помехикоторого может быть сделан малым,1. Преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полусумматорон, прямые и инверсные нходы первых слагаемых которых соединены с пряжми и инверсными выходами соответствующих разрядов входного регистра, прямой и инверсный выходы 1-го полусумматора (1 = 2 - и), где и - число разрядов кода Грея, соединены со входами второго слагаемого (3.-1)-го полусумматора, о т л и ч а ю щ и й с я тем, что, с целью увеличения быстродействия, н него нведены источники логической единицы и логического нуля, дна нагрузочных резистора и группа дифференциальных усилителей, первый и второй входы каждого из которых соединены с прямыми и инверсными выхо. дами переноса соответствующего полусумматора, а выходы дифференциальных усилителей являются выходами преобразователя, выходы полусумматорамладшего разряда соединены через первый и второй нагруэочные резисторыс шиной нулевого потенциала, прямой и инверсный нходы второго слагаемого полусумматора старшегс разряда соединены с источниками логической единицы и логического нуля соответственно.2, Преобразователь по и, 1, о т л и ч а ю щ и й с я тем, что, с нем каждый полусумматор ныполнен из четырех ключей, причем информационные вхо.ды первого и второго ключей являютсяпряьым входом второго слагаемого полусумматора, информационные входытретьего и четвертого ключей являются.Ужго ным входом первого слагаемого полусумматора, выход первого ключа соединен с выходом четвертого ключа и является инверсным выходом переноса полусумматора,выход второго ключа соединен с выходом третьего ключа и является пряеым выходом переноса полусуммат ор а,НИИПИ Заказ 5101/59ираж 745 Подписное Источники инФормации,принятые во внимание при экспертизе1, Авторское свидетельство СССРЮ 357682, кл. Н 03 К 23/00, 1970. 5 2, Авторское свидетельство СССР 9 137311, кл, С 06 Р 5/02, 1961.

СмотретьЗаявка

1976353, 26.11.1973

ПРЕДПРИЯТИЕ ПЯ В-6269

ХОДАКОВ АНАТОЛИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: грея, двоичныйкод, кода

Опубликовано: 30.06.1981

Код ссылки

<a href="https://patents.su/3-842783-preobrazovatel-koda-greya-v-dvoichnyjjkod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь кода грея в двоичныйкод</a>

Предыдущий патент: Устройство для приведения р-кодовфибоначчи k минимальной форме

Следующий патент: Преобразователь двоичного кода вдвоично-десятичный

Случайный патент: Транспортное средство