Параллельный регистр

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

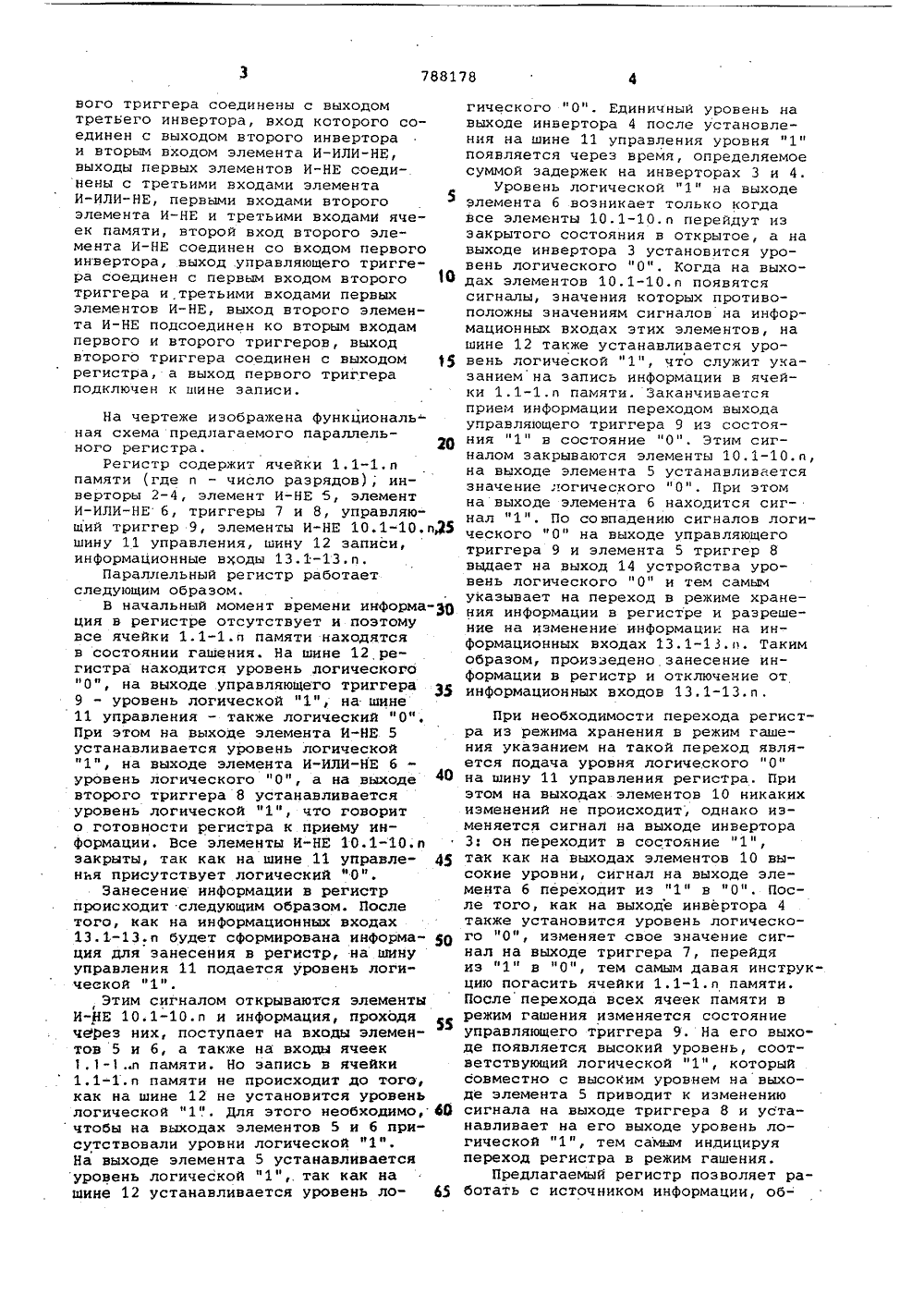

1 птвнГескаю" бблнпте.:ъ ЬФЕ А ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалистическихРеспублик н 1788178(22) Заявлено 28. 09, 78(21) 2670330/18-24с присоединением заявки Но(51)М. Кл. С 11 С 19/00 Государственный комитет СССР оо делам изобретений и открытий(54) .ПАРАЛЛЕЛЬНЫЙ РЕГИСТР Изобретение относится к вычислительной технике, в частности к устройствам для приема и хранения информации, передаваемой однофазными сигналами.5Известен регистр, содержащий ячейки памяти, выполненные на триггерах и элементы управления 1 .Известный регистр обладает низким быстродействием и невысокой надеж-тО ностьюНаиболее близким к изобретению по технической сущности является параллельный регистр, содержащий ячейки памяти, инвертор и управляющий триг гер, причем ячейки памяти первыми управляющими входами подключены к выходу инвертора, вход которого соединен со вторыми управляющими входами ячеек памяти и фазовой шиной ре ,гистра, выход управляющего триггера подключен к выходной шине регистра, а его входы соединены с вшходами ячеек памяти и инвертора 21.Однако параллельный регистр обла дает существенным недостатком, заключающимся в его ограниченных возможностях, так как после приема информации в ячейки памяти и формирования сигнала о приеме информации, тре буется подать на выхоцные информационные шины уровни напряжений, соответствующих логической "1". Только в этом случае регистр хранит записанную в ячейки памяти информацию.Цель изобретения - расширение области применения регистра за счет его работы с произвольной организацией смены состояний входной информации.Поставленная цель достигается тем, что в параллельный рег истр, содержащий ячейки памяти, первые входы которых соединены с выходом первого инвертора и первым входом управляющего триггера, вход первого инвертора подключен ко вторым входам ячеек памяти и к шине записи, выходы ячеек памяти соединены со вторыми входами управляющего триггера, и шину управления, введены элементы И-НЕ, элемент И-ИЛИ-НЕ, два триггера, второй и третий инверторы, вход второго инвертора соединен с шиной управления и первыми входами первых элементов И-НЕ, вторые входы которых подключены к информационным входам регистра и к первым входам элемента И-ИЛИ-НЕ, выход которого подсоединен к первому входу первого триггера, вторые входы первого триггера соединены с выходомтретьего инвертора, вход которого соединен с выходом второго инвертораи вторым входом элемента И-ИЛИ-НЕ,выходы первых элементов И-НЕ соединены с третьими входами элементаИ-ИЛИ-НЕ, первыми входами второгоэлемента И-НЕ и третьими входами ячеек памяти, второй вход второго элемента И-НЕ соединен со входом первогОинвертора, выход управляющего триггера соединен с первым входом второго Отриггера и третьими входами первыхэлементов И-НЕ, выход второго элемента И-НЕ подсоединен ко вторым входампервого и второго триггеров, выходвторого триггера соединен с выходом Ярегистра, а выход первого триггераподключен к шине записи,На чертеже изображена функциональ-ная схема предлагаемого параллельного регистра.Регистр содержит ячейки 1.1-1.ппамяти (где и - число разрядов), инверторы 2-4, элемент И-НЕ 5, элементИ-ИЛИ-НЕ б, триггеры 7 и 8, управляющий триггер 9, элементы И-НЕ 10.1-10,п,35шину 11 управления, шину 12 записи,информационные входы 13.1-13.п.Параллельный регистр работаетследующим образом.В начальный момент времени информаОция в регистре отсутствует и поэтомувсе ячейки 1.1-1.п памяти находятсяв состоянии гашения. На шине 12 регистра находится уровень логического"0", на выходе управляющего триггера9 - уровень логической "1", на шине11 управления - также логический "0", При этом на выходе элемента И-НЕ 5устанавливается уровень логической"1", на выходе элемента И-ИЛИ-НЕ б уровень логического ИО", а на выходе 40второго триггера 8 устанавливается уровень логической "1", что говорит о готовности регистра к приему информации. Все элементы И-НЕ 10.1-10.пзакрыты, так как на шине 11 управле нья присутствует логический фО".Занесение информации в регистр происходит следующим образом. После того, как на информационных входах13.1-13.п будет сформирована информа р ция для занесения в регистр, на шину управления 11 подается уровень логической ф 1".Этим сигналом открываются элементыИЕ 10,1-10.п и информация, проходя через них, поступает на входы элементов 5 и б, а также на входы ячеек 1.1-1,.п памяти, Но запись в ячейки 1.1-1.и памяти не происходит до того, как на шине 12 не установится уровень логической "1" Для этого необходимо, ФО чтобы на выходах элементов 5 и б присутствовали уровни логической ф 1 ф. На выходе элемента 5 устанавливается уровень логической "1",.так как на шине 12 устанавливается уровень ло гического "0". Единичныи уровень на выходе инвертора 4 после установления на шине 11 управления уровня "1" появляется через время, определяемое суммой задержек на инверторах 3 и 4.Уровень логической "1" на выходе элемента б возникает только когда все элементы 10.1-10.п перейдут из закрытого состояния в открытое, а на выходе инвертора 3 установится уровень логического "0". Когда на выходах элементов 10,1-10,п появятся сигналы, значения которых противоположны значениям сигналов на информационных входах этих элементов, на шине 12 также устанавливается уровень логической "1", что служит указанием на запись информации в ячейки 1.1-1.п памяти. Заканчивается прием информации переходом выхода управляющего триггера 9 из состояния "1" в состояние "0". Этим сигналом закрываются элементы 10.1-10.п, на выходе элемента 5 устанавливается значение логического "О". При этом на выходе элемента б находится сигнал "1". По совпадению сигналов логического "0" на выходе управляющего триггера 9 и элемента 5 триггер 8 выдает на выход 14 устройства уровень логического "0" и тем самым указывает на переход в режиме хранения информации в регистре и разрешение на изменение информации на информационных входах 23.1-13.п. Таким образом, произзедено занесение информации в регистр и отключение от информационных входов 13.1-13.п.При необходимости перехода регистра из режима хранения в режим гашения указанием на такой переход является подача уровня логического "0" на шину 11 управления регистра. При этом на выходах элементов 10 никаких изменений не происходит, однако изменяется сигнал на выходе инвертора 3: он переходит в состояние "1", так как на выходах элементов 10 высокие уровни, сигнал на выходе элемента б переходит из "1" в "0". После того, как на выходе инвертора 4 также установится уровень логического "0", изменяет свое значение сигнал на выходе триггера 7, перейдя из "1" в "0", тем самым давая инструкцию погасить ячейки 1.1-1.п памяти. После перехода всех ячеек памяти в режим гашения изменяется состояние управляющего триггера 9. На его выходе появляется высокий уровень, соответствующий логической "1", который совместно с высоким уровнем на выходе элемента 5 приводит к изменению сигнала на выходе триггера 8 и устанавливает на его выходе уровень логической "1", тем самым индицируя переход регистра в режим гашения.Предлагаемый регистр позволяет работать с источником информации, об788178 15 Составитель А. ВоронинНанкина Техред Е.Гав илешко 1 оррвкт Па дакто Тираж 662 осударственного ко лам изобретений и сва, Ж, Раушскаладающим произвольной организациейсмены состояния информационных шинв то время, как известный работаеттолько с источником информации, обладающим состоянием гашения междудвумя последовательными состояниямиинформационных шин, что упрощаетработу с источником информации и поВышает надежность устройства. Формула изобретения 10 Параллельный регистр, содержащий ячейки памяти, первые входы которых соединены с выходом первого инвертора и первым входом управляющего триггера, вход первого инвертора подключен ко вторым входам ячеек памяти и к шине записи, выходы ячеек памяти соединены со вторыми входами управляющего триггера, и шину управления, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения регистра за счет его работы с произвольной организацией смены состояний входной информации, в него введены элементы И-НЕ, элемент И-ИЛИ-НЕ, два триггера, второй и третий инверторы, вход второго инвертора соединен с шиной управления и первыми входами первых элементов И-НЕ, вторые входы которых подключены к информационным входам регистра и к первым входам элемента И-ИЛИ-НЕ, выход которого подсоединен к первому входу первоготриггера, вторые входы первого триггера соединены с выходом третьегоинвертора, вход которого соединен свыходом второго инвертора и вторымвходом элемента И-ИЛИ-НЕ, выходы первых элементов И-НЕ соединены с третьими входами элемента И-ИЛИ-НЕ,первыми входами второго элемента И-НЕи третьими входами ячеек памяти, второй вход второго элемента И-НЕ соединен со входом первого инвертора,выход управляющего триггера соединенс первым входом второго триггера итретьими входами первых элементовИ-НЕ выход второго элемента И-НЕ подсоединен ко вторым входам первого ивторого триггеров, выход второготриггера соединен с выходом регистра,а выход первого триггера подключенк Шине записи. Источники информации,принятые во внимание при экспертизе1. Патент ВеликобританииР 1378199, кл. 6 11 С 19/00, 1974.2. Авторское свидетельство СССР9 583480, кл, С 11 С 19/00, 04,02.76

СмотретьЗаявка

2670330, 28.09.1978

ПРЕДПРИЯТИЕ ПЯ А-3706

ПЕЛЕНОВИЧ ИГОРЬ ИВАНОВИЧ, СТАЛИН ЕВГЕНИЙ ГЕОРГИЕВИЧ, ЛОБАЧЕВ СЕРГЕЙ ЛЬВОВИЧ

МПК / Метки

МПК: G11C 19/00

Метки: параллельный, регистр

Опубликовано: 15.12.1980

Код ссылки

<a href="https://patents.su/3-788178-parallelnyjj-registr.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный регистр</a>

Предыдущий патент: Ассоциативный запоминающий элемент

Следующий патент: Накопитель

Случайный патент: Коммутирующее кольцевое устройство