Аналоговый компаратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

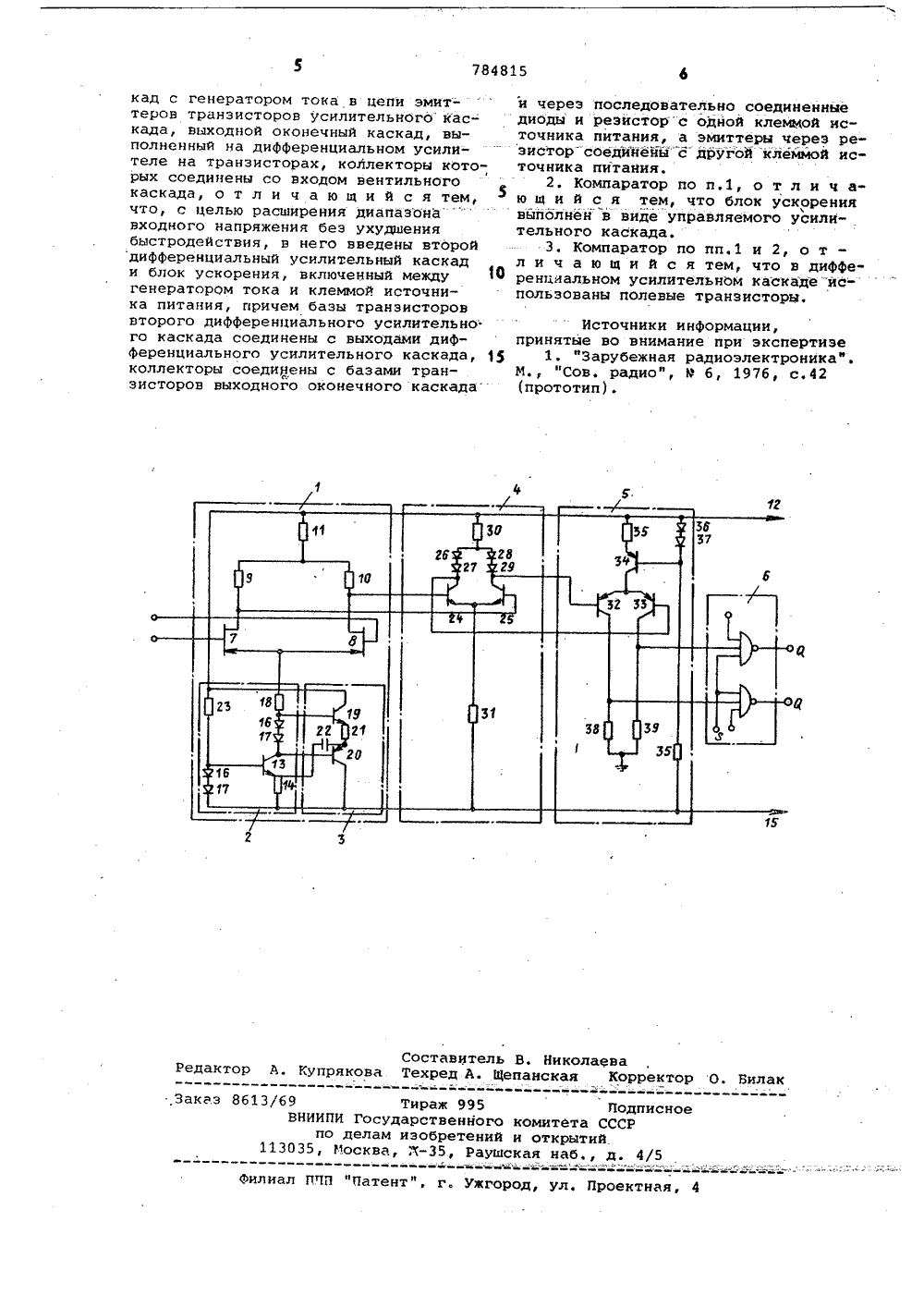

О П И С А Н И Е ,78481ИЗОБРЕТЕНИЯ Союз Советскик Социалистических Республик(23) Приоритет - (32) 22. 02. 77 Государственный комитет СССР но делам изобретений и открытий.5(088.8) Дата опубликования описания 301180 Иностранцы Янош Брауер, Петер Хацер, Иштван Секели,ференц Маркуш Лепк,Петер Рожа, Арпад Севези . и Дьерць Сараз(72) Авторы изобретения Иностранное предприятие(54) АНАЛОГОВЫЙ КОМПАРАТОР Изобретение относится к измерительной технике и найдет применение в электронных устройствах, преимущественно в приборах техники связи.Известен аналоговый компаратор, содержащий дифференциальный усилительный каскад с генератором тока в цепи эмиттеров транзисторов усилительного каскада, выходной оконечный каскад, выполненный на дифференциальном усили- О теле на транзисторах, коллекторы которых соединены с входом вентильного каскада 11 .Недостатком такого компаратора является то, что он может применяться 15 в сравнительно узком диапазоне входного напряжения.Цель изобретения - расширение диапазона входного напряжения без ухудшения быстродействия компаратора. 20Укаэанная цель достигается тем, что в аналоговый компаратор, содержаций дифференциальный усилительный каскад с генератором тока в цепи эмиттеров транзисторов усилительного кас када, выходной оконечный каскад, выполненный на дифференциальном усилителе на транзисторах, коллекторы которых соединены со входом вентиль- ного каскада, введены второй диффе ренциальный усилительный каскад и блок ускорения, включенный .между генератором тока и клеммой источника питания, причем база транзисторов второго дифференциального усилительного каскада соединены с выходами дифференциального усилительного каскада, коллекторы соединены с базами транзисторов выходного оконечного каскада и через последовательно соединенные диоды и резистор - с одной клеммой источника питания, а эмиттеры через резистор соединены с другой клеммой источника питания, при этом блок ускорения выпй- нен в виде управляемого усилительного каскада, а в дифференциальном усилительном каскаде использованы цолевые транзисторы.На чертеже изображена принципиальная схема аналогового компаратора.Компаратор содержит снабженный полевыми транзисторами.входной дифференциальный усилительный каскад 1, причем дифференциальный усилитель имеет генератор 2 тока и блок 3 ускорения. Затворы полевых транзисторов, осуцествляющих Функции управляемях элементов, образуют входы входного дифференциального усилительного каскада 1. На выходе дифференциального уси784815лительного каскада 1 включен дифферен и 29 соединен 1 б йны через о щий резисс перво клеммой 2 источникаусилительный каскад 4, Выход тор 30 с первой кле й 12дифференциального усилительного кас- напряжения, Резисто 31 п екада 4 через оконечный каск 5 оения, езистор представляете ы каскад 5 со- собой генератор тока дифференциальноединен с вентильным каскадом 6 для го усилител о ад 4передачи нагрузки на выходе.го усилительного каскада он поме/щен между второй клеммой 15 источникаВходы компаратора образованы за-напряжеиия и об имитвс.ами полевых транзисто ов 7 и 8щими эмиттерами шестов транзисторов 7 и 8, го и седьмого транзисторов 24 и 25,расположенных во вхо ном ид д фференциаль- Также и оконечный усилительный касном усилительном каск е.вых транзисторов 7 и 8 образуют сад . Стоки поле- кад 5 содержит дифференциальный усилитель. Вход этоГо каскада образованодиой стороны выход этого каскада, а О базами помещенных в иффы . в ди еренциальР они соединены"чеРез нам усилителе транзисторов 32 и 33резистор 9 или резистор 10 и че езобщий резисто 1 с пе вр ор 10 и через типа р-п-р, а выход каскада сое иненр р 1 с первой клеммой 12 с коллекторами транзисторов 32 и 33,д енисточника напряжения. Совместно вклю- Оконечный усилительный каскад 5 имеетченные истоки полевых транзисто овети 8 присоединены к выхоР исторов 7 15 генератор тока с разомкнутым коллекток выходу генератора ром, причем эмиттер транзистора 34соединен через резистор 35 с первойГенератор 2 тока со е жит т ан- клеммой 12 источника напряжения, Базаэистор 13 с разомкнутым коллекто ом.Эмиттер транзисто а 13 сое инеиу ым коллектором. транзистора 34 присоединена к выхора 3 соединен через р второго делителя. Второй делительы дурезистор 14 со второй клеммой 15 ис- состоит из резистора 35, включенноготочника напряжения, Коллектор тран- между клеммами 15 и 12и , и соединенныхвключенные вторые диоды 16 и 1 амежду собой последовательно диодов36 и 37. Делитель выполнен так, чтотакже через резистор 18 выполняетдиоды 36 и 37 делителя включаютсяфункцию входа генератора 2 тока.Гене апараллельно с диодом база - эр тор 2 тока соединен с блоком транзистора 34.миттер3 ускорения, выполненным как управ- дифференциальный усили бси тель сна женмый усилительный каскад соде житкаскад управляе- симметричным выходом, Резисторы 38транзистор 19 типа о- -и и т анзистоад держит и 39, соединенные с корпусом, являютр и транзистор ЗО ся коллекторными сопротивлениями дифр р, включенные м жду двумя ференциального усилителя."клеммами 15 и 12 источника нап яженияТранзистор 20 соединен через еэистос ника напРяжения, Вентильный каскад 6, передающий21 с эмиттером транзистора 19. Базад , через резистор выходную нагрузку, соединен однимтранзистора 20 присоединена к коллекИс ора 19 База своим входом с выходом оконечноготору транзистора 13, расположенномр д а к коллек- З 5 каскада, а другие входы предназначав генераторе 2 тока. Эмитте т анэисРРасположенномУ . ются для селектирующих импульсов,тора 20 через конденсатор 22 соедиЭмиттер транэис- Принцип работы данного компарато ао и рат ранен с эмиттером транзистора 13. Базаи известнйх компараторов аналогичен.транзистора 21 соединена с общейРазличие входных сигналов усиливаточкой диода 16 и езисто а 18.4 О ется входным каскадом 1. ПолученныйБаза т анзисто а осигнал управляет дифференциальным усиР нзистоРа 13, помещенного лительным каскадом 4 или оконечнымв гене ато е 2 токар р 2 тока, соединена с вы- усилительным каскадом 5. Все каскадыходом первого делителя, причем первый выполнены таким образом или коллекделитель состоит из пе вого ези - то а 23 вкл еь состоит из первого резис- торнйе нагрузки выбраны так что Ра"р , включенного между обеимибочие точки активных элементов воВи 12 источника напряжения всей области регулирования находятсяи=соединенных друг с другом последо- вйределах линейной зоны, в результавательно диодов 16 и 17 Нделителя- ния,д дов 16 и 17, Нижнее звеноте чего не возникает перевоэбуж ения" е я, содержащее диоды, параллель- или насыщения,но соединено с дио ами база -транзистора 13.д с диодами база - эмиттер 50 При перерегулировании компаратбрапереходный сигнал, поступающий на реВторой ступенью компаратора явля- зистор 18, управляет через конденсается дифференциальный усилительный тор блока Ускорения транзистором 13" каскад 4, состоящий из дифференциаль генератора тока, благодаря чему обесного усилителя высокого быстродейст печивается ускоренное переключение ввия,обоих направлениях.Вход .дифференциального усилитель- Расположенные в делителях диодыного каскада 4 образован базамй тран- компенсируют температурную зависизисторов 24 и 25 типа и-р-и диффе- мость генераторов тока.Ренциального усилителя, а выход каскада соединен с коллекторами транзисторов 24 и 25. Включенные последо- . Формула изобретениявательйо диоды 26-29 образуют коллекторные сопротивления транзисторов 24 1. Аналоговый компаратор содержа 25. Аноды диодов 26 и 27 илидиодов б 5 щий дифференциальный усилительный касдписноеР ВНИИПИ Гос по дела 13035, Москв4 тная, 4 Филиал ПЧП "Патен г. Ужгород, ул. кад с генератором тока в цепи эмиттеров транзисторов усилительного кас-када, выходной оконечный каскад, выполненный на дифференциальном усилителе на транзисторах, коллекторы которых соединены со входом вентильногокаскада, о т л и ч а ю щ и й с я тем,что, с целью расширения диапазонавходного напряжения беэ ухудшениябыстродействия, в него введены второйдифференциальный усилительный каскади блок ускорения, включенный между огенератором тока и клеммой источника питания, причем базы транзистороввторого дифференциального усилительного каскада соединены с выходами дифференциального усилительного каскада, 15коллекторы соедииены с базами транзисторов выходного оконечного каскада и через последовательно соединенные диоды и резистор"с одной клеммой источника питания, а эмиттеры через резистор соединейй "с другой клеммой источника питания.2. Компаратор по п.1, о т л и ч аю щ и й с я тем, что блок ускорения вййолнен в виде управляемого усилительного каскада.3. Компаратор по пп,1 и 2, о т - л и ч а ю щ и й с я тем, что в дифференциальном усилительном каскаде"использованы полевые транзисторы,Источники информации,принятые во внимание при экспертизе1. фЗарубежная радиоэлектроника".М., "Сов. радио", Р 6, 1976, с.42

СмотретьЗаявка

2583497, 21.02.1978

ЯНОШ БРАУЕР, ПЕТЕР ХАЦЕР, ИШТВАН СЕКЕЛИ, ФЕРЕНЦ МАРКУШ ЛЕПК, ПЕТЕР РОЖА, АРПАД СЕВЕЗИ, ДЬЕРЦЬ САРАЗ

МПК / Метки

МПК: H03K 5/22

Метки: аналоговый, компаратор

Опубликовано: 30.11.1980

Код ссылки

<a href="https://patents.su/3-784815-analogovyjj-komparator.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый компаратор</a>

Предыдущий патент: Устройство для выбора адреса

Следующий патент: Устройство для передачи и приема кодированного сигнала изображения

Случайный патент: Способ подготовки поверхности пресс-формы перед прессованием