Устройство опознавания сигналов, модулированных по фазе

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 656003

Авторы: Александров, Иванов-Шидловский, Ковешников, Химулин, Чистов

Текст

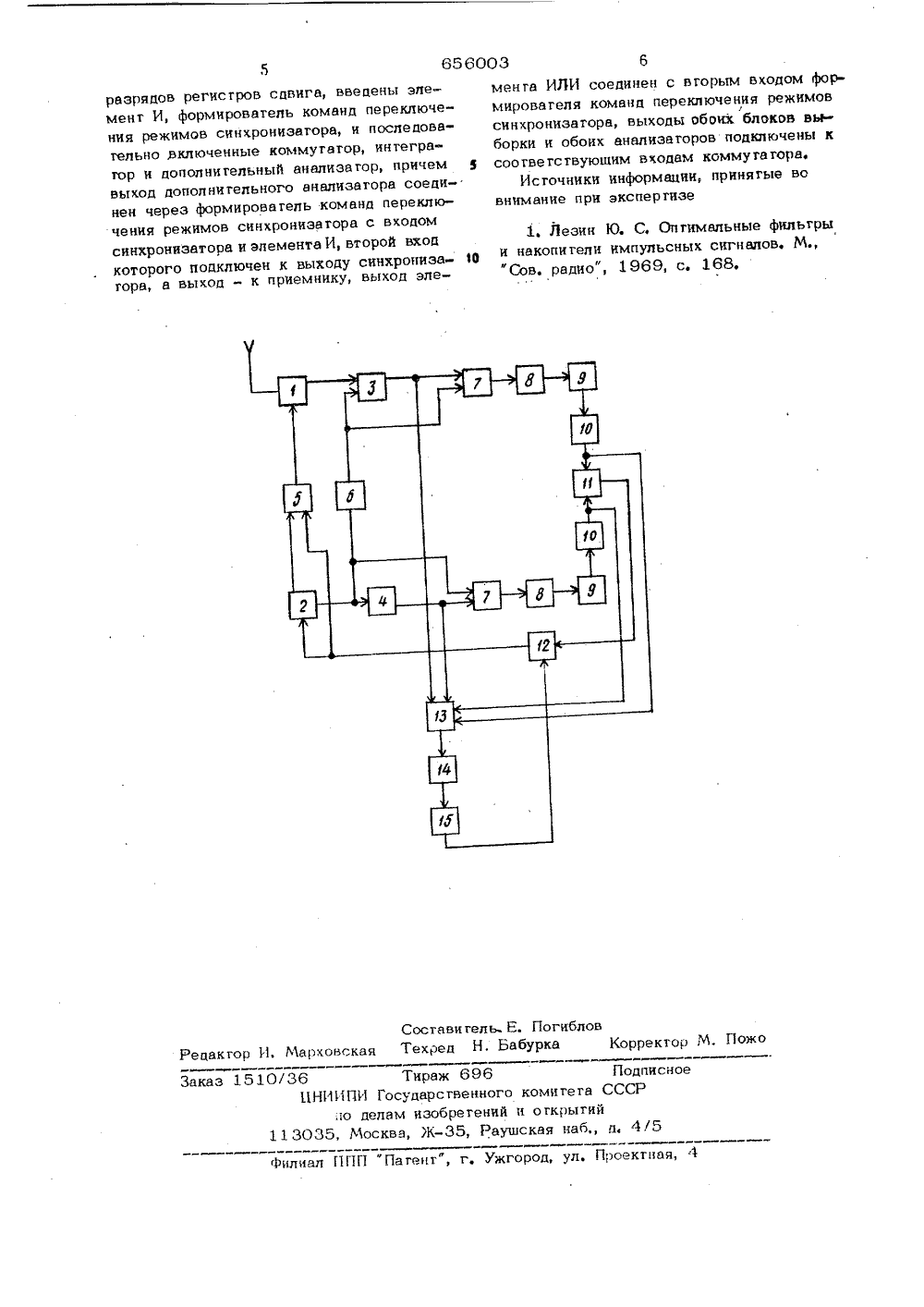

3бклиат - р Союз Советских Социалмстицеских Республикип 1 656003 ОП ИСАН ИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУвки И присоединением 3) ПриоритетГосударставииый июСССР .аа делам изабретви открытий Опубликовано 05,04.79.Бюллетень13 Лата опубликования описания 09.04.79 3) УЛК 621,396. 986(088 8)(54) УСТРОЙСТВО ОПОЗНАВАНИЯ СИГНАЛОЦ МОДУЛИРОВАННЫХ ПО ФАЗЕем с Изобретение относится к радиотехникеи может использоваться для обнаружениясигналов при определении места положения подвижных объектов,Известно устройство опознавания сигналов, модулированных по фазе, содержашее приемник, выход которого через двеидентичные цепи из последовательно включенных блока выборки, регистра сдвига,дешифратора, сумматора и анализатораподключен к двум входам элемента ИЛИ,синхронизатор, выход которого подключенк вторым входам блока выборки и регистра сдвига одной цепи. непосредственно, адругой - через блок задержки 11ЧОднако это устройство имеет значительный объем оборудования. Иель изобретения - уменьшение объоборудования путем сокрашения числа ррядов регистров сдвигаДля этого в устройство опознаванияигналов, модулированных по фазе, содежашее приемник, выход которого через две идентичные цепи из последовательновключенных блока выборки, регистра сдвига, дещифратора, сумматора и анализатора подключен к двум входам элементаИЛИ, синхронизатор, выход которого подключен к вторым входам блок выборкии регистра сдвнга одной цепи непосредственно, а другой - через блок задержки,введены элемент И, формирователь командпереключения режимов синхронизатора ипоследовательно включенные коммутатор,интегратор и дополнительный анализатор,причем выход дополнительного аналнзатора соединен через формирователь команд переключения режимов синхронизатора с входом синхронизатора и элемента И, второй вход которого подключен к выходу синхронизатора, а выход - к приемнику, выход элемента ИЛИ соединен с вторым входом формирователя команд переключения режимов синхронизатора, выходы обоих блоков выборки и обоих анализаторов подключены к соответствующим входам комму та тораНв черт же изображена структурнаяэлектрическая схема предложен ого устройства.Устройство содержит приемник 1, синхронизатор 2, блоки 3,4 выборки, элемент 5И 5, блок 6 задержки, регистры 7 сдвига, дешифраторы 8, сумматоры 9, анализаторы 10, элемент ИЛИ 11, формироввгель 12 команд переключения режимовсинхронизатора, коммутатор 13, интегратор 14 и дополнительный анализатор 15.Устройство работает следующим образом.Сигнал с приемника 1 поступает наблоки 3, 4 выборки. На управляющий вход 15приемника 1 через элемент И 5 поступаютдекодируюшие импульсы для раскодировкисигнала в режиме контроля, в режиме жеускоренного поиска нв регистрах. (режим"сетка" ) нв второй вход элемента И 5поступает команда запрета от формнротеля 12 команд и сигнал с приемника 1поступает нервскодированныйНа второй вход блоков 3, 4 выборкии на тактовые входы регистров 7 сдвигаодновременно поступают стробируюшие импульсы от синхронизатора 2 (причем наодин из блоков выборок - непосредственно, а на другой - через блок задержки 6со сдвигом на 1/4 периода несушей час 30тоты для реализации квадратуры),)2 алее выборки сигналов поступают нарегистр 7 сдвига и постепенно заполняютего. Выходы регистра 7 сдвига сгруппи-рованы таким образом, чтобы в момент35записи в первый. разряд регистра последнего анализируемого импульса сигнала нвдешифратор 8 поступала информация овсех анализируемых выборках сигнала.40В момент записи в соответствующихразрядах регистра сдвига 7 кода сигналана выходе дешифратора 8 появляются все1" или"0 в зависимости от стробируемойв данный момент фазы сигнала.Эта информация суммируется в сум 45маторе 9 и поступает на анализатор 10;который в случае превышения количества "1" или "0" определенной пороговойвеличины, срабатывает и через элементИЛИ 11 подает команду на формирователь5012 команд переключения режима синхронизации. Благодаря этому синхронизатор2 переключается в режим работы "пачка"и разрешается прохождение декодируюших55импульсов нв приемник 1 через элементИ 5. Оекодируюшие импульсы формируются с таким расчетом, чтобы при правильном взаимном временном положении сигпалов и пачек стробируюших импульсов на выходе приемнике 1 все радиоимпульсы данной станции имели одинаковую фазу,Одновременно на коммутатор 13 подается команда от соответствуюшего анализатора 10, и к интегратору 14 подключается блок выборок (3 или 4), в канале которого произошло обнаружение сигнала. Тем самым отпадает необходимость во втором квадратурном контрольном канале на этапе контроля.Выход интегратора 14 подается на анализатор 15 ( в который входит схема обработкк и пороговая схема).Если контрольный канал (время анализа в точке в котором может быть выбрано значительно большим, чем в канале на регистре сдвига из расчета заданных величин вероятностей ложной тревоги и пропуска сигнала, т.к. увеличение объема реверсивного счетчика, скажем от 16 до 256 бит обходится всего в лишний корпус микросхемы) не подтверждает правильности обнаружения, команда с выхЬда анализатора 15 поступает на второй вход формирователя 12 команды и переводит синхронизатор 2 опять в режим "сетка" и одновременно запрещает прохождение декодируюших импульсов через элемент И 5 на приемник 1Таким образом поскольку заданные величины ложной тревоги и пропуска сигнала обеспечиваются контрольным каналом, объем выборок, а, следовательно, и объем регистров на первом этапе поиска можно выбрать минимальным.Предложенное ус т рой ство поэволяе т значительно сократить объем оборудования, поскольку позволяет только на одних регистрах сэкономить около 1 30 корпусов микросхем.формула изобре генияУстройство опознавания сигналов, модулированных по фазе, содержвшее приемник, выход которого через две идентичные цепи из последовательно включенных блока выборки, регистра сдвига, дешифрвгора, сумматора и анализатора подключен к двум входам элемента ИЛИ, синхрони,"втор, выход которого подключен к вторым входам блока выборки и регистра сдвига одной цепи непосредственно, а другой - через блок задержки, о т л и ч а ю ш е - е с я тем, что, с целью уменьшения объема оборудования путем сокрашения числа656003 Составитель. Е. ПогнбловРедактор И, Марковская Техред Н, Бабурка орректор М Пож Зака 10/36 Тираж 6 1 НИ И ПИ Государ с гве по делам иэобрет 3035, Москва Ж, 6 Подписно ного комитета СССРений и открытий Раущская наб., д. 4,Рнлнал ПГ 1 П "Патент", г, Ужгород, ул. Проектная, 4 разрядов регистров сдвига, введены элемент И, формирователь команд переключения режимов синхронизатора, и последовательно включенные коммутатор, интегратор и дополнительный анализатор, причем 5выход дополнительного анализатора соединен через формирователь команд переключения режимов синхронизатора с входомсинхронизатора и элемента И, второй входкоторого подключен к выходу синхронизагора, а выход - к приемнику, выход эле 6мента ИЛИ соединен с вторым входом формирователя команд переключения режимов/синхронизатора, выходы обонх блоков выборки и обоих анализаторов подключены к соответствующим входам коммутатора.Источники информации, принятые во внимание при экспертизе 1. Лезин Ю. С. Оптимальные фильтрыи накопители импульсных сигналов. М.,

СмотретьЗаявка

2548221, 28.11.1977

ПРЕДПРИЯТИЕ ПЯ В-2203

ХИМУЛИН ВЛАДИЛЕН ИВАНОВИЧ, КОВЕШНИКОВ ВАХТАНГ ПАВЛОВИЧ, ЧИСТОВ ЮРИЙ ГАВРИЛОВИЧ, ИВАНОВ-ШИДЛОВСКИЙ НИКОЛАЙ ВЛАДИМИРОВИЧ, АЛЕКСАНДРОВ АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: G01S 1/24

Метки: модулированных, опознавания, сигналов, фазе

Опубликовано: 05.04.1979

Код ссылки

<a href="https://patents.su/3-656003-ustrojjstvo-opoznavaniya-signalov-modulirovannykh-po-faze.html" target="_blank" rel="follow" title="База патентов СССР">Устройство опознавания сигналов, модулированных по фазе</a>

Предыдущий патент: Устройство для устранения многозначности при фазовых измерениях

Следующий патент: Способ измерения влажности воздуха

Случайный патент: Способ оценки стойкости моторного масла к шламообразованию