Микропрограммное устройство управ-ления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 842815

Автор: Черепанов

Текст

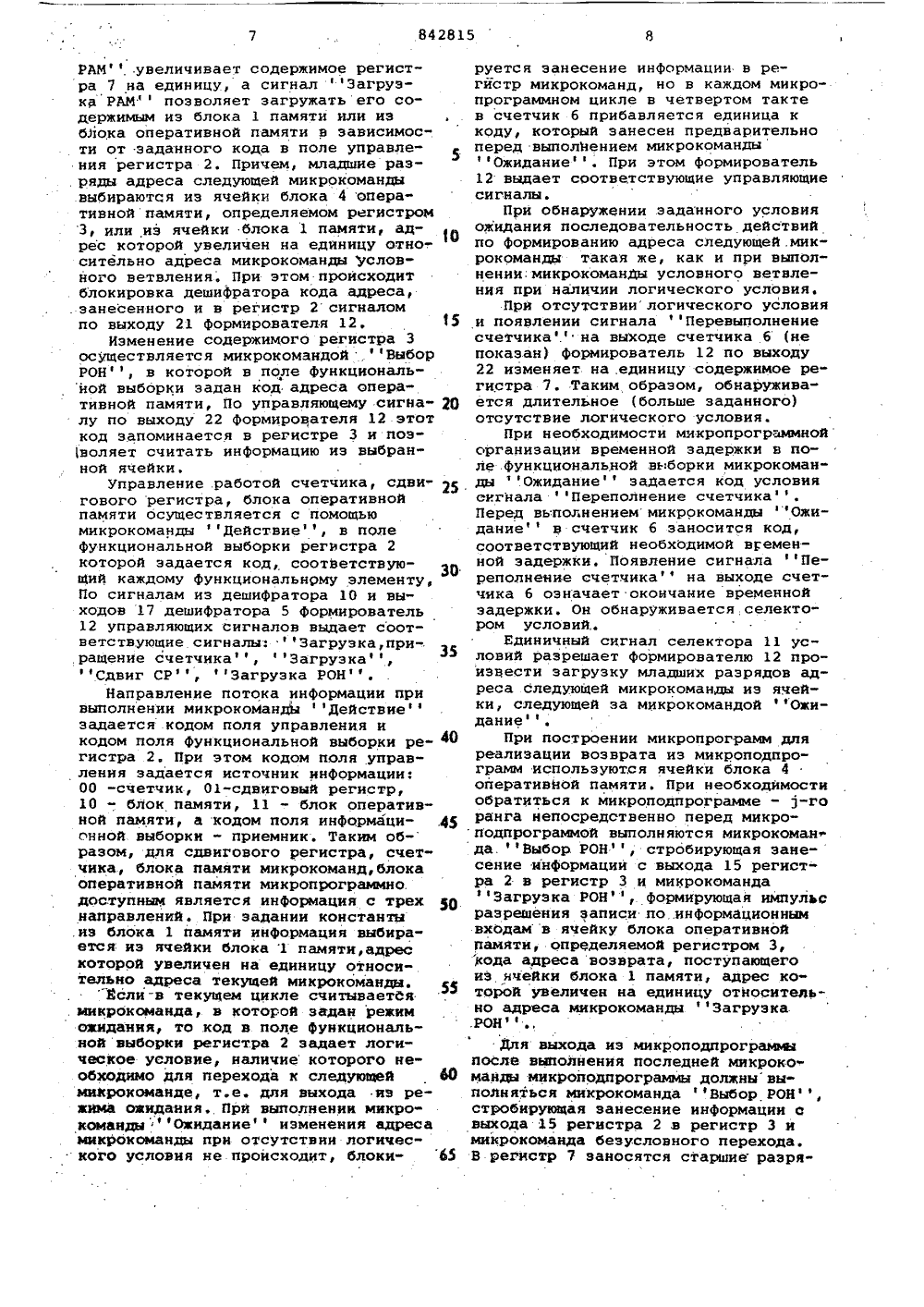

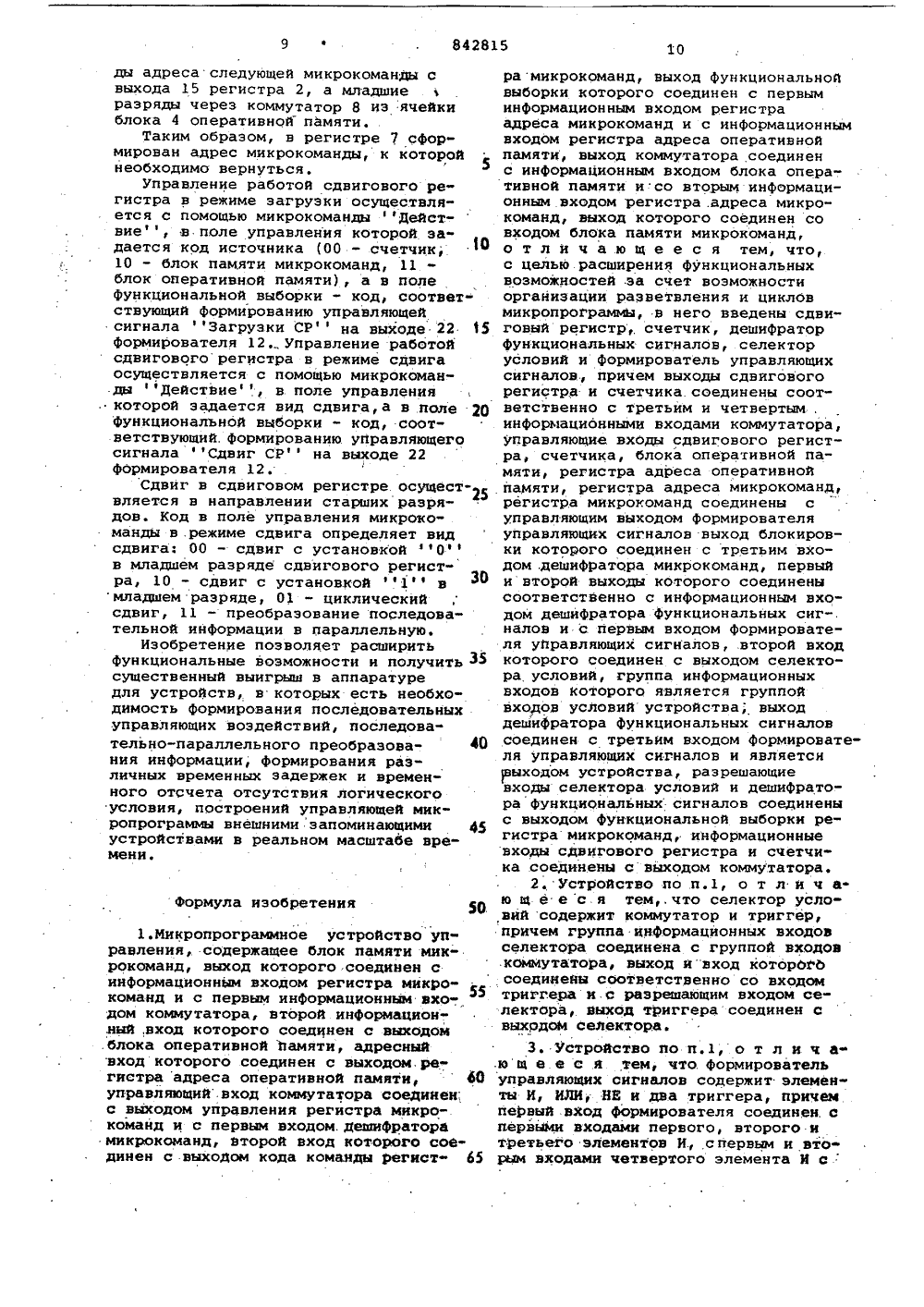

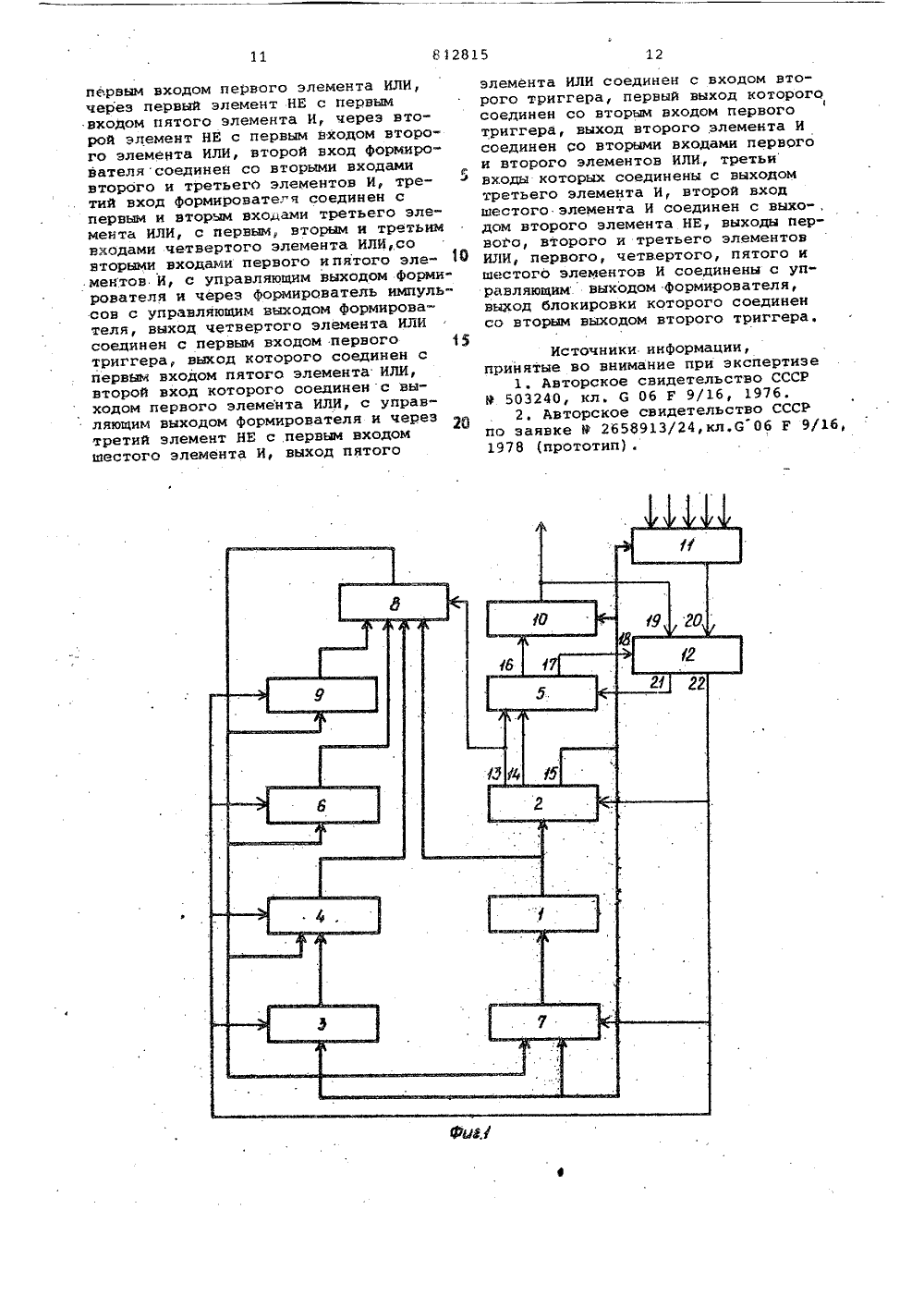

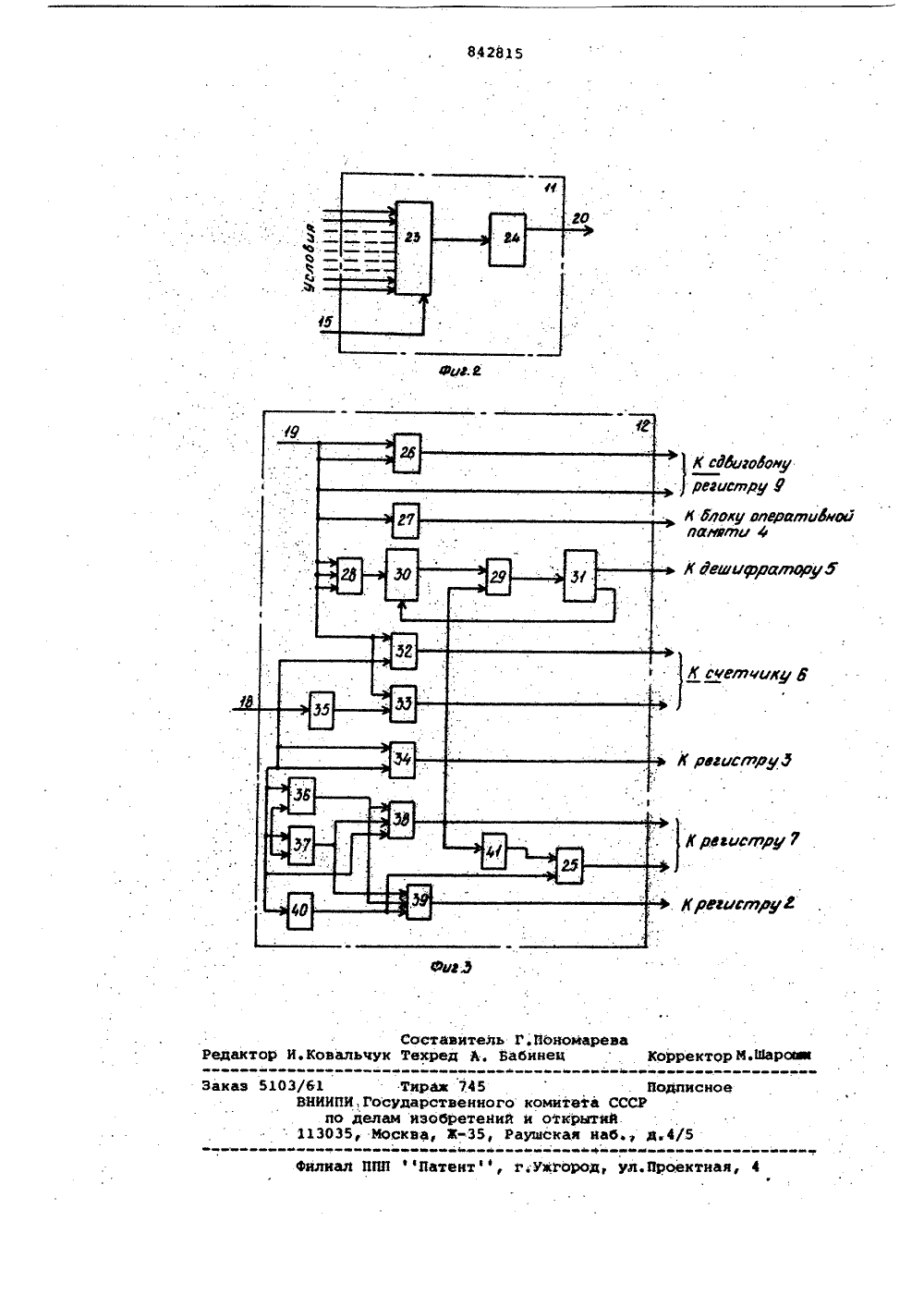

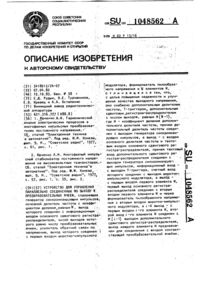

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ Сешеа СеаетскииСоциалистическихРеспубинк 1 ц 842815 в,"ф(51)М3 с присоедимвмием заявки Ив 6 06 Р 9/22Гвсуяавствеянмй явмятет СССР яв ямви нзобретеянй я етярытяй(23) Приоритет Опубликовамо 3006 В 1, Бюллетень М 9 24 Дата опубликования описания 300681(7) Заявит ОЕ УСТРОЙСТВО УПРАВЛЕНИ ИКРОПРОГ Изобретение относится к вычисли,.тельной. технике, в частности к микропрограммным устройствам управления.Известно микропрограммное устрой,ство управления, содержащее блок памяти микрокоманд, регистр адреса мик. рокоманд, регистр микрокоманд, дешифратор кода микрокоманд, элементы И, ,ИЛИ Ц,Однако для .формирования младших разрядов адреса следующей микрокоманды используются.или разряды поля ветвления, или младшие разряды поля ад" реса, что увеличивает затраты обо.рудования..Наиболее близким к изобретению по технической сущности и достигаемОму результату является микропро граммиое устройство управления, со-держащее память микрокоманд, регистр микрокоманд, регистр адреса микро- коканды, коюеутатор, оперативную память, дешифратор векрокоманды, регистрадреса оперативной памяти,2.Однако функциональные воэможности такого устройства ограничены.Цель изобретения " расширение функциональных возможностей за. счет, воэможности организация разветвления я циклов микропрограммы. 2Эта цель достигается тем, что вмикропрограммное устройство управления, содержащее -блок памяти микрокоманд, выход которого ссединен с инФормационным входом регистра микро.команд н с первым инФормационнымвходом коммутатора, второй информационный вход которого соединен с выходом блока оперативной памяти, адресный вход которого соединен с выходом. регистра адреса оперативной памктй, управляющий вход коммутатора.соединен с.выходом управления регистра микрокоманд и .с первым входом 1 дешифратора микрокоманд, второй, входкоторого соединен с выходом кода команды регистра микрокоманд, выходфункциональной выборки которого соединен с первым информационным входом 29 регистра адреса микрокоманд н с инфор".мационным входом .регистра адреса оперативной памяти, выход коммутаторасоединен с информационным входом блока оперативной памяти и со вторыминаф формационным входом регистра адресамикрокоманд, выход которого соединенсо входом блока памяти микрокоманд,введены сдвиговый регистр, счетчик,дешифратор функциональных сигналов, М селектор условий и формирователь ут(равляющих сигналов, причем выходысдвигового регистра и счетчика соединены соответственно с третьим и четвертым информационными входами ком"мутатора, управляющие входы сдвигового регйстра, счетчика, блока опера"тивной памяти, регистра, адреса опе(ративной памяти, регистра адреса микрокоманд регистра чкрокоманд соединены о управляющим выходом формирователя управляющих сигналов, выходблокировки которого соединен с третьим входом дешифратора микрокоманд,первый и второй выходы которого соединены соответственно с информационным входом дешифратора функциональных сигналов и с.первым входом формирователя управляющих сигналов,второй вход которого соединен с выходом селектора условий, группа. инФормационных входов которого является группой входов условий устройства, 2 Овыход дешифратора Функциональных сиг"налов соединен с третьим входом Формирователя управляющих сигналов и является выходом устройства, разрешающие входы селектора условий и дешиф,ратора Функциональных сигналов соединены с выходом Функциональной выборки регистра микрокоманд, информационные входы сдвигового регистра .исчетчика соединены с выходом коммутатора,Кроме того, селектор условий содержит коммутатор и триггер, причемгруппа информационных входов селектора соединена с группой входов коммутатора, выход и вход которого соеди- З 5нены соответственно с входом тригге.ра и с разрешающим входом селектора,выход триггера соединен с выходом селектора,Кроме того, Формирователь.управля Оющих сигналов содержит элементы И,ИЛИ, НЕ и два триггера, причем пер.вый вход формирователя соединен спервыми входами первого, второго итретьего элементов И, с первым и 45лторьм входами четвертого элемента И,с первым входом первого элемента ИЛИ,через первый элемент НЕ с первым входом пятого элемента И, через второйэлемент НЕ с первым входом второго Оэлемента ИЛИ, второй вход Формирователя соединен со вторыми входами второго и третьего элементов И, третийвход Формироваеля соединен с первым и вторыа входами третьего элемента ИЛИ, с первым, вторым и третьимвходами четвертого элемента ИЛИ, совторыми входами первого и йятого элементов И, с управляющим выходом Формирователя и,.череэ Формирователь импульсов с управляющим выходом форми- ВО.рователя, выход четвертого элементаИЛИ соединен с первым входом первоготриггера, выход которого соединенс первым входом пятого элемента ИЛИ,второй вход которого соединен с выходом первого элемента ИЛИ, с управляющим выходом формирователя и черезтретий элемент НЕ с первым входом шеетого элемента И, выход пятого элемента ИЛИ соединен с входом второготриггера, первый выход которого соединен со вторым входом первого триггера, выход второго элемента И сое"динен со вторыми входами первого ивторого элементов ИЛИ, третьи входыкоторых соединены с выходом третьегоэлемента И, второй вход шестого элемента И соединен с выходом второгоэлемента НЕ, выходы первого, второгои,третьего элементов ИЛИ, первого,четвертого, пятого и шестого элементов И соединены с управляющим выходом формирователя, выход блокировкикоторого соединен со вторым выходомвторого триггера.На Фиг,.1 представлена блок-схемаустройства; на фиг.2 - схема селектора условий 1 на фиг.3 - схема формирователя управляющих сигналов.Устройство состоит из блока 1 памяти микрокоманд, регистра 2 микрокоманд, регистра 3 адреса оперативной памяти, блока 4 оперативной памяти, дешифратора 5, микрокоманд,счетчика 6, регистра 7 адреса микрокоманд, коммутатора 8, сдвиговогорегистра 9, дешифратора 10 функциональных сигналов, селектора 11 условий, Формирователя 12 управляющихсигналов, а также содержит выходы13-15 регистра микрокоманд, выходыХб и 17 дешифратора микрокоманд,входы 18-20 и выходы 21 и 22 формирователя управляющих сигналов,Выход 13 является выходом поля управляющим коммутатором, выход 14 разряды поля кода .команды, выход 15- выход поля функциональной выборки, выход 21- сигнал блокировки дешифрации микрокоманды, выход 22 - является выходом сигналов, управляющих работой регистра микрокоманд, регистра адреса микрокоманд, регистра адреса оперативной памяти, оперативной памяти, счетчика, сдвигового регистра,Схема селектора 11 условий (фиг.2) включает .в себя коммутатор 23 и триггер 24. При выполнении микрокоманд Ус- . ловное ветвление и .фОжидание четчрехразрядный код анализируемого условия по выходу 15 регистра 2 микрокоманд позволяет получать на выходе коммутатора 23 истинное значение входного условия, которое запоминается на триггере 24,Схема формирователя 12 управляющих сигналов (Фиг.З) включает В себя элемент И 25, элемент ИЛИ 2 бформи" рователь 27 импульсов, элементы ИЛИ 28 и 29, триггеры 30 и 31, элементй И 32"34, элемент НЕ 35, элементы И 36 и 37, элементы ИЛИ 38 и 39, эле-менты НЕ 40 и 41. и работает следующим образом.Сигнал Загрузка РАМ на выходе элемента ИЛИ 38 формируется при выполнении микрокоманд безусловного пе" рехода (по входу 18),при выполнении микрокоманд Условное ветвление и Ожидание и обнаружении заданного условия и по входу 20 через элемент И 37.или заданного неусловия по входу 20 через элемент И 36.Сигнал фПриращение РАМ на вхо" де элемента И 25 вырабатывается при выполнении любой микрокоманды (на выходе элемента НЕ 40 единичное значение), кроме микрокоманды Ожидание и при отсутствии условий для 15 формирОвания сигнала Загрузка РАМна выходе элемента ИЛИ 38.Сигнал Загрузка РАМ на выходе элемента ИЛИ 39 формируется после выполнения любой микрокоманды, кро О ме микрокоманды Ожидание (при этом иа выходе, элемента НЕ 40.значение логического нуля) и если не обнаружены заданные микрокомандной Ожидание условия (на выходе элементов И 36 и И 37 значения логических нулей).Сигнал Выбор РОН, на выходе элемента И 34 формируется при совпадении сигналов с дешифратора 5 по входу 18, Сигналы Загрузка счетчика на выходе элемента И 32 и Приращение счетчика на выходе элемента И 33 вырабатывается соответственно при наличии и отсутствии сигнала на входе 18 и при появлении З 5 сигнала Синхронизация счетчика на входе 19 из дешифратора 10,Сигнал ффСинхронизация СР на выходе элемента ИЛИ 26 совместно с единичным сигналом Загрузка СРф по входу 19 .осуществляет параллельную загрузку информации в сдвиговый регистр 9, а с нулевым сигналом Загрузка .СР - сдвиг информации.Сигнал Загрузка РОН на выхо де Формирователя 27 импульсов запускается по входу 19 иэ дешифратора 10.Сигнал Блокировка дешифрацииф на выходе триггера 31 устанавливает ся через элемент ИЛИ 29 или единичным сигналом 1 Загруэка, РАМ и по выходу элемента ИЛИ 38, или единичным сигналом триггера 30, который устанавливается через элемент ИЛИ 2855 сигналами .Загрузка СР, Загрузка РОКф и Синхронизация счетчика по.входу 19,Устройство работает следующим образом.Микрокоманда,выбираемая из блока 60 памяти 1 по адресу, хранимому в регистре 7,: засылается в регистр 2 по управляющему сигналу выхода 22 Формирователя 12 Выбранная микрокоманда.расшифровывается в дешифраторе 5, 65 формируя соответствующие сигналы иовыходам 16 и 17.Микрокоманда состоит из поля управления .(выход 13), поля кода команды (выход 14), поля функциональнойвыборки (выход 15) . Адрес очередноймикрокоманды формируется в регистре7 адреса микрокоманды. При выполнениимикрокоманд, кроме микрокоманд безусловного перехода и условйого ветвления при наличии логического условия, единичный сигнал ПриращенчеРАМф по выходу 22 формирователя 22перед выполнением текущей микрокоманды .разрешает формирование адреса следующей микрокоманды увеличением наединицу текущего адреса микрокоманды.Если выбрана микрокоманда Действиеф, то она через выходы 13 и 14регистра 2 расшифровывается в дешифраторе 5, а выход 15 регистра 2, задавая код функции (действия), поступает на вход дешифратора 10, на выходе которого формируется сигнал,соответствующий заданному коду. Дешифратор 10 построен по мультиплексному гринципу,Если выполняется микрокоманда безусловного перехода, то в регистр 7заносятся старшие разряды адреса следующей микрокоманды с выходом 15 регистра 2 микрокоманды, а младшие разряды череЗ .коммутатор 8 из блока 1памяти при задании в поле управлен:"кода 10 (.выход 13) регистра 2 микрокоманд или блока оперативной памяти4 - при задании кода 11, Причем,младшие разряды адреса следующеймикрокоманды выбираются из ячейкиблока 4 оперативной памяти, определяемой регистром 3, или из ячейки блока 1 памяти, адрес которой увелина единицу относительно адреса ;икрокоманды безусловного перехода. Приэтом происходит блокировка дешиФрации кода адреса, занесенного и в регистр 2 сигналом по выходу 21 формирователя 12.При выполнении микрОкоманды условного ветвления в поле функциональной выборки регистра 2 задается код условия, в Поле управления - знак условия и направление, по которому из- влекается адрес ветвления. Селектор 11 условий позволяет определить наличие или отсутствие в данный момент заданного условия выдачей соответственно единичного и нулевого сигнала на выходе селектора 11, который пода- ется на вход формирователя 1.2.Формирователь 12, сравнивая сиг-. налы, поступившие из селектора 11 .Условий и дешифратора 5 по выходу 17, выдает по выходу 22 сигнал Приращение РАМф, еслИ произошло их несов" падение, т.е. задако отсутствие условия; а оно обнаружено., или сигнал ЗагрузкаРАМ, если заданное условие обнаружено. Сигнал ПриращениеРАМф. увеличивает содержимое регистра 7 на единицу, а сигнал Загрузка РАМ позволяет загружать его содержимым из блока 1 памяти или из блока оперативной памяти в зависимости от заданного кода в поле управления регистра 2Причем, младшие раз. ряды адреса следующей микрокоманды выбираются из ячейки блока 4 оперативной памяти, определяемом регистром 3, или иэ ячейки блока 1 памяти, адрес которой увеличен на единицу отно-. сительно адреса микрокоманды условного ветвления. При этом происходит блокировка дешифратора кода адреса, . занесенного и в регистр 2 сигналом по выходу 21 формирователя 12, 15Изменение содержимого регистра 3 осуществляется микрокомандой Выбор РОН, в которой в поле функциональной выборки задан код адреса оперативной памяти, По управляющему сигна- Щ лу по выходу 22 Формирователя 12 этот код запоминается в регистре 3 и поз(воляет считать информацию из выбран ной ячейки.Управление работой счетчика, сдвигового регистра, блока оперативной памяти осуществляется с помощью микрокоманды Действие, в поле функциональной выборки регистра 2 которой задается код, соответствующий каждому функциональнрму элементу, По сигналам из дешифратора 10 и выходов 17 дешифратора 5 формирователь 12 управляющих сигналов выдает соответствующие сигналы: фЗагрузка,приращение счетчика, Загрузка, Сдвиг СРф, Загрузка РОНф.Направление потока инФормации при выполнении микрокоманды Действие задается кодом поля управления и кодом поля функциональной выборки ре О гистра 2. При этом кодом поля управления задается источник информации: 00 -счетчик, 01-сдвиговый регистр, 10 - блок памяти, 11 - блок оперативной памяти, а кодом поля информаци- .4 онной выборки - приемник. Таким об- разом, для сдвигового регистра, счетчика, блока памяти микрокоманд,блока оперативной памяти микропрограммно. доступным является информация с трех щ. направлений. При задании константы .из блока 1 памяти информация выбирается иэ ячейки блока 1 памяти, адрескоторой увеличен на единицу относи-.тельно адреса текущей микрокоманды. 55Если-в текущем цикле считываетбя .микрокомаида, в которой задан режим ожидания, то код в поле функциональной выборки регистра 2 задает логическое условие, наличие которого необходимо для перехода к следующей ЬО микрокоманде, т.е. для выхода иэ режйма ожидания, При выполнении микро- команды ффОжидание изменения адреса микрокоманды при отсутствии логического условия не происходит, блоки руется занесение информации в регйстр микрокоманд, но в каждом микропрограммном цикле в четвертом тактев счетчик б прибавляется единица ккоду, который занесен предварительноперед выполнением микрокомандыОжидание, При этом формирователь12 выдает соответствующие управляющиесигналы,При обнаружении заданного условияожидания последовательность действийпо формированию адреса следующей.микрокоманды такая же, как и при выполнении микрокоманды условного ветвления при наличии логического условия.При отсутствиилогического условияи появлении сигнала 1 ПеревыполнениесчеТчика. на выходе счетчика б (непоказан) формирователь 12 по выходу22 изменяет на .единицу содержимое регистра 7. Таким образом, обнаруживается длительное (больше заданного)отсутствие логического условияПри необходимости микропрограммнойсрганизации временной задержки в поле .функциональной ввборки микрокомаи"ды Ожидание задается код условиясигнала Переполнение счетчика.Перед вьполнением микрокоманды фОжидание в счетчик б заносится код,соответствующий необходимой временной задержки. Появление сигнала Переполнение счетчикаф на выходе счетчика б означает окончание временнойзадержки. Он обнаруживается селектором условий,.Единичный сигнал селектора 11 условий разрешает формирователю 12 произвести загрузку младших разрядов адреса следующей микрокоманды иэ ячейки, следующей за микрокомандой фОжиданиеПри построении микропрограмм дляреализации возврата из микроподпрограмм используются ячейки блока 4оперативной памяти. При необходимостиобратиться к микроподпрограмме - 3-горанга непосредственно перед микро"подпрограюиой выполняются микрокоманда Выбор. РОН, стробирующая заие"сение информации с выхода 15 регистра 2 в регистр 3 и микрокомандаЗагрузка РОН, формирующая импульсразрешения записи поинформационнымвходам в ячейку блока оперативнойпамяти, определяемой регистром 3,кода адреса возврата, поступающегоиз ячейки блока 1 памяти, адрес которой увеличен на единицу относительно адреса мккрокоманды Загрузка..РОН 1.,Для выхода иэ микроподпрограмаюпосле вьаолнения последней микрокоманды микроподпрограммы должнывыполняться микрокоманда ффВыбор РОНф,стробирующая занесение информации свыхода 15 регистра 2 в регистр 3 имикрокоманда безусловного перехода.В регистр 7 заносятся старшие разряды адреса следующей микрокоманды с выхода 15 регистра 2, а младшие разряды через коммутатор 8 из ячейки блока 4 оперативной памяти.Таким образом, в регистре 7 сформирован адрес микрокоманды, к которой необходимо вернуться.5Управление работой сдвигового регистра в режиме загрузки осуществля" ется с помощью микрокоманцы Действиеф, в поле управления которой задается код источника (00 - счетчик, О 10 " блок памяти микрокоманд, 11 блок оперативной памяти), а в поле функциональной выборки - код, соответствующий формированию управляющей сигнала Загрузки СР на выходе 22 15 формирователя 12, Управление работой сдвигового регистра в режиме сдвига осуществляется с помощью микрокоманды Действие , в поле управления которой задается вид сдвига, а в поле 2 О функциональной выборки - код, соответствующий. Формированию управляющего сигнала 1 Сдвиг СРф на выходе 22 формирователя 12Сдвиг в сдвиговом регистре осуществляется в направлении старших разрядов. Код в поле управления микрокоманды в .режиме сдвига определяет вид сдвига: 00 - сдвиг с установкой 0 в младшем разряде сдвигового регист" ра, 10 - сдвиг с установкой 1 фф в младшем разряде, 01 - циклический сдвиг, 11 - преобразование последовательной информации в параллельную.Изобретение позволяет расширить функциональные возможности и получить З 5 существенный выигрыш в аппаратуре для устройств, в которых есть необходимость формирования последовательных управляющих воздействий,оследовательно-параллельного преобразова О ния информации, формирования различных временных задержек и временного отсчета отсутствия логического условия, построений управляющей микропрограммы внешними запоминающими 45 устройствами в реальном масштабе времени.формула изобретения501. Микропрограммное ус тройство управления, содержащее блок памяти микрокоманд, выход которого соединен с информационным входом регистра микро" команд и с первым информационным входом коммутатора, второй информационвый,вход которого соединен с выходом .блока оперативной памяти, адресный вход которого соединен с выходом.ре" гистра адреса оперативной памяти, 60 управляющий .вход коммутатора соединен: с выходом управления регистра микро- команд и с первым входом. дешифратора микрокоманд, второй вход которого соединен с выходом кода команды регйст ра микрокоманд, выход функциональной выборки которого соединен с первым информационным входом регистра адреса микрокоманд и с информационным входом регистра адреса оперативной памяти, выход коммутатора соединен с информационным входом блока оперативной памяти и со вторым информационным входом регистра .адреса микро- команд, выход которого соединен со входом блока памяти микрокоманд, о т л и ч а ю щ е е с я тем, что, с целью. расширения функциональных возможностей .эа счет воэможности организации разветвления и циклов микропрограммы, в него введены сдвиговый регистр, счетчик, дешифратор функциональных сигналов, селектор условий и формирователь управляющих сигналов, причем выходы сдвигового регистра и счетчика соединены соответственно с третьим и четвертым . информационными входами коммутатора, управляющие входы сдвигового регистра, счетчика, блока оперативной памяти, регистра адреса оперативной памяти, регистра адреса микрокоманд, регистра микрокоманд соединены с упраВляющим выходом формирователя управляющих сигналов выход блокировки которого соединен с третьим входом .дешифратора микрокоманд, первый и второй выходы которого соединены соответственно с информационным входом дешифратора Функциональных сиг-. налов и с первым входом формирователя управляющих сигналов, второй вход которого соединен с выходом селектора условий, группа информационных входов которого является группой входов условий устройства; выход дешифратора функциональных сигналовсоединен с третьим входом формирователя управляющих сигналов и являетсн выходом устройства, разрешающие входы селектора условий и дешифратора функциональных сигналов соединены с выходом функциональной выборки ре" гистра микрокоманд, информационные входы сдвигового регистра и счетчика .соединены с выходом коммутатора.2. Устройство по п.1, о т л и ч аю щ е е с я тем,.что селектор условий содержит коммутатор и триггер, причем группа инФормационных входов селектора соединена с группой входов .коммутатора, выход и вход которогЬ соедииейы соответственно со входом триггера и.с разрешающим входом селектора, выход триггера соединен с выхрдом селектора.3. Устройство по п.1, о т л и ч а.ю щ е е а .я тем, что. Формирователь управляющих сигналов содержит элементы И, ИЛИ, НЕ и два триггера, причем первый .вход Формирователя соединен. с первыми входами первого, второго и третьего элементов И., спервым и вторьак входами четвертого элемента Н спервым входом первого элемента ИЛИ,через первый элемент НЕ с первымвходом пятого элемента И, через второй элемент НЕ с первым Входом второго элемента ИЛИ, второй вход формирователя соединен со вторыми входамивторого и третьего элементов И, третий вход формирователя соединен спервым и вторым входами третьего элемента ИЛИ, с первым, вторым и третьимвходами четвертого элемента ИЛИ,совторыми входами первого и пятого эле О.ментов И, с управляющим выходом форми"рователя и через формирователь импульсов с управляющим выходом формирователя, выход четвертого элемента ИЛИсоединен с первым входом первого 15триггера, выход которого соединен спервым входом пятого элемента ИЛИ,второй вход которого соединен с выходом первого элемента ИЛИ, с управляющим выходом формирователя и черезтретий элемент НЕ с .первым входомшестого элемента И, выход пятого элемента ИЛИ соединен с входом второго триггера, первый выход которогосоединен со вторым входом первоготриггера, выход второго элемента Исоединен со вторыми входами первогои второго элементов ИЛИ, третьивходы которых соединены с выходомтретьего элемента И, второй входшестого элемента И соединен с выхо-,дом второго элемента НЕ, выходы первоГо, второго и третьего элементовИЛИ, первого, четвертого, пятого ишестого элементов И соединены с управляющим. выходом формирователя,выход блокировки которого соединенсо вторым выходом второго триггера. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР 9 503240, кл. 6 06 Р 9/16, 1976. 2, Авторское свидетельство СССР по заявке В 2658913/24,кл.6 06 Р 916,1978 (прототип).842815 с. К Феыирралиоу Х ююж гзиощ 7 у Составитель Г.ВонокареваРедактор И.Ковальчук Техред А. БабинецХОРректорйвШарю евею ясно роектн ал ППП ффПатент, г. каэ 5103/61 Тираж ВНИИПИ Государс по делам иэо 113035 Москва, еввЮЕЮ Еа745енного кетений и-35, Рауш рееиелоу УК блоку олерагли 8 нпалли Ф митета СССРоткрытийская иаб., д.4/5

СмотретьЗаявка

2815254, 27.08.1979

КИЕВСКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙИ КОНСТРУКТОРСКИЙ ИНСТИТУТ ПЕРИ-ФЕРИЙНОГО ОБОРУДОВАНИЯ

ЧЕРЕПАНОВ ВИКТОР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 9/12

Метки: микропрограммное, управ-ления

Опубликовано: 30.06.1981

Код ссылки

<a href="https://patents.su/7-842815-mikroprogrammnoe-ustrojjstvo-uprav-leniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управ-ления</a>

Предыдущий патент: Микропрограммное устройство управ-ления

Следующий патент: Многоканальное устройство приоритета

Случайный патент: Установка для моделирования фундаментов сооружений