Сумматор -разрядных к-ичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

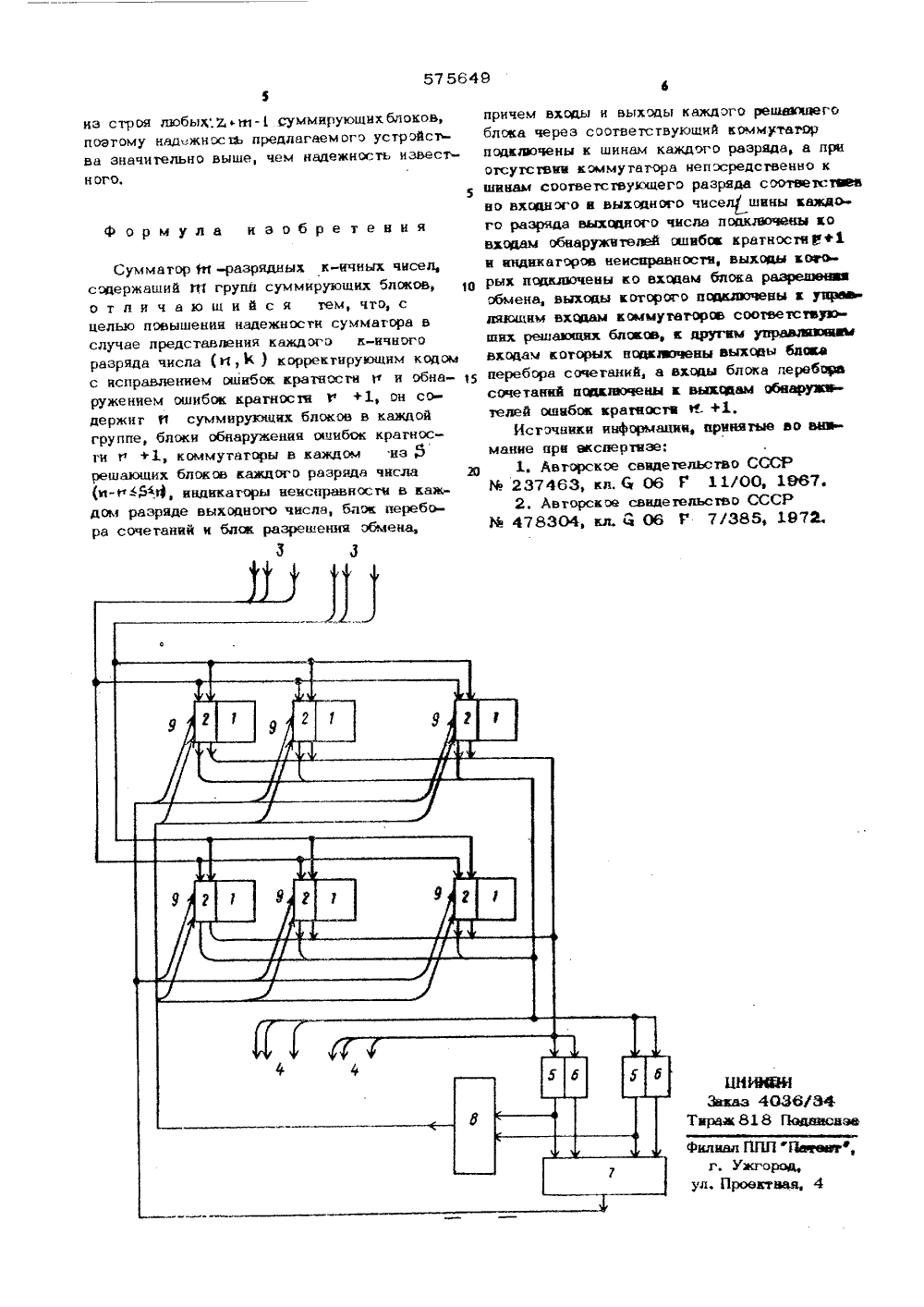

Союз Советских Социалистицеских Республик(22) Заявлено 02.01.74 (21)1986242/18-2с присоединением заявки-385 1/02 Госудерстеенный хамите Совете Мнннстрае СССР но делам изобретений и открытий(45) Дата опубликования описан К, К, Ешиц, А, К, Завэлэкцн, В. 11. Зарэвскцй Е. К. Кферэва ц Т. А. Яснэгорэдская Г В Г 1 е тр эв. 72) Авторы изобретения 1) Заявител 4 ) СУММ А ТОР АЗГ ЯДНЫ Х КЧН кратнэстц 2 + 1 ( м т возникшая в однойиз групп, уже не может быть исправлена,Целью изобретения является пэвышенценадежности сумматора.б Для дэстцжения этой цели предложенныйсумматор сэдержит тт сухмцруюшцх блэкэвв каждой группе, блоки обнаружения эшибоккратнэстц Е +1, коммутаторы в каждом изсуммирующих блоков каждого разряда чис ла ( тт - т" 6 51 т) индикаторы неисправности в каждом разряде выходногэ числа,блок перебора сочетаний и блок разрешения о 1мена, Входы ц выходы каждого суммцруюшегблока через с оэтве тствуюши й к эммута тэр 5 подключены к шинам каждого разряда,а при отсутствии коммутатора непосредственно к шинасоответствующего разряда соответствен н э вхоного и выходного чисел. Шины каждого разрядавыходного числа подключены ко входам блоков 0 обнаружцтелейошйбоккратцэсти г +1 и индикарторов неисправности, выходы которых пэдклчецы ко входам блока разрешения обмена,Выхэды последнего подключены к упрлвлцюцвхэдвм коммутаторов соответствующих сумх 7 руюших блэков, к други управляющим вх: Изобретение относится к эбластн ццфрэвэй вычислительнэй техники и мэжет быть использовано для выполнения арифметических эперашФ над числами счисления с оснэванием й каждая цифра которых представлена самокорректирующимся двоичным кэдэм.Известны устройства обладающие повышенной надежностью, за счет того, что в нихЬвместо отказавшихузлов подключаются резервные. Однако при атом необходимо 1 иметь;запас резервных устройств 11.Наиболее близким техническим решением к изобретению является сумматор нтт- разрядных к- ичных чисел, содержащий ттт групп суммируюших блоков 121.При представлении каждого к - ичнэгэ разряда числа корректирующим двэичным кодом с исправлением ошибок кратности Е и,обнаружением ошибок кратности (+ 1) непол ностью используются возможности исправления ошибок. Этэт способ кодирования позвэлцет исправить максимально ошибку кратности тпрр,по 3 ошибок в каждой группе сумемируюшцх блоков). В то же время ошибка 2 ОП ИСАНИЕ 5 т 5 ввИЗОБРЕТЕН ИЯдам которых подключены выходы блока перебэра сочетаний. Входы блока перебора сочетаний подключены к выходам блоков обнаружения ошибок кратности 2 +1,Структурная схема сумматора представлена на чертеже.Сумматор содержит ю групп пэ И сум"мирующих блоков 1, при чем все суммирующиеблоки, формирующие одновременные двоичныеразряды копов различиьгх к-ичных разрядов выходного числа, идентичны. Входы и выходыб суммирующих блоков 1 в каждой группеИз т 1 блоков (.И.8И ) через соответствуюший кэммутатор 2 подключены кшинам каждого разрядаа выходы и вжды остальных суммирующих блоков 1 непосредственно к шинам соответствующегоразряда входного 3 и выходного 4. чисел,Шины каждого разряда выходного числа 4подключены ко входам блоков обнаружения 5 2 Оошибок кратности х +1 и индикатэровнеисправности в групп решающих блоков. Выхэпы блоков 5 н индикаторов неисправности 6подключены к входам блока разрешения обмене7 суммируюших блоков группы, сэдержаШей г 5ошибку кратности 2+1 с идентичными блокамиисправной группы, Выходблоков 5 подключены ко входам блэка перебора сочетаний 8,Выходы блока разрешения обмена 7 и выхсы блока перебора сочетаний 8 пэдключены з 0к управляющим входам 9 коммутаторовсоответствующих блоков 1,Устройство работает следующим образом,В исходном состоянии, когда все элементы системы исправны, суммирующие блоки1 распределены по группам некоторым образом. При этом коммутатор подключаетвхэды каждогэ блока 1 к шинам соэтветствуюшегэ разряда входного числа 3, а выход атого блэка - к шине соответствующегоразряда вы.сэдного числа 4. Сигналы на выходахблоков 5 и индикатэрэв неисправности 6отсутствуют, блоки разрешения обмена 7и перебора сочетаний 8 находятся в исходном состоянии, 45При возникновении отказов в некоторойгруппе суммирующих блоков 1 выходящихиз строя менее Е + 1 блоков 1, на .выхсдах соответствующих индикаторов неиспрааности 6 появляются сигналы, однако блэки 50разрешения обмена 7 и перебора сочетаний8 остаются в исходном состоянии и перестройка не происходит. При таких же отказахв нескольких группах суммируюших блоковустройство работает аналогично, 55При выходе из строя в некэтэрэй группеЕ +1 суммирующих блоков 1 на выходесээтветствуюшегэ блока обнаружения эшибок5 кратности Е +1 появляется сигнал, который включает блоки разрешения эбмепа 7 и пэреоора сочетаний Я При наличии в сумматоре полностью исправной группы суммируюших блоков 1 блок разрешения обменадает сигнал, разрешающий перестройку сумматора путам обмена суммирующими блоками 1 между атой группой и группой с ошибкой краткости 2+1, При перестройке коммутаторы 2 идентичных суммирующих блоков1, формирующих одноименные двоичныеразряды кодов, соответствующих к-ичныхразрядов выходного числа, переключаютсятаким образом, что блоки меняются местами, т.е, входы и выходы одного блокаподключаются вместо входов и выходовдругого, и наоборот. Перестройка прэизвсь.1дится пэ тактам, И каждом такте некэторая часть суммирующих блоков 1 однойгруппы меняется местами с идентичнымисуммирующими блоками 1 другой группы,Различные кэмбинации переключаюшихся сум1мируюших блоков 1 перебираются такимобразом, чтобы для произвэльных;., +1неисправности блоков 1 нашелся хэтя быодин такт, в котором все эти блоки небудут подключены к одной и той же группе.И этом случае в каждой группе окажетсяне болеенеисправных блоков 1. Кратнэсть эшибки в каждой группе станетменьше Е +1, чтэ позволит исправить ееза счет корректирующих свойств кода.целесообразно в каждом такте переклкчать половину решающих блоков группы вразличных сочетаниях, Максимальнсе числотактов Т, удэвлетворяюшее указанному условию, в этом случае определяется формулой,где символ т означает округление дэ ближайшего большого целого числа.Порядок переключения блоков определяется блоком перебора сочетаний 8, которыйформирует в каждом такте требуемые сочетания блоков 1, Блок перебора сочетаний8 включается пэ сигналу блока 5, когдав некотором такте в результате перестройки кратность ошибки становится меньшеГ +1; сигнал на выходе блока обнаружения ошибок 5 исчезает и блэк перебора сочетаний 8 фиксирует достигнутое состояние.На атом перестройка заканчивается.При пэв торном вэзникн эвеиии ошибкикратности 4+1 процесс пэвторяегся, еслиимеется хотя бы одна целиком исправная группа,Если известное устройство га ра и эработало при отказах Е суммируюших блэкэа и мэглэ выйти из строя при отказе+1 блоков (если, все они принадлежали одной группе), тэ предлагаемое ус гройс,гво гарапти 1 эваииэ работает прп вих.де57 5649 ЦНИК 3 И Заказ 403 б/ЗФТараи 81 8 Поалнонзв ППП юД тфг. Ужгород, Проектная, 4 из строя любых,2,т- с суммируюшихблэхэв, поатому надежнэсМ предлагаемого устрэйства значительно выше, чем надежнссть известногоо.5 Ф ормула изобре гения Сумматор й -разрядных х-ичиых чисел, сэдержаший Ю групп суммирующих блоков, 1 о отличающийся тем,что,с целью повышения надежности сумматора в случае представления каждого к-ичнэгэ разряда числа (т 1, С ) корректирующим кодом с исправлением ошибок кратностии обна ружением ошибок кратности Фф +1, он содержит И суммирующих блоков в каждой группе, блэки обнаружения ошибок кратности ф +1, коммутаторы в каждом из, решающих блоков каждого разряда числа л (н- М, индикаторы неисправности в каж; дом разряде выходного числа, блэк перебора сочетаний и блок разрешения обмена,3 д причем входы и выходы каждого решюощего блока через соответствуюший коммутагаю подключены к шинам каждого разряда, а прн отсутствии коммутатора непэсредсгвенно к шиизм соответствующего разряда сэответстма но входного н выходного чисел шины каждого разряда выходного числа подключены ко входам обнаружителей ошибок кратности р 1 и индикаторов неисправности, выходы которых подуцпочены ко входам блока разреиюваа эбмена, выходы которого подключены к управляющим входам коммутаторов соответствуюЩ Р Щ ЮЕ входам которых нодклочены вьпсовы блакв перебора сочетаний, а вхсды блока перебща сочетаний подключены к выхсФам обнвруювтелей ошибок кратности ф +1.Источники информации, принятые во внимание при мспертизе:1. Авторское свидетельство СССР М 237463, кл. 6 06 Г 11/00, 1987.2. Авторское свидетельство СССР Ж 478304, кл. а 06 Г 7/385 1972

СмотретьЗаявка

1986242, 02.01.1974

ВОЕННАЯ ОРДЕНОВ ЛЕНИНА, ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И СУВОРОВА АКАДЕМИЯ ИМЕНИ Ф. Э. ДЗЕРЖИНСКОГО

ЕЩИН КОНСТАНТИН КОНСТАНТИНОВИЧ, ЗАВОЛОКИН АНАТОЛИЙ КУЗЬМИЧ, ЗАРОВСКИЙ ВИТАЛИЙ ИВАНОВИЧ, ПЕТРОВА СВЕТЛАНА БОРИСОВНА, ЮФЕРОВА ЕВГЕНИЯ КИРИЛЛОВНА, ЯСНОГОРОДСКАЯ ТАТЬЯНА АЛЕКСАНДРОВНА

МПК / Метки

МПК: G06F 7/385

Метки: к-ичных, разрядных, сумматор, чисел

Опубликовано: 05.10.1977

Код ссылки

<a href="https://patents.su/3-575649-summator-razryadnykh-k-ichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор -разрядных к-ичных чисел</a>

Предыдущий патент: Устройство для вычисления значения полинома -степени

Следующий патент: Частотно-импульсное алгебраическое суммирующее устройство

Случайный патент: Гидробак