Устройство для исправления ошибок кратности и обнаружения ошибок кратности

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1619411

Авторы: Кауров, Неумывакина, Попова

Текст

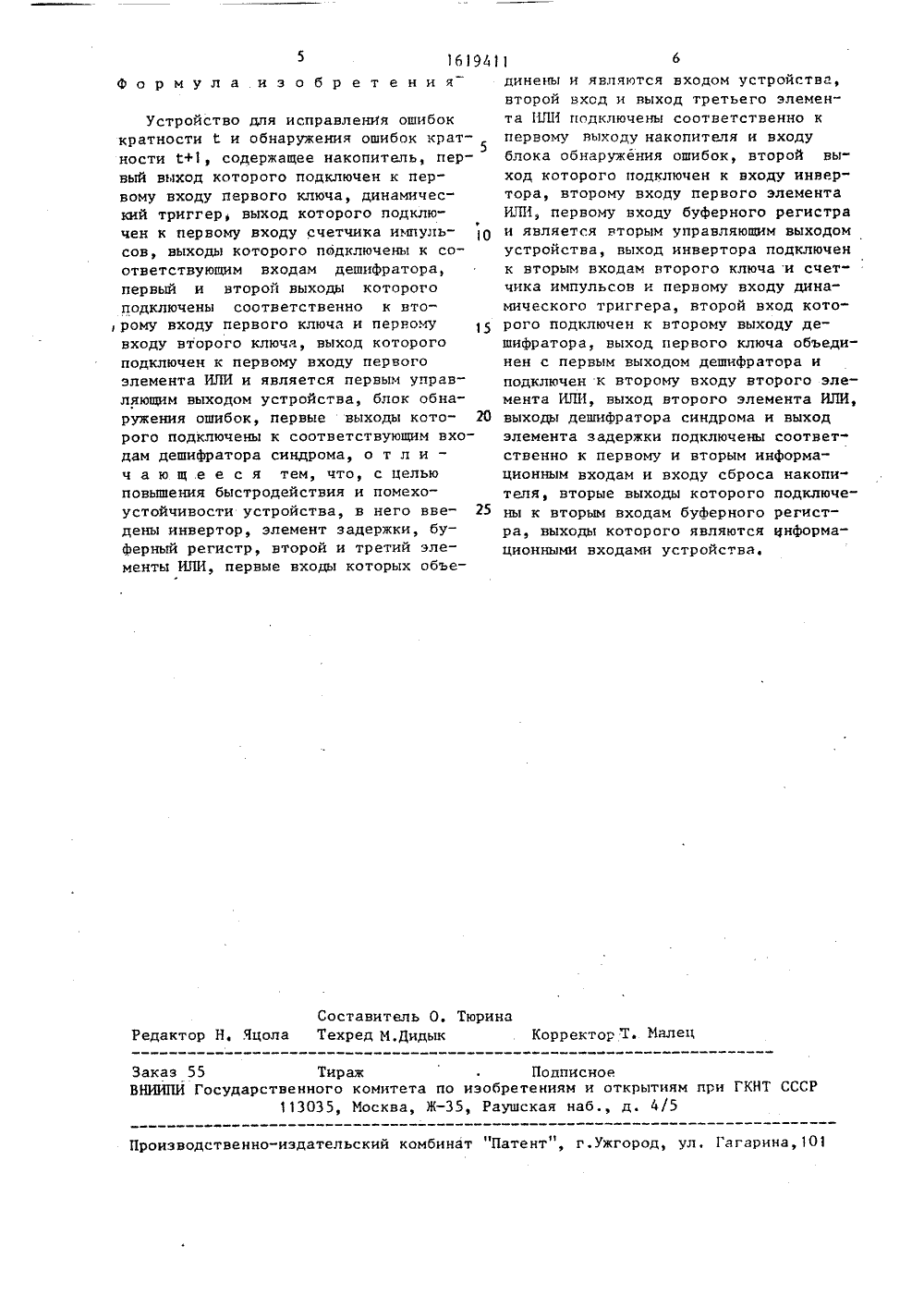

ПИСАНИЕ ИЗОБРЕТ СВИДЕТЕЛЬСТВ Н АВТОРСН(53) 621.374(088,Унститут радиК. Янгеля ектумывакина ШИ- БОК ГОСУДАРСТ 8 ЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ ГННТ СССР(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОБОК КРАТНОСТИ С И ОБНАРУЖЕНИЯ ОШИКРАТНОСТИ с+1,БО 1619411 содержит накопитель 1, буферный регистр 2, блок 3 обнаружения ошибок,состоящий из делителя 4 и элементаИЛИ"НЕ 5, дешифратор 6 синдрома,динамический триггер 12, счетчик 13импульсов, дешифратор 14, инвертор15,элементы ИЛИ 7, 8 и 9, два ключа 10 и 11, элемент 16 задержки. Поставленная цель достигается за счеттого, что исправление ошибок и считывание информационных разрядов декодированной кодовой комбинации производится в параллельном коде, а такжеза счет одновременного осуществлениязаписи в накопитель кодовой комбинации, поступающей непосредственно впоследовательном коде, и получениясиндрома путем деления кодовой комбинации на порождающий полином в блоке 3 обнаружения ошибок. 1 ил.ному. Изобретение относится к технике пе.редачи данных и может использоватьсяв устройствах защиты от ошибок аппаратуры передачи данных.Пель изобретения - повышение быстродействия и помехоустойчивости устройства.На чертеже представлена структурная схема устройства для исправленияошибок кратности С и обнаружения ошибок кратности 1+1,Устройство содержит накопитель 1,буферный регистр 2, блок 3 обнаружения ошибок, содержащий делитель 4 иэлемент ИЛИ-НЕ 5, дешифратор б синдрома, элементы ИЛИ 7-9, ключи 10 и 11,динамический триггер 12, счетчик 13импульсов, дешифратор 14, инвертор 15и элемент 16 задержки. 20Устройство работает следующим образом.На вход устройства поступает принятая кодовая комбинация, при этом одновременно происходит ее запись в после довательном коде через элемент ИЛИ 7в накопитель 1 и деление на порождающий полином в делителе 4, в которыйкодовая комбинация поступает в последовательном коде через элемент ИЛИ 8 ф 30В случае отсутствия ошибок послепервого цикла деления на выходе блока обнаружения ошибок получают нулевой синдром, а на выходе элементаИЛИ-НЕ 5 - логическая "1", поступающая на вход буферного регистра 2 иразрешающая перезапись в него в параллельном коде информационных разрядов кодовой комбинации из накопителя 1. После этого информационная часть 40кодовой комбинации может быть считана из буферного регистра 2 в параллельном коде. Сигнал логической "1"с выхода элемента ИЛИ-НЕ 5 через элемент ИЛИ 9 и элемент 16 задержки поступает на вход сброса накопителя 1.Сигнал с второго управляющего выходаустройства может быть использованкак команда разрешения ввода очередной комбинации.50В случае обнаружения ошибок навыходе элемента ИЛИ-НЕ 5 будет логический 0, при этом разрешение наперезапись информационной части кодовой комбинации в буферный регистр 2не выдается. Дешифратор 6 синдрома55ставит в соответствие синдрому, полученному с выходов блока 3 обнаруженияошибок, наиболее вероятное для данно го канала связи сочетание ошибок, которое поступает с выходов дешифратора б синдрома на соответствующиевходы накопителя 1, происходит исправление ошибок в параллельном коде.Сигнал логической "1", поступающий с выходу инвертора 15, устанавливает в исходное состояние счетчик 13импульсов и запускает динамическийтриггер 12, вырабатывающий на своемвыходе последовательность импульсовсо скоростью, обеспечивающей определение синдрома исправляемой кодовойкомбинации за время, равное 1/2 К ,где З.т - скорость телеграфирования.При этом происходит проверка правильности исправления ошибок. Исправленная кодовая комбинация из накопителя1 через элемент ИЛИ 8 поступает в последовательном коде в блок 3 обнаружения ошибок и делится на порождающий полином в делителе 4. При этомключ 10 открыт управляющим сигналомс первого выхода дешифратора 14 и одновременно с делением происходит перезапись исправленной кодовой комбинации в накопитель 1,По окончании второго цикла сигналс второго выхода дешифратора 14, поступая на установочный вход динамического триггера 12, фиксирует его . состояние. Если исправление ошибок осуществлено верно, на выходе блока 3 обнаружения ошибок будет получен нулевой синдром и выдача разрешения на перезапись информационной части исправленной кодовой комбинации из накопителя 1 в буферный регистр 2 и сигнала"Сброс", происходит аналогично описанЕсли имела место ошибка кратности +1, получают ненулевой синдром, на выходе элемента ИЛИ-НЕ 5 - логический "0" (запрещение перезаписи в буферный регистр 2), при этом логическая "1" с выхода инвертора 15 и управляющий сигнал с второго выхода дешифратора 14 открывают ключ 11, на первом управляющем выходе - сигнал логической "1" (" Ошибка" ), который также может быть использован. для разрешения ввода очередной кодовой комбинации. Сигнал "Сброс" в этом случае поступает на вход сброса накопителя 1 через элемент ИЛИ 9 и элемент 16 задержки.Заказ 55 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г.Ужгород, ул, Гагарина,10 5 16194формула изобретения Устройство для исправления ошибок кратностии обнаружения ошибок крат 5 ности 1+1, содержащее накопитель, первый выход которого подключен к первому входу первого ключа, динамический триггер, выход которого подклю"ч чен к первому входу счетчика импульсов, выходы которого подключены к соответствующим входам дешифратора, первый и второй выходы которого подключены соответственно к вто, рому входу первого ключа и первому входу второго ключа, выход которого подключен к первому входу первого элемента ИЛИ и является первым управляющим выходом устройства, блок обнаружения ошибок, первые выходы кото рого подключены к соответствующим входам дешифратора синдрома, о т л и - ч а ю щ е е с я тем, что, с целью повышения быстродействия и помехоустойчивости устройства, в него вве дены инвертор, элемент задержки, буферный регистр, второй и третий элементы ИЛИ, первые входы которых обье 11 6динены и являются входом устройства, второй вход и выход третьего элемен" та ИЛИ подключены соответственно к первому выходу накопителя и входу блока обнаружения ошибок, второй выход которого подключен к входу инвертора, второму входу первого элемента ИЛИ, первому входу буферного регистра и является вторым управляющим выходом устройства, выход инвертора подключен к вторым входам второго ключа и счетчика импульсов и первому входу динамического триггера, второй вход которого подключен к второму выходу дешифратора, выход первого ключа объединен с первым выходом дешифратора и подключен к второму входу второго элемента ИЛИ, выход второго элемента ИЛИ, выходы дешифратора синдрома и выход элемента задержки подключены соответственно к первому и вторым информационным входам и входу сброса накопителя, вторые выходы которого подключены к вторым входам буферного регистра, выходы которого являются информационными входами устройства.

СмотретьЗаявка

4657293, 01.03.1989

ХАРЬКОВСКИЙ ИНСТИТУТ РАДИОЭЛЕКТРОНИКИ ИМ. АКАД. М. К. ЯНГЕЛЯ

КАУРОВ ЛЕОНИД ГРИГОРЬЕВИЧ, НЕУМЫВАКИНА ОЛЬГА ЕВГЕНЬЕВНА, ПОПОВА НАДЕЖДА БОРИСОВНА

МПК / Метки

МПК: H03M 13/02

Метки: исправления, кратности, обнаружения, ошибок

Опубликовано: 07.01.1991

Код ссылки

<a href="https://patents.su/3-1619411-ustrojjstvo-dlya-ispravleniya-oshibok-kratnosti-i-obnaruzheniya-oshibok-kratnosti.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок кратности и обнаружения ошибок кратности</a>

Предыдущий патент: Преобразователь кодов

Следующий патент: Способ обнаружения ошибок и устройство для его осуществления

Случайный патент: Устройство для прокладки трубопроводов