Преобразователь параллельных двоичных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

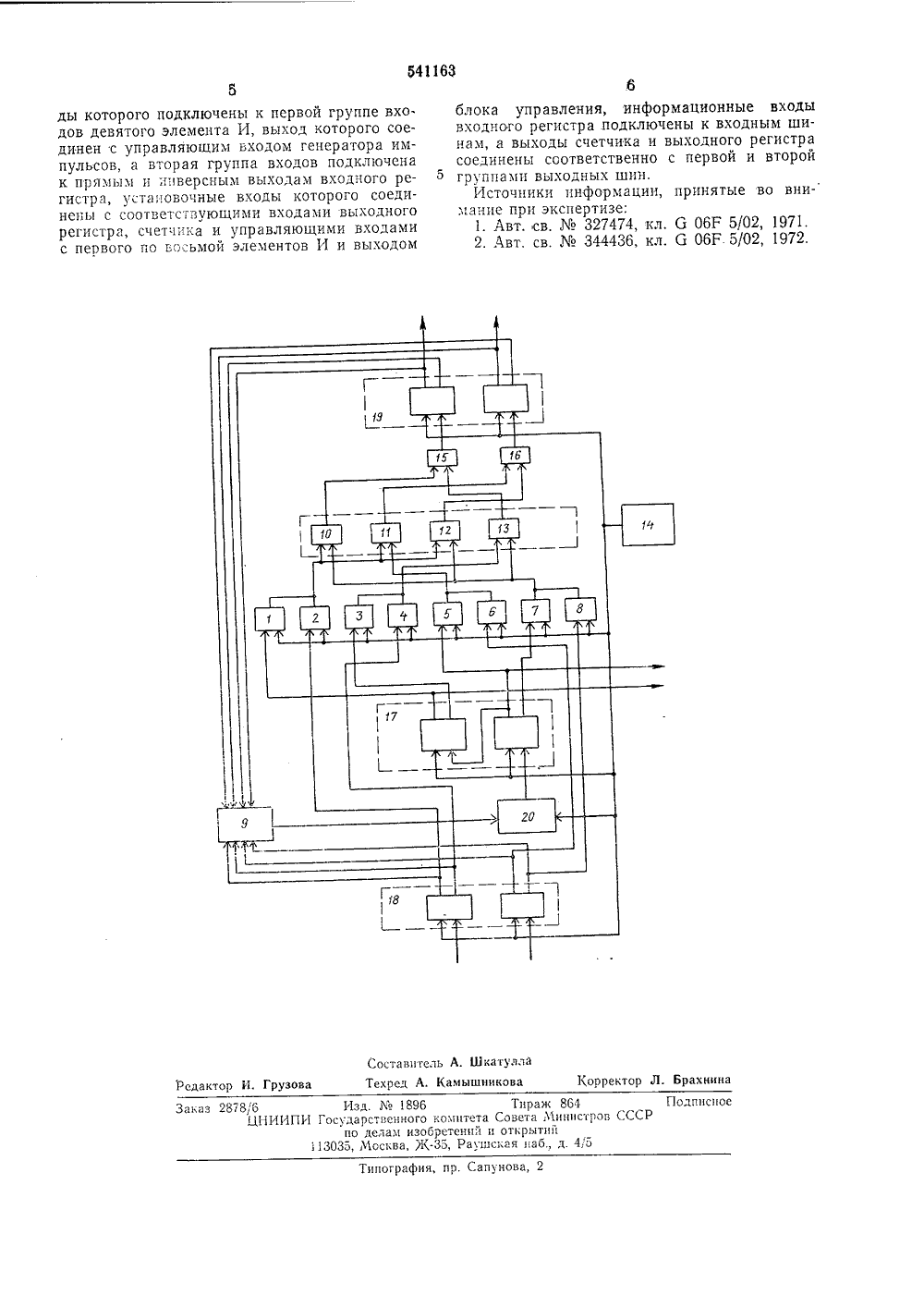

(1) 54 П 63 ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Республикб 1) Дополнительное к авт. свид-ву22) Заявлено 26.03.74 (21) 2008037/24с присоединением заявки Ме -23) Приоритет л. 6 Государственный комитет Совета Министров СССР ло делам изобретений 3) УДК 681.325(08 30.12.76, Бюллетень Ме 4ата опубликования описания 19.01.77 публиковано и открыт 54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНЫХ ДВОИЧНЫХ КОДОВтчисли- преобв в рИзобретение относится к области вь тельной техники и предназначено для разования и-разрядных двоичных кодо разрядные и обратно.Известен преобразователь двоичных кодов 1, содержащий регистр исходного кода, дешифратор, шифратор на ферритовых матпицах, регистр преобразованного кода с детцифратором, дешифратор выбора матриц, выходные элементы, усилитель. С помощью ферритовых матриц, прошитых управляющими шинами, осуществляется формирование преобразованного кода из исходного.Недостатком такого устройства является необратимость преобразования кодов, что делает невозможным его применение при двустороннем обмене информацией.Известен также преобразователь параллельных двоичных кодов 121, наиболее близкий по техническому решению к изобретению, содержащий блок управления и управляющие элементы И,Однако указанный преобразователь имеет большое количество оборудования, что вызвано необходимостью включения активных элементов с двусторонней проводимостью, Кроме того, в состав этих элементов должна быть включена дополнительная коммутационная логика, обеспечивающая изменение направления передачи сигналов через элементы с двусторонней проводимостью,Цель изобретения - повышение коэффициента использования оборудования при преобразовании многоразрядных кодов.Это достигается за счет того, что преобра зователь содержит двухразрядный счетчик,входной и выходной двухразрядные регистры, генератор тактовых импульсов, элементы И и ИЛИ. Прямые выходы первых разрядов счетчика и входного регистра через первый и вто рой элементы И соединены между собой иподключены к первым входам первого, второго и третьего управляющих элементов И. Инверсные выходы первых разрядов счетчика и входного регистра через третий и четвертый 15 элементы И объединены и подключены к первому входу четвертого управляющего элемента И, прямые выходы вторых разрядов счетчика и входного регистра через пятый и шестой элементы И соединены и подключены к 20 второму входу второго управляющего элемента И. Инверсные выходы вторых рязрядов счетчика и входного регистра через седьмой и восьмой элементы И соединены и подключены к вторым входам первого, третьего и четвер того управляющих элементов И, выходы первого и четвертого управляющих элементов И через первый элемент ИЛИ подключены к информационному входу первого разряда выход ного регистра, выходы второго и третьего уп 30 равляющих элементов И через второй элементИЛИ - к информационному входу второго5 10 15 20 25 30 35 40 45 50 55 60 65 разряда выходного регистра, прямые и инвер. сные выходы которого подсоединены к первой группе входов девятого элемента И, выходом связанного с управляющим входом генерато. ра импульсов, а вторая группа входов подключена к прямым и инверсным выходам входного регистра, установочные входы которого соединены с соответствующими входами выходного регистра, счетчика и управляющими входами с первого по восьмой элементов И и выходом блока управления. Информационные входы входного регистра подключены к входным шинам, а выходы счетчика и выходного регистра соединены соответственно с первой и второй группами выходных шин.На чертеже представлен двухразрядный преобразователь параллельных двоичных кодов.Преобразователь содержит элементы И 1 - 9, управляющие элементы И 10 - 13, блок 14 управления, элементы ИЛИ 15, 16, двухразрядный счетчик 17, входной двухразрядный ретистр 18, выходной двухразрядный регистр 19 и генератор 20 импульсов.Двухразрядные (и =2) кодовые комбинации ОО, 01, 10, 11 преобразуются в устройстве в двухразрядные (р=2) кодовые комбинации 10, 00, 11, 01 соответственно и наоборот,Устройство работает следующим образом.При преобразовании и-разрядного кода в р-разрядный и разрядов исходного кода заносятся во входной регистр 18. Потенциалы прямых и инверсных выходов регистра 18 поступают на и-входовые управляющие элементы И 10 - 13 через элементы И 2, 4, 6, 8, открытые блоком 14 управления. В случае совпадения единичных потенциалов на и входах управляющих элементов И 10 - 13 устанавливаются в единичное состояние те разряды выходного регистра 19, информационные входы которых через элементы ИЛИ соединены с выходом того управляющего элемента И, на котором произошло совпадение потенциалов. Остальные разряды регистра 19 остаются в нулевом состоянии. Если, например, на входной регистр 18 поступает код 10, то единичный потенциал появляется на выходах элементов И 2 и 8, затем на выходах управляющих элементов И 10, 12, 13 и устанавливает на выходе регистра 19 код 11.При обратном преобразовании р-разрядный код также заносится во входной регистр 18. Однако в этом случае на входы управляющих элементов И 10 - 13 поступают потенциалы не с выходов регистра 18, а с прямых и инверсных выходов счетчика 17 через элементы И 1, 3, 5, 7, открытые блоком 14 управления.После занесвния р-разрядного кода во входной регистр 18, содержимое и-разрядного счетчика 17 начинает изменяться на 1 по каждому импульсу, поступающему на вход счетчика с генератора 20. После каждой модификации счетчика на 1 осуществляется преобразование и-разрядного кода счетчика в р-разрядный код по рассмотренному алгоритму с той лишь разницей, что на входы управляющих элементов И 10=13 поступают потенциалы с выходов счетчика через элементы И 1, 3, 5, 7, После каждого преобразования элемент И 9 анализирует коды в регистрах 18, 19 на совпадение. Если коды не совпадают, генератор 20 продолжает добавлять 1 к содержимому счетчика 17, после очередного преобразования вновь сравниваются коды элементом И 9 и так до тех пор, пока коды в регистрах 18, 19 не совпадут, после чего элемент И 9 вырабатывает сигнал останова генератора 20. На счетчике 17 фиксируется и-разрядный код, соответствующий принятому р-разрядному коду, Блок 14 управления производит начальную установку счетчика 17, а также входного и выходного регистров перед каждым преобразованием.Предложенная схема двустороннего преобразователя кодов эффективно использует оборудование, причем коэффициент эффективности использования оборудования значительно возрастает при преобразовании многоразрядных кодов за счет того, что оно содержит только и управляющих элементов И, в то время как известное устройство имеет 2"+ подобных элемента, а также 2" элемента с двусторонней проводимостью. Формула изобретенияПреобразователь параллельных двоичных кодов, содержащий блок управления и управляющие элементы И, отличающийся тем, что, с целью повышения коэффициента использования оборудования при преобразовании многоразрядных кодов, он содержит двух- разрядный счетчик, входной и выходной двух- разрядные регистры, генератор импульсов, элементы И и ИЛИ, причем прямые выходы первых разрядов счетчика и входного регистра через первый и второй элементы И соединены между собой и подключены к первым входам первого, второго и третьего управляющих элементов И, инверсные выходы первых разрядов счетчика и входного регистра через третий и четвертый элементы И объединены и подключены к первому входу четвертого управляющего элемента И, прямые выходы вторых разрядов счетчика и входного регистра через пятый и шестой элементы И соединены и подключены к второму входу второго управляющего элемента И, инверсные выходы вторых разрядов счетчика и входного регистра через седьмой и восьмой элементы И соединены и подключены к вторым входам первого, третьего и четвертого управляющих элементов И, выходы первого и четвертого управляющих элементов И через первый элемент ИЛИ подключены к информационному входу первого разряда выходного регистра, выходы второго и третьего управляющих элементов И через второй элемент ИЛИ подключены к информационному входу второго разряда выходного регистра, прямые и инверсные выхо541163 Составитель А. ШкатуллаТехред А. Камышникова Редактор И. Грузова Корректор Л. Брахнина Заказ 2878/6 Изд. М 1896 Тираж 864 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, 5 К, Раушская иаб., д. 4,5Типография, пр. Сапунова, 2 ды которого подключены к первой группе вхо. дов девятого элемента И, выход которого соединен с управляющим входом генератора импульсов, а вторая группа входов подключена к прямым и;нверсным выходам входного регистра, установочные входы которого соединены с соответствующими входами выходного регистра, счетчика и управляющими входами с первого по восьмой элементов И и выходом бблока управления, информационные входы входного регистра подключены к входным шинам, а выходы счетчика и выходного регистра соединены соответственно с первой и второй группами выходных шин.Источники информации, принятые во вни- мание при экспертизе:1. Лвт. св.327474, кл. б 06 Р 5/02, 1971.2. Лвт. св.344436, кл. (д 06 Р 5/02, 1972.

СмотретьЗаявка

2008037, 26.03.1974

ИНСТИТУТ БИОЛОГИЧЕСКОЙ ФИЗИКИ АН СССР

АВРАМЕНКО АРКАДИЙ ЕФИМОВИЧ, АХАПКИН ЮРИЙ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоичных, кодов, параллельных

Опубликовано: 30.12.1976

Код ссылки

<a href="https://patents.su/3-541163-preobrazovatel-parallelnykh-dvoichnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь параллельных двоичных кодов</a>

Предыдущий патент: Устройство для обработки и ввода экспериментальный данных в вичислительную машину

Следующий патент: Устройство для спавнения чисел

Случайный патент: Модификатор для флотации фосфатных руд