Устройство для контроля программно-управляемого вычислительного блока

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1829034

Автор: Берников

Текст

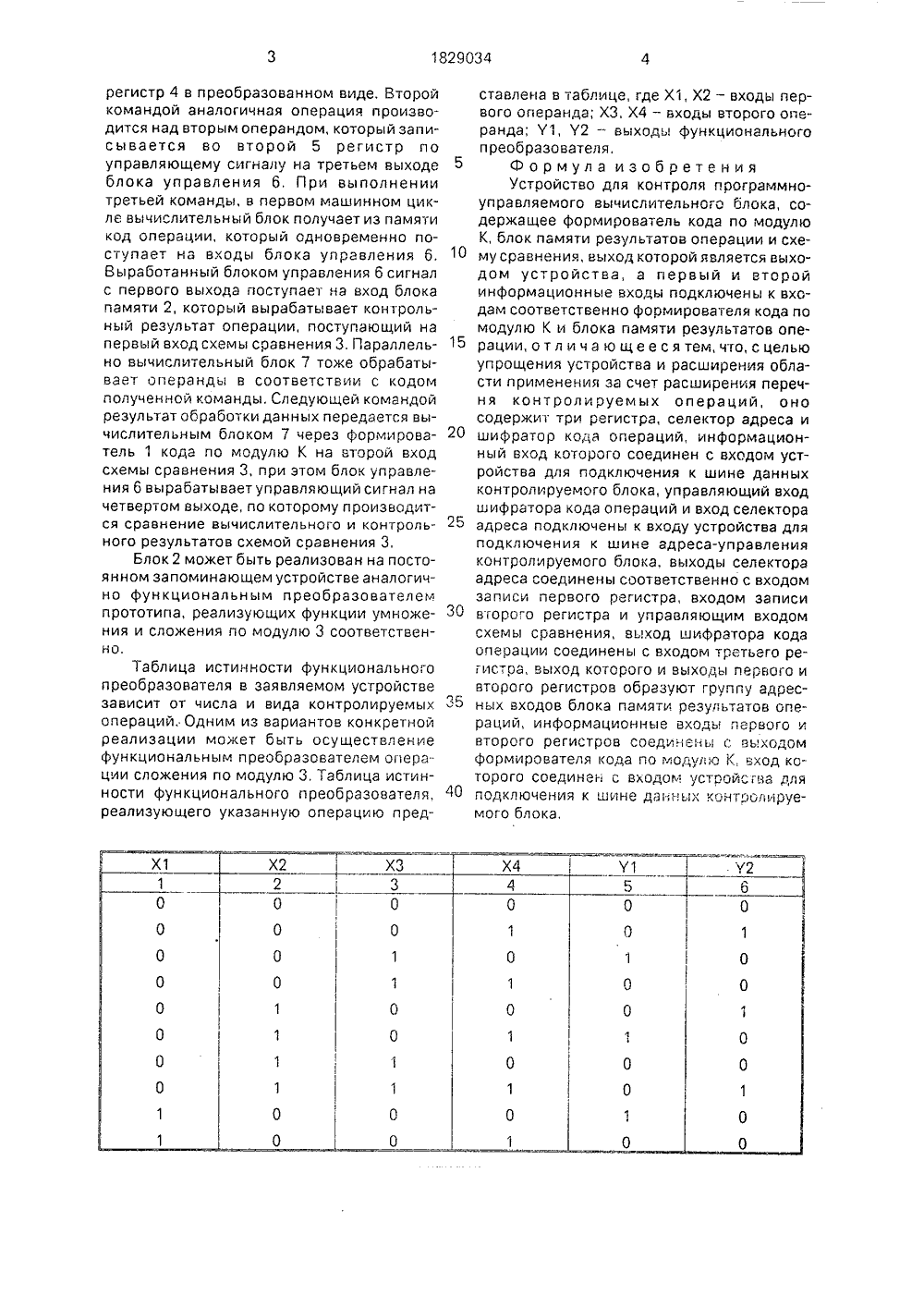

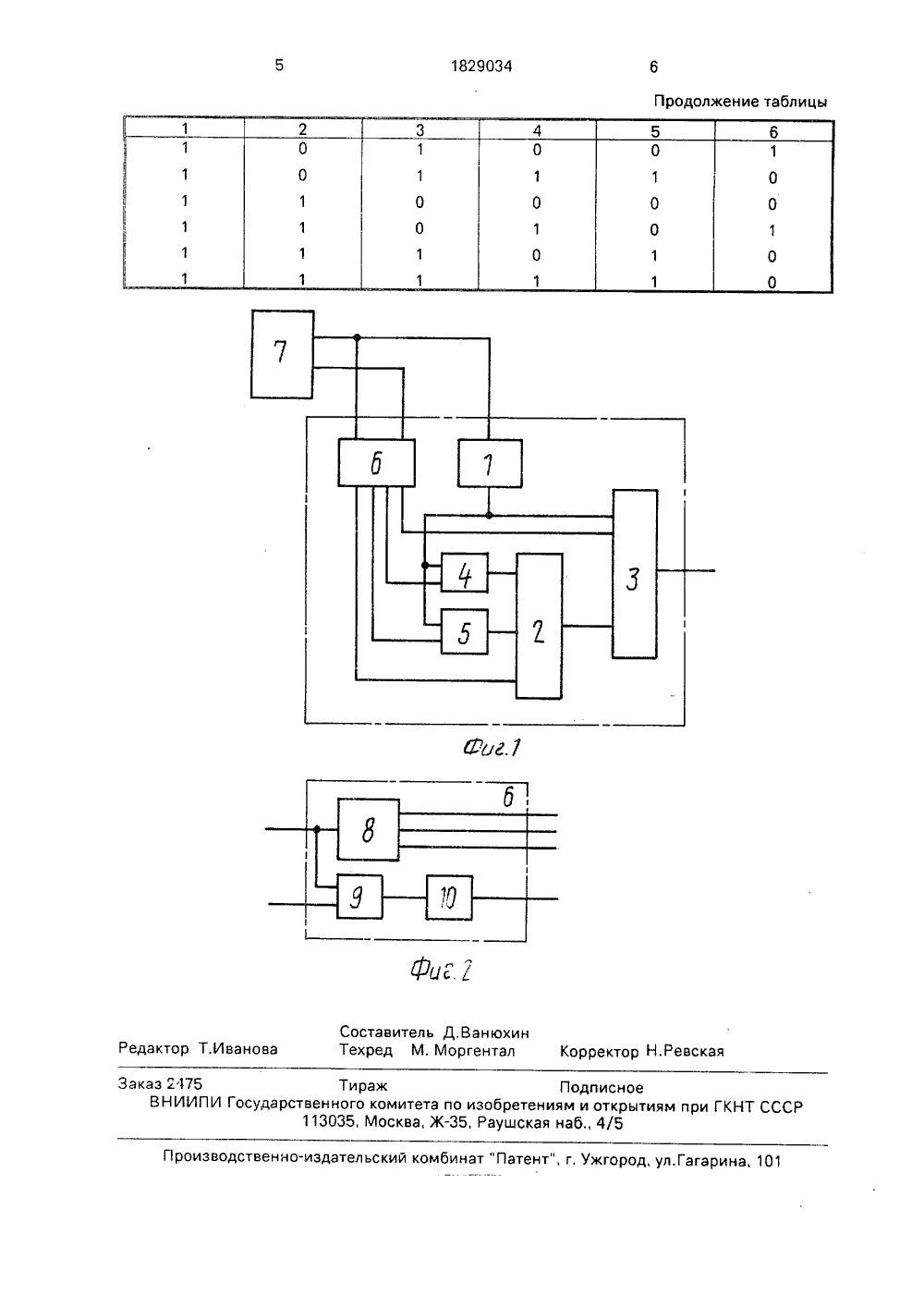

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9 О 34 А 1 51)5 6 06 Р 11/00 ИСАН АВТОРСКО неров а кад. ка неист, 1989,с.144. (54) УСТР ГРАММ Н ТЕЛЬНО (57) Изоб вычислит пользова ОЙСТВО ДЛЯ КОНТРО-УПРАВЛЯЕМОГО ВО БЛОКАретение относится к автельнсй технике и можес в системах обработки ЛЯ ПРО- ЧИСЛИатике и ыть ис- фровой ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(46) 23.07.93, Бюл, М 27971) Ленинградский институт ижелезнодорожного транспортаВ,Н,Образцова(56) Авторское свидетельство СССМ 1425674, кл. 0 Об Р 11/00, 1987Граф Ш,Гессель М, Схемы поиправностей. - М,: Энергоатомиз Изобретение относится к автоматике и вычислительной технике и может быть использовано е системах обработки цифровой информации повышенной надежности,Цель изобретения является упрощение устройства и расширение области его применения за счет расширения перечня контролируемых операций,На фиг, 1 представлена блок-схема устройства для контроля программно-управляемогс вычислительного блока; на фиг, 2 - пример реализации блока управления.Устройство для контроля программноуправляемого вычислительного блока содержит формирователь 1 кода по модулю К и блок памяти результатов операции 2, схему сравнения 3, первый 4 и второй 5 регистинформации повышеннои надежности. Цель изобретения - упрощение устройства и расширение области его применения за счет расширения перечня контролируемых операций. Устройство для контроля программно-управляемых вычислительных блоков содержит формирователь кода по модулю К и блок памяти результатов операции, схему сравнения, Первым в устройстве является введение первого и второго регистров и блока управления, причем выходы блока управления соединены с соответствующими входами регистров, блока памяти результатов операций и схемы сравнения, выход формирователя кода по модулю К соединен через регистры с входами блока памяти результатов операций и входом схемы сравнения, 2 ил., 1 табл. ры и блок управления 6 причем вход: блока ОО управления 6 и формирователя 1 кода по 3 модулю К являются входами устройства и ) подключены с соответствующим выходам контролируемого программно-управляемого вычислительного блока 7.Блок управления б (см, фиг, 2) содержит селектор адресов 8 шифратор када операции 9, реализованном на постоянном запоминающем устройстве, и регистр 10,швй Устройство работае следующим обраГ 1 ереой командой первый операции засылается в первый регистр 4, причем данные по сигналу на втором выходе блока управления 6, проходя через формирователь 1 кода пс модулю К, записываются врегистр 4 в преобразованном виде, Второй командой аналогичная операция производится над вторым операндом, который записывается во второй 5 регистр по управляющему сигналу на третьем выходе блока управления б, При выполнении третьей команды, в первом машинном цикле вычислительный блок получает из памяти код операции, который одновременно поступает на входы блока управления б. Выработанный блоком управления б сигнал с первого выхода поступает на вход блока памяти 2, который вырабатывает контрольный результат операции, поступающий на первый вход схемы сравнения 3. Параллельно вычислительный блок 7 тоже обрабатывает операнды в соответствии с кодом полученной команды. Следующей командой результат обработки данных передается вычислительным блоком 7 через формирователь 1 кода по модулю К на Второй вход схемь сравнения 3, при этом блок управления б вырабатывает управляющий сигнал на четвертом выходе, по которому производится сравнение вычислительного и контрольного результатов схемой сравнения 3,Елок 2 может быть реализован на постоянном запоминающем устройстве аналогично функциональным преобразователем прототипа, реализующих функции умножения и сложения по модулю 3 соответственно,Таблица истинности функционального преобразователя в заявляемом устройстве зависит от числа и вида контролируемых операций. Одним из вариантов конкретной реализации может быть осуществление функциональным преобразователем операции сложения по модулю 3, Таблица исгинности функционального преобразователя, реализующего указанную операцию представлена в таблице, где Х 1, Х 2 - входы первого операнда; ХЗ, Х 4 - входы второго операнда; У 1, У 2 - выходы функциональногопреобразователя,Формула изобретенияУстройство для контроля программноуправляемого вычислительного блока, содержащее формирователь кода по модулюК, блок памяти результатов операции и схему сравнения, Выход которой является выходом устройства, а первый и Второйинформационные входы подключены к входам соответственно формирователя кода помодулю К и блока памяти результатов опе 15 рации,отличающеесятем,что,сцельюупрощения устройства и расширения области применения за счет расширения перечня контролируемых операций, оносодержит три регистра, селектор адреса и20 шифратор кода операций, информационный вход которого соединен с входом устройства для подключения к шине данныхконтролируемого блока, управляющий входшифратора кода операций и вход селектора25 адреса подключены к входу устройства дляподключения к шине адреса-управленияконтролируемого блока, выходы селектораадреса соединены соответственно с входомзаписи первого регистра, входом записи30 второго регистра и управляющим входомсхемы сравнения, выход шифратора кодаоперации соединены с входом третьего регистоа, Выход которого и Выходы перВОго ивторого регистров образуют группу адрес 35 ных входов блока памяти результатов операций, информационные Входы первого ивторого регистров соединень, с Вь.ходомформирователя кода по модулю К., Вход которого соединен с входом устройсгва для40 подключения к шине данных контрогируемого блока,1829034 Продолжение таблицы Составитель Д.ВанюхинТехред М. Моргентал Корректор Н.Ревская Редактор Т.Иванова Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 Заказ 2175 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4863896, 03.09.1990

ЛЕНИНГРАДСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА ИМ. АКАД. В. Н. ОБРАЗЦОВА

БЕРНИКОВ ДМИТРИЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 11/00

Метки: блока, вычислительного, программно-управляемого

Опубликовано: 23.07.1993

Код ссылки

<a href="https://patents.su/3-1829034-ustrojjstvo-dlya-kontrolya-programmno-upravlyaemogo-vychislitelnogo-bloka.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля программно-управляемого вычислительного блока</a>

Предыдущий патент: Устройство приоритета

Следующий патент: Сигнатурно-синдромный анализатор

Случайный патент: Сталь