Сплайн-интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1686461

Авторы: Бедный, Денисюк, Картавая, Шелевицкий, Шутько

Текст

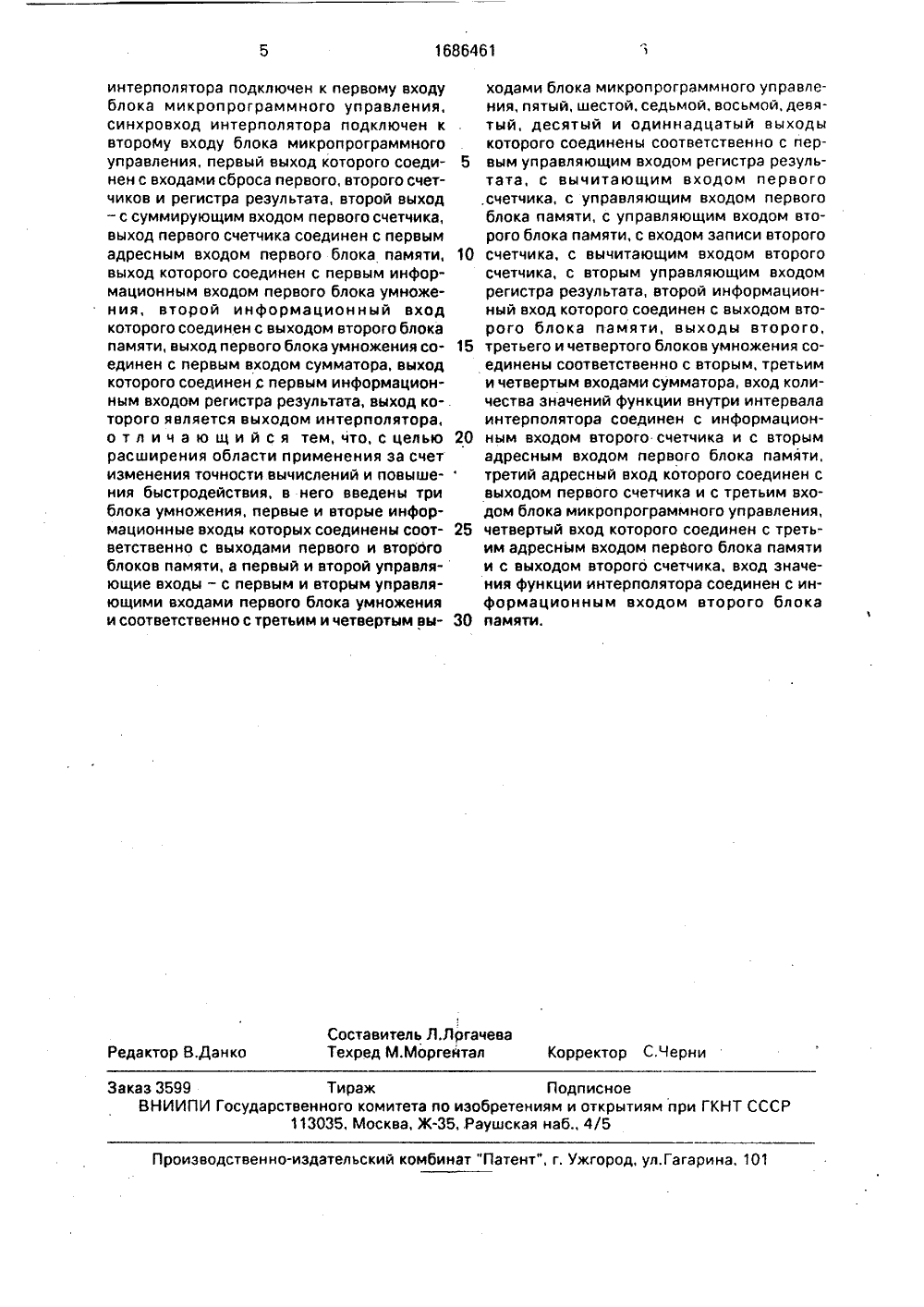

(Г 9 5)5 6 06 Г 15/353 НИЕ ИЗОБРЕТЕ ждансюк ГОСУДАРСТВЕННЫЙ КОМИГЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Киевский институт инженеров грской авиации им.60-летия СССР(56) Авторское свидетельство СССРМ 1465893, кл. б 06 Р 15/253, 1986.Авторское свидетельство СССРМ 1405074, кл, 6 06 Г 15/353, 1986,(54) СПЛАЙН-ИНТЕРПОЛЯТОР(57) Изобретение относится к автоматике ивычислительной технике, в частности к полиномиальным и сплайн-аппроксиматораМ, и может быть использовано в автоматических системах управления при воспроизведении широкого класса функциональных зависимостей. Целью изобретения является расширение области применения эа счет изменения точности вычислений и повышение быстродействия, Интерполятор используется для воспроизведения функциональных зависимостей на основе кусочно-полиномиальной сплайн-аппроксимации сплайнами третьей степени при равномерном разбиении на участки аппроксимации и может работать в реальном времени, Интерполятор содержит блок 1 микропрограммного управления, счетчики 2, 3, блоки 4, 5 памяти, блоки 6 - 9 умножения, сумматор 10 и регистр 11 результата, 1 ил.Изобретение относится к автоматике ивычислительной технике, в частности к полиномиальным и сплайн-аппроксиматорам,и может быть использовано в автоматических системах управления при воспгпиэведении широкого класса функциональныхзависимостей.Цель изобретения - расширение области применения за счет изменения точностивычислений и повышение быстродействия.На чертеже приведена структурная схема интерполятора.Интерполятор содержит блок 1 микропрограммного управления, счетчики 2 и 3,блоки 4 и 5 памяти, блоки 6 - 9 умножения,сумматор 10, регистр 11 результата.Принцип действия интерполятора основан на кусочно-полиномиальной сплайн-аппроксимации сплайнамистепени приравномерном разбиении на участки аппроксимации.Вычисления производятся по формуле2 3 451 х +1 х Х х,+Х х;т 1 21",1 т и а 3 1 а 1где 1 значение интерполируемой функциив узловых точках;х - коэффициент, зависящий от текущего значения абсциссы;1 1х = - (1- ьх,Ьх;, ( ): Я,) )х; =(1-дх;)ф(1-дхД дх;1-дХ;)дх(.К,й);ХидХ;фдХ;1-дХ;(1-ЬХД дХ;,)=2,1)х дХ., (1-дХД, ма,и-).На первом участке интерполяции= 2): 4гдех= 1-дх;)11-дх,Ьх.,гх;2 = дх,д Х (1- дх; ),х 2 =- г) дх; 1,1- ьх;,СНа последнем участке интерполяции= Й), "х = О,Ьй = тп.2 хМ+Ь 1 хПЧ+ Ъ хщ, (3)1 2 3гдеХ,= - (1-дх;) дх;2 х; : (1-дХ,")+ (1-ЬХ,д х;Ъх,-дх, 1 дх, дХ Коэффициен 1 ы хц хранятся в блоке 4 памяти, выг 1 олненном на ПЗУ. Значения функции 1 в узловых точках последовательно поступают на вход блока 5 памяти, собранного на сдвиговых регистрах. С выходов блока 5 на входы блоков 6-9 параллельно поступают четыре значения функции 11-2т 1-1 т 2 т 1+15 Одновременно на другие входы блоковумножения поступают из блока 4 соответст 1 2 3 4ВУЮЩИЕ ЗНаЧЕНИЯ Хг,1-2; Х,1-1; ХЦ; ХЦ+1., Сформированные произведения поступают на входы сумматора 10, на выходе которого 10 получаем значения сплайна 51, Регистр 11служит для фиксации этих значений, причем с целью сохранения информации о значении функции 1 в последней узловой точке, значение 1 = Ь = Бми переписывается не посредственно из блока 5 в регистр 11 поокончании процесса вычислений.Работа интерполятора начинается припоявлении на входе "Пуск" блока 1 уровня логической единицы.20 Блок 1 вырабатывает сигнал, обнуляющий счетчик 2, счетчик 3, блок 5 и регистр 11. Одновременно с записью т 1 в блок 5 в счетчик 3 заносится код М, который определяет количество вычисляемых значений 25 функции внутри интерполируемого интервала и формирует младшие разряды адреса .блока 4. Содержимое счетчика 3 уменьшается на 1 после каждого вычислительного значения функции. При значении его, равном О, 30 интерполяция на данном участке заканчивается, Код М записывается в счетчик 3 перед каждым новым участком интерполирования одновременно с записью следующего значения 1, Код М также, поступает в блок 4 и 35 является средней частью адресного слова.Счетчик 2 формирует старшие разряды адреса блока 4 и определяет момент начала процесса интерполирования, подсчитывая в начале работы количество принятых эначе ний 11, поступающих на вход блока 5, В ычисления начинаются после принятия третьего значения 11, В этот момент времени содержимое счетчика 2 равно 2, При этом условии значение Ь вычисляется по формуле (2).45 После нахождения значений функцияна первом участке интерполяции содержимое счетчика 2 уменьшается на 1. При значении 1 счетчика 2 вычисления производятся по формуле (1). Следующий 50 управляющий сигнал появляется после исчезновения сигнала "Пуск". Содержимое счетчика 2 становится равным О, и на последнем участке интерполирования вычисления производятся по формуле (3).55 Формула изобретен ияСплайн-интерполятор, содержащийпервый и второй счетчики, первый и второй блоки памяти, первый блок умножения, сумматор, регистр результата, блок микропрограммного управления, причем вход пуска1686461 Составитель Л.ЛргачеваТехред М.Моргентал Корректор С.4 ерни Редактор В.Данко Заказ 3599 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж,.Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина. 101 интерполятора подключен к первому входу блока микропрограммного управления, синхровход интерполятора подключен к второМу входу блока микропрограммного управления, первый выход которого соединен с входами сброса первого, второго счетчиков и регистра результата, второй выход - с суммирующим входом первого счетчика, выход первого счетчика соединен с первым адресным входом первого блока памяти, выход которого соединен с первым информационным входом первого блока умножения, второй информационный вход которого соединен с выходом второго блока памяти, выход первого блока умножения соединен с первым входом сумматора, выход которого соединен с первым информационным входом регистра результата, выход которого является выходом интерполятора, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения за счет изменения точности вычислений и повышения быстродействия, в него введены три блока умножения, первые и вторые информационные входы которых соединены соответственно с выходами первого и второго блоков памяти, а первый и второй управляющие входы - с первым и вторым управляющими входами первого блока умножения и соответственно с третьим и четвертым выходами блока микропрограммного управления, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый выходы которого соединены соответственно с пер вым управляющим входом регистра результата, с вычитающим входом первого ,счетчика, с управляющим входом первого блока памяти, с управляющим входом второго блока памяти, с входом записи второго 10 счетчика, с вычитающим входом второгосчетчика, с вторым управляющим входом регистра результата, второй информационный вход которого соединен с выходом второго блока памяти, выходы второго, 15 третьего и четвертого блоков умножения соединены соответственно с вторым, третьим и четвертым входами сумматора, вход количества значений функции внутри интервала интерполятора соединен с информацион ным входом второго счетчика и с вторымадресным входом первого блока памяти, третий адресный вход которого соединен с выходом первого счетчика и с третьим входом блока микропрограммного управления, 25 четвертый вход которого соединен с третьим адресным входом первого блока памяти и с выходом второго счетчика, вход значения функции интерполятора соединен с информационным входом второго блока 30 памяти.

СмотретьЗаявка

4688490, 13.02.1989

КИЕВСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ ИМ. 60-ЛЕТИЯ СССР

ШУТКО НИКОЛАЙ АЛЕКСАНДРОВИЧ, ШЕЛЕВИЦКИЙ ИГОРЬ ВЛАДИМИРОВИЧ, БЕДНЫЙ НИКОЛАЙ СЕМЕНОВИЧ, КАРТАВАЯ ТАТЬЯНА ГЕННАДИЕВНА, ДЕНИСЮК ВЛАДИМИР ПЕТРОВИЧ

МПК / Метки

МПК: G06F 17/17

Метки: сплайн-интерполятор

Опубликовано: 23.10.1991

Код ссылки

<a href="https://patents.su/3-1686461-splajjn-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Сплайн-интерполятор</a>

Предыдущий патент: Устройство для вычисления импликант

Следующий патент: Устройство для синтаксического контроля

Случайный патент: Устройство для определения веса партии сортового проката в потоке