Генератор тестов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

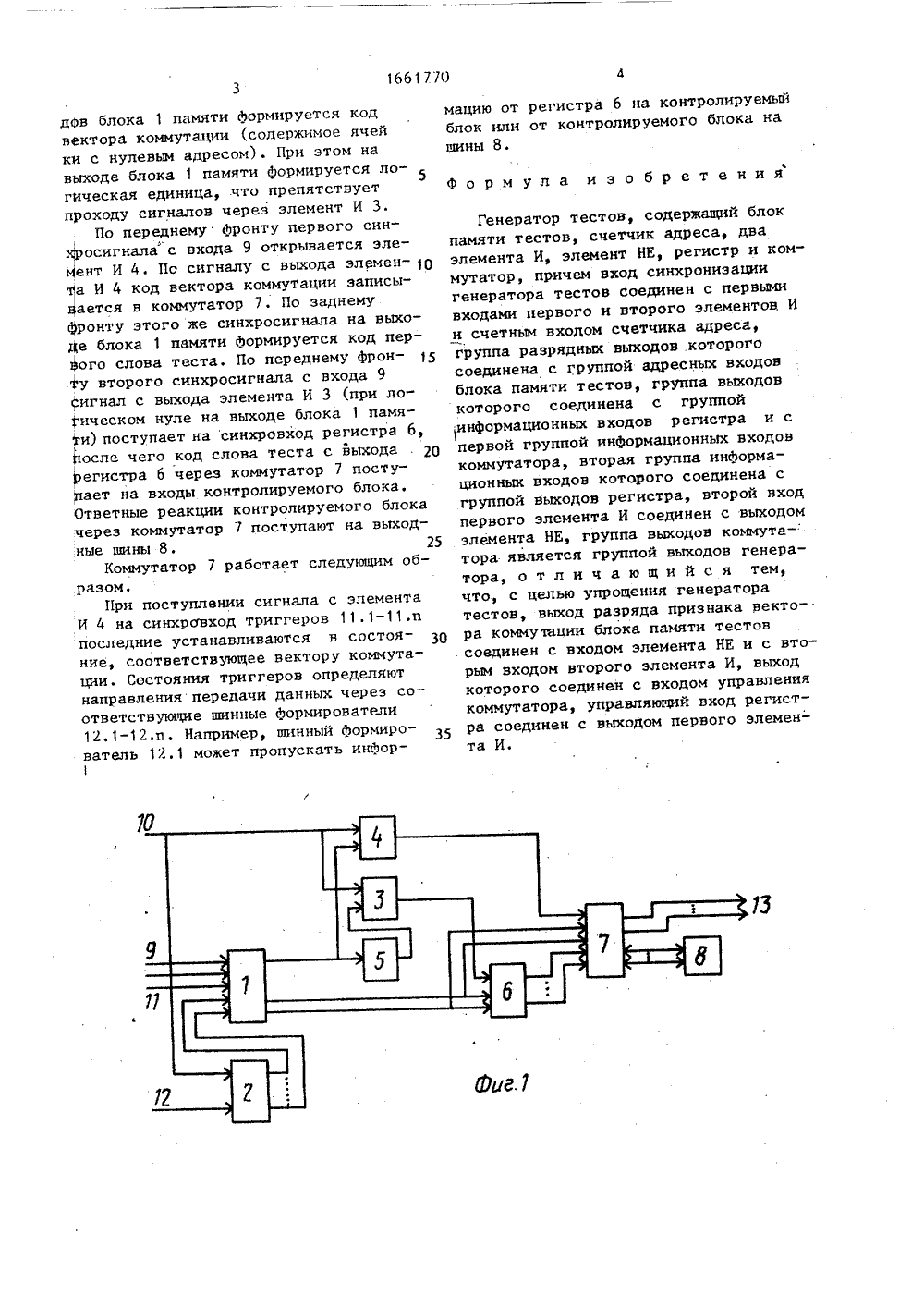

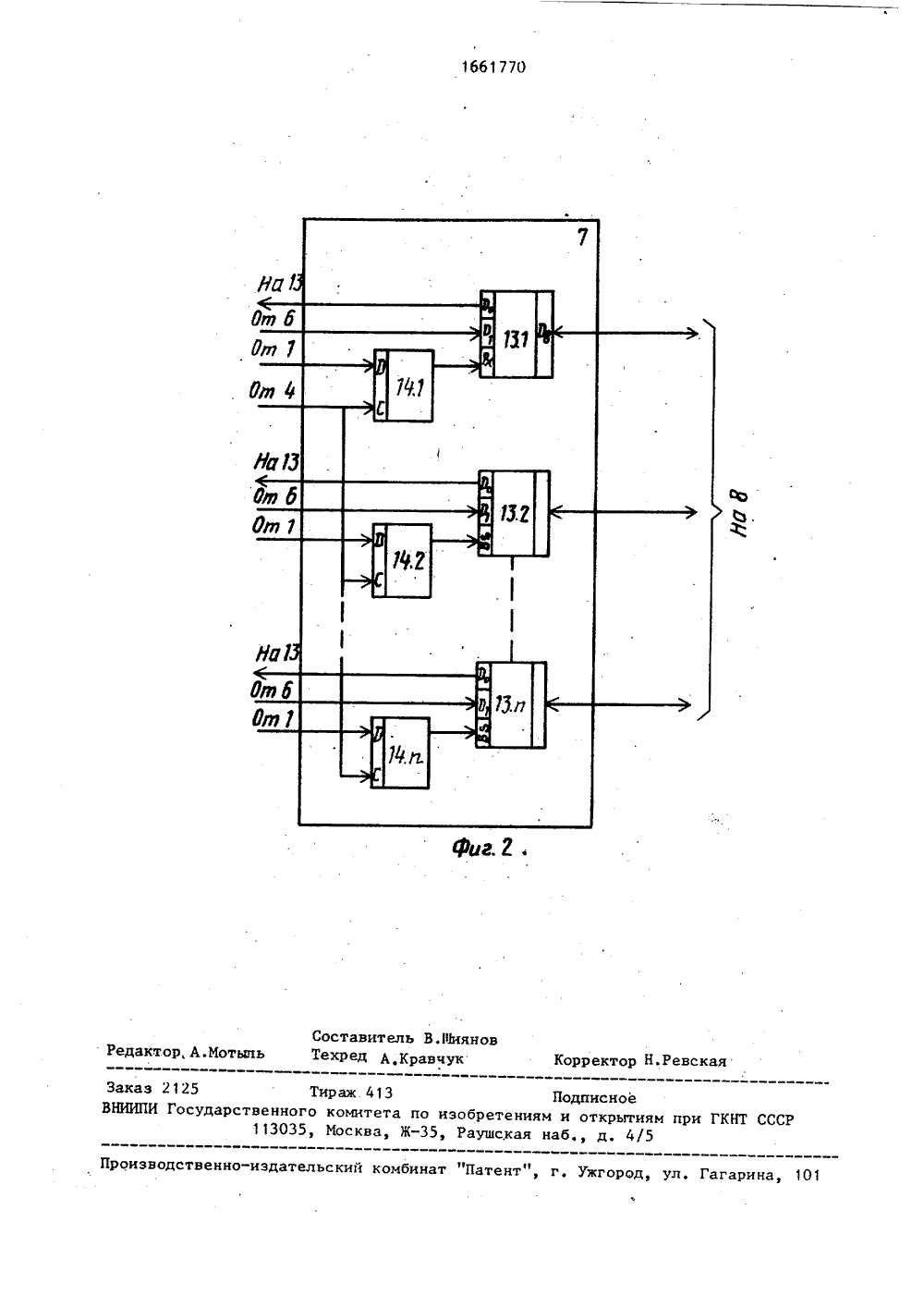

(51)5 С 06 Р 11/26 ЕТЕНИЯ ПИСА ЕЛЬСТ УС Н АВТО м обе состояруппе выхоОСУДАРСТВЕННЫЙ НОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМРИ ГКНТ СССР(71) Научно-исследовательский и конструкторско-технологический институт средств контроля электронной аппаратуры и изделий электронной техники "Контрольприбор"(56) Авторское свидетельство СССР У 836389, кл. С 06 Р 11/26, 1979.Авторское свидетельство СССР Р 1405060, кл . С 06 Р 11/26, 1986. Изобретение относится к вычислительной технике и может быть использовано при тестировании цировой аппаратуры,Цель иэо бретения - упрощение гене ратора.На фиг. 1 показана структурная схема .генератора тестов; на Фиг. 2 структурная схема коммутатора.Генератор содержит блок 1 памяти, тестов, счетчик 2 адреса, два элемента И 3 и 4, элемент НЕ 5, регистр 6, коммутатор 7, выходные нины 8, вход 9 синхронизации, вход 10 сброса счетчика 2 . Коммутатор (3 иг . 2) содержит и триггеров 11.1-11.и и и шинных формирователей 12.1-12.и.Генератор работает следующи разом.Контролируемый блок имеет и выводов, каждый из которых может быть входным и выходным. Управление выводами осуществляется с помощью вектора(57) Изобретение относится к вычислительной технике и может быть исполь-.зовано при тестировании цифровой аппаратуры. Цель изобретения - упроще -ние генератора. Генератор содержитблок памяти тестов, счетчик адреса,два элемента И, элемент НЕ, регистри коммутатор. Генератор обеспечиваетпростоту Формирования тестов для контролируемых объектов с двунаправленными выводами . 2 ил . оммутации, записанного наряду с тесовыми словами в блок 1 памяти тесов. Последовательность слов, считыемых из блока 1 памяти тестов, всегда начинается с вектора коммутации, а который устанавливает входы и выходы коммутатора 7, затем считываются тестовые слова. При необходимости изменения назначения выводов коммутатора 7 из блока 1 памяти тестов считывается новый вектор коммутации, а затем тестовые слова. В исходное нуле-.вое состояние счетчик 2 адреса устанавливается сигналом, поступающимна вход 10 сброса. Считывание иэблока 1 памяти тестов производится ф, в соответствии с изменением состояния счетчика 2 адреса, переключение которого происходит по заднему фронту сигнала, поступающего по входу 9 синхронизации.При установке в исходноние счетчикаадреса на гдОв блока 1 памяти формируется код вектора коммутации (содержимое ячей кн с нулевым адресом). При этом на выходе блока 1 памяти формируется ло 5 гнческая единица, что препятствует проходу сигналов через элемент И 3.По переднему фронту первого синхросигнала" с входа 9 открывается элеь 1 ент И 4. По сигналу с выхода элемен О та И 4 код вектора коммутации записывается в коммутатор 7, По заднему фронту этого же синхросигнала на выхоДе блока 1 памяти формируется код первого слова теста. По переднему фронту второго синхросигнала с входа 9 Сигнал с выхода элемента И 3 (при логическом нуле на выходе блока 1 памяТи) поступает на синхровход регистра 6, После чего код слова теста с выхода . 2 О регистра 6 через коммутатор 7 поступает на входы контролируемого блока. Ответные реакции контролируемого блока через коммутатор 7 поступают на выходные шины 8, 25Коммутатор 7 работает следующим образом.При поступлении сигнала с элемента И 4 на синхрсвход триггеров 11.1-11.п последние устанавливаются в состоя О ние, соответствующее вектору коммутации. Состояния триггеров определяют направления передачи данных через соответствующие шинные формирователи 12.1-12.п. Например, шинный формирователь 12.1 может пропускать инфор мацию от регистра 6 на контролируемыйблок или от контролируемого блока нашины 8.Формула из о брет енияГенератор тестов, содержащий блок памяти тестов, счетчик адреса, два элемента И, элемент НЕ, регистр и коммутатор, причем вход синхронизации генератора тестов соединен с первыми входами первого и второго элементов, И и счетным входом счетчика адреса, группа разрядных выходов которого соединена с группой адресных входов блока памяти тестов, группа вьмодов которого соединена с группой информационных входов регистра и с первой группой информационных входов коммутатора, вторая группа информационньм входов которого соединена с группой выходов регистра, второй вход первого элемента И соединен с выходом элемента НЕ, группа выходов коммута- тора является группой выходов генератора, отличающийся тем, что, с целью упрощения генератора тестов, вьмод разряда признака вектора коммутации блока памяти тестов . соединен с входом элемента НЕ и с вторьм входом второго элемента И, выход которого соединен с входом управления коммутатора, управляющий вход регистра соединен с выходом первого элемен- та И.1661770 Фиг. 2 Составитель В.1 Ыян Техред А,Кравчук актор, А.Мотып вс орректор твенно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 о Заказ 2125 ВНИИПИ Госуд Тираж 413 твенного комитета по 113035, Москва, Ж

СмотретьЗаявка

4684340, 27.04.1989

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ И КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ СРЕДСТВ КОНТРОЛЯ ЭЛЕКТРОННОЙ АППАРАТУРЫ И ИЗДЕЛИЙ ЭЛЕКТРОННОЙ ТЕХНИКИ

ЛЕБЕДЬ ЛЕВ ЛЬВОВИЧ, ОСОБОВ МИХАИЛ ИЗРАИЛЕВИЧ

МПК / Метки

МПК: G06F 11/26

Опубликовано: 07.07.1991

Код ссылки

<a href="https://patents.su/3-1661770-generator-testov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор тестов</a>

Предыдущий патент: Формирователь тестов

Следующий патент: Устройство для отладки программ

Случайный патент: Способ усиления серебряных фотографических изображений на бумажной основе