Устройство для вычисления функции z=

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

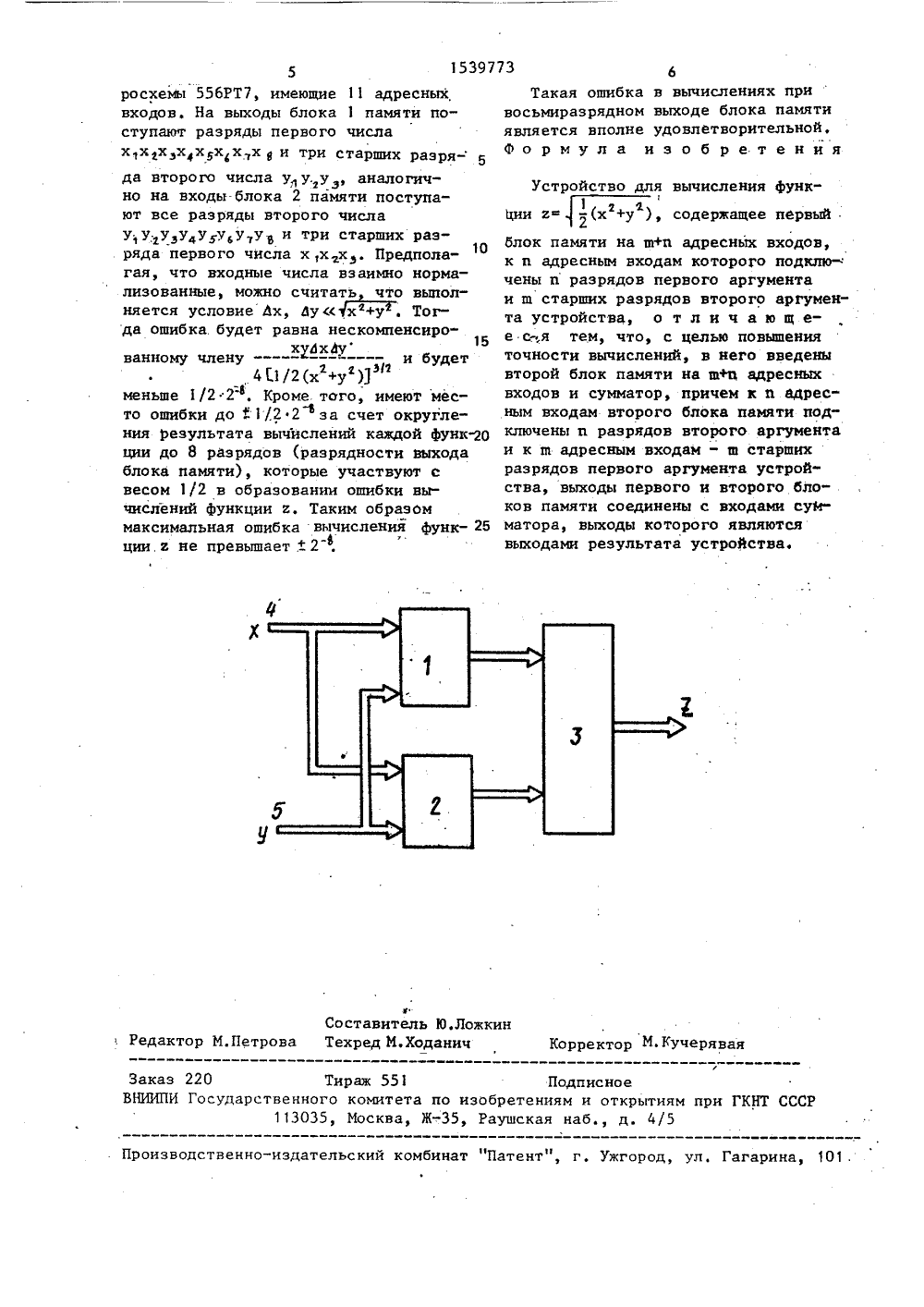

(5)5 С 0 552 НИЯ М 4 Аксельрод идетельство СССР 06 Р 7/552, 198 ие небольших ПЗУ Электроника, 19 ВЫЧИСЛЕ ФУНКсум для дов вто о аргумента 5 и щ первого числа 4. в блока 1 памяти зрядов выход мяти п 3, с в тарши Числа блока 2 п сумматора оды даются мает выхо ода переноса старшин разр Устройств ч разом. На входы числа х и у аким азо ного ч ыи блокчисление оОСУДАРСТ 8 ЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМРИ П(НТ СССР ИСАНИЕ ИЗОБР К АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение относится к цифровой вычислительной технике и можетбыть использовано в быстродействующих Изобретение относится к цифровоивычислительной технике и может бытиспользовано в быстродействующихпроцессорах и специализированных вычислителЬных устройствах, работающих в реальном масштабе времени свысокой тактирующей частотой.Цель изобретения - повьппение тоности вычислений.На чертеже приведена блок-схема устройства,Блок-схема содержит первый 1 ивторой 2 блоки памяти, сумматор 3входы 4 и 5 аргументов устройства.К входам первого .блока 1 памятиподключены все и разрядов первогоаргумента 4 и щ старших разрядов врого аргумента 5 (щ (и). К входамрого блока 2 памяти подключены все 2процессорах и специализированных вычислительных устройствах, работающих в реальном масштабе времени с высокой тактирующей частотой. Цель изобретения. - повьппение точности вычислений. Устройство содержит блок памяти на щ+и адресных входов, к и адресным входам которого подключены и разрядов первого числа х и щ старших разрядов второго числа у, дополнительный блок памяти на п 1+и адресных входов и сумматор, к и адресным входам второго блока памяти подключены щ старших разрядов первого числа х, выходы первого и второго блоков памяти соединены с входами ра, выходы которого служ а выходного числа. 1 ил. ходов которого сниисло, причем с вымматора снимается ыходного числа.ботает следующим обустроиства поступаютвзаимно нормализованныем, что старший разрядел равен единице. Пермяти осуществляет выции г согласно формул4 -(х+ Аналоги мяти осуще цин соглас , 1/2(х +у )эа 2 па- функ 10 о на втором блок х) +(у+Ьу эг4 - (х-Дх) +(12 ол на 1 и 2 памяти зиаковым образом.сумматора 3 опвыражению Е азультат яет чи фунпозволяют Отсюда блок ду необхоинформаятся в-(х +у )2 22 2 -(х+у )12Ьт бки,величину ош 55 дныхе разрядо и в ка в+ тся ми использ твляется вычисленио формуле Отметим, что блок программированы о Результат на выхо ределяется соглас 2 хх "(Е +Е )2ФПолагая, дх, дусс х +уг и учитыв1 д 11 дг разложение а + Ь"-а+ -- . . 2 (2(, 8 аэ иметь (члены, содержащие Ьх и Ьу степени вьппе второй ввиду их мал опущены):+ Ш,М. Е, Ф у ) 41/2(х Фу) где / () - иском а член вида дхдХ4 1/2 (хг+у 2)Р нескомпенсированной ошибкВы сление каждой из в ных кций е и е" - бол операция, чем вычисление при условии, что входные имеют меньшую суммарную р Это достигается в предлаг ройстве при выборе х-Дх р х, округленному до ш разр чем округление производит ввода первых разрядов чис 2 памяти, где вычисляется присвоения значения 1 (ш+ х.-дх (считая х и у правил ми), откуда ой.спомогательее простая функций е, переменные азрядность. аемом уставным числу ядов, прися послела х в блок е путем 1) разряду ьными дробядх=О,ООх .х , .хАналогичные преобразованияполучить значения у-ду и Ьследует, что для введенияпамяти пары чисел х+дх и удимо ввести (ш+и)-разряднуюцию, числа х-дх и у+Ьу ввоблок 2 памяти.В то же время програмблоков 1 и 2 памяти произиаковым образомОценивая на примереимеем следующее.Пусть количествои выходных чисел п=8блоков 1 и 2 памяти15397736Такая ошибка в вычислениях привосьмиразрядном выходе блока памятиявляется вполне удовлетворительной.Формула изобретения Корректор М.Кучеряв Заказ 220 Тираж 551 П ВНИИПИ Государственного комитета по изобретени113035, Москва, Ж, Раушская писно и отк ням при ГКНТ СССР/5 а Производственно-издательский комбинат "Патент", г, Ужгород, у 101 агари 5росхемы 556 РТ 7, имеющие 11 адресных входов. На выходы блока 1 памяти поступают разряды первого числа ххгххх 5 ххх у и три старших раэря да второго числа у у.,у , аналогично на входы. блока 2 памяти поступают все разряды второго числа у угууду 5 ууу и три старших Раз ряда первого числа х,ххз. Предпола 10 гая, что входные числа взаимно нормализованные, можно считать что выполняется условие Лх, Ду(с х+у . Тогда ошибка будет равна нескомпенсирохудхЬуванному члену -- -" ---- и будет40/2(х +у )3 меньше 1/2:2 , Кроме того, имеют место ошибки до + 1/22 за счет округления Результата вычислений каждой функции до 8 разрядов (разрядности выхода блока памяти), которые участвуют с весом 1/2 в образовании ошибки вычислений функции к, Таким образом максимальная ошибка вычисления функ7 ции в не превышает .+ 2 ,Составитель Ю.ЛожРедактор МПетрова Техред М.Ходанич Устройство для вычисления функ 1 г гсии з -(х +у ), содержащее первый блок памяти на ш+и адресных входов, к и адресным входам которого подклю- чены и разрядов первого аргумента и ш старших разрядов второго аргумента устройства, о т л и ч а ю щ ее с,я тем, что, с целью повышения точности вычислений, в него введены второй блок памяти на а+и адресных входов и сумматор, причем к и адресным входам второго блока памяти подключены и разрядов второго аргумента и к ш адресным входам - ш старших разрядов первого аргумента устройства, выходы первого и второго блоков памяти соединены с входами сум" матора, выходы которого являются выходами результата устройства.

СмотретьЗаявка

4432908, 08.04.1988

ПРЕДПРИЯТИЕ ПЯ Р-6577

ЛОЖКИН ЮРИЙ НИКОЛАЕВИЧ, АКСЕЛЬРОД ГЛЕБ ЗАЛМАНОВИЧ, ЯХОНТОВ РАФАЭЛЬ ДАВЫДОВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, функции

Опубликовано: 30.01.1990

Код ссылки

<a href="https://patents.su/3-1539773-ustrojjstvo-dlya-vychisleniya-funkcii-z.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции z=</a>

Предыдущий патент: Вычислительное устройство

Следующий патент: Генератор псевдослучайной последовательности

Случайный патент: Привод вращения для нарезки резисторов