Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1517136

Авторы: Герасичкин, Домнин, Пузеев

Текст

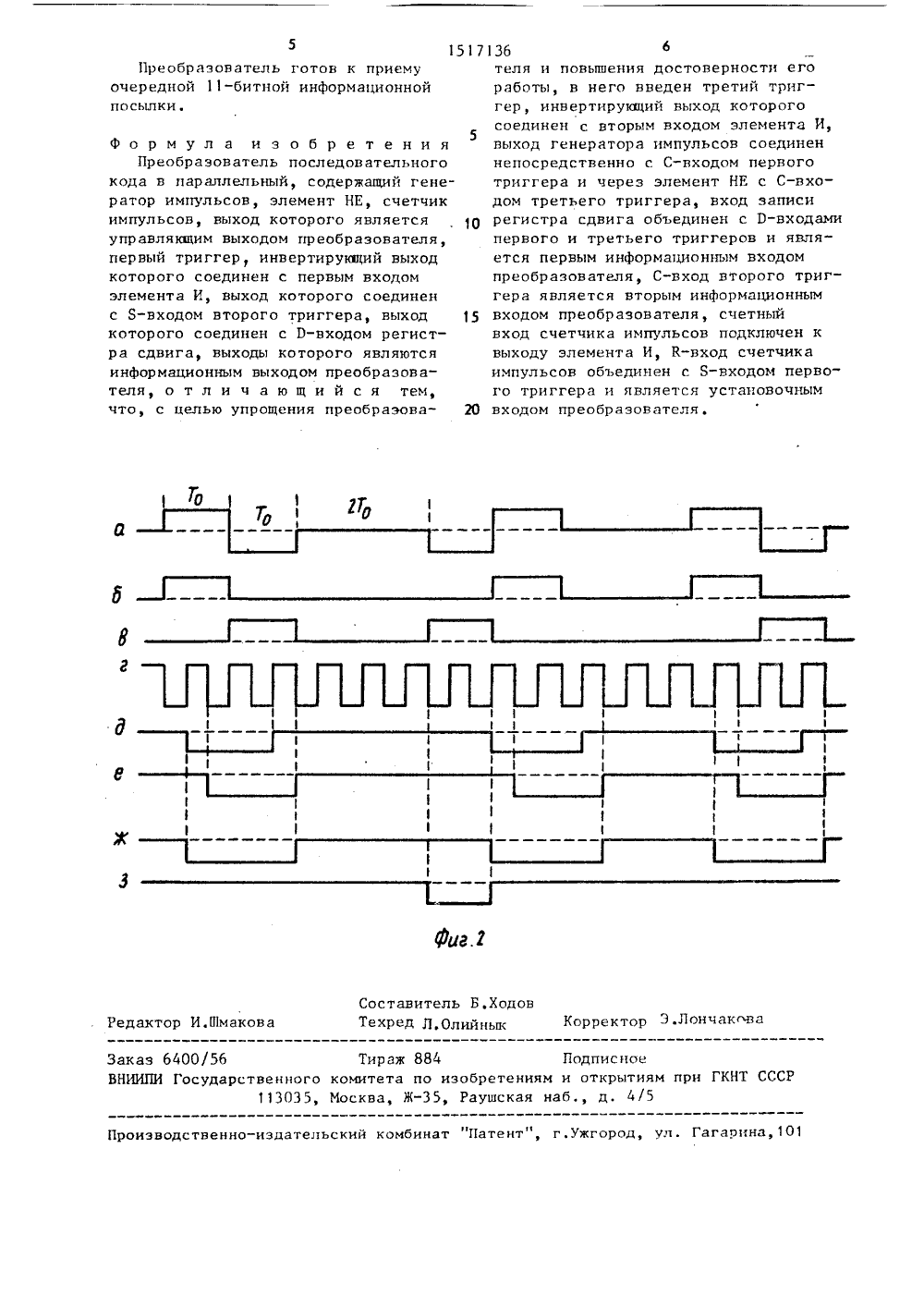

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) Я 136 7 0 504 Н СУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМИ ГКНТ СССР изоБектЕНИ и ИДЕТЕЛЬСТВУ 2ойствах сопряжения ЭВМ с ными каналами связи. Изобзволяет упростить конструк азователя и, кроме того, искажение информации на лей в устр двухпровод ретение по цию преобр устранить его выходе та сигнала вателя отн 39В,М.До ельство СССР 7/00, 1982. ьство СССР 7/00, 1983. го перво достоверности работы преобПреобразователь последокода в параллельный содертор 1 импульсов, элемент чик 3 импульсов, три триггеэлемент И 5 и регистр 7(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится к вычислительной технике и может быть использовано при построении преобраэоватегенера счет(56) Авторское свидеУ 924696, кл. Н 03 МАвторское свидетелУ 1159164, кл. Н 03 вызванное задержкой фрон на втором входе преобразо сительно спада сигнала на входе, чем обеспечиваетсяИзобретение относится к вычисли"тельной технике и может быть использовано при построении преобразователей в устройствах сопряжения ЭВМ сдвухпроводными каналами связи,Целью изобретения является упрощение преобразователя и повышение достоверности его работы.Па фиг.1 представлена блок-схемапреобразователя; на Фиг,2 - временные диаграммы, поясняющие работу преобразователя,Преобразователь последовательногокода в параллельный содержит генератор 1. импульсов, элемент НЕ 2, счетчик 3 импульсов, первый триггер 4,элемент И 5, второй триггер 6, регистр 7 сдвига, третий триггер 8 иимеет первый 9 и второй 10 информационнь е и установочные 11 входы, атакже информационный 12 и управляющий 13 выходы.На Фиг.2 обозначены: а - сигнал,поступающий на преобразователь с двух 25проводного канала связи; б - сигнална входе 9; в " сигнал на входе 10;г - сигнал на выходе генератора 1; д -сигнал па выходе триггера 4; е - сигнал па выходе триггера 8; ж - сигнална выходе элемента И 5; з - сигнал навыходе триггера б.Преобразователь последовательногокода в параллельный работает следук.щим образом.Информационный бит передается за35время, равное 4 Т и кодируется следующим образом: "1" как последовательность,(+Б, -П, О), "0" как последовательность (-П +У,О) . Информация следу 40ет последовательно бит за битом поодиннадцать бит в каждой информационной посылке, 11-битные информацион"ные посылки разделяют время не менее 8 Т,. 45При включении питания преобразователь устанавливается в исходное состояние, которое определяется обнулением 11-разрядного счетчика 3 и установкой триггера 6 в "1" черезтриггер 4 и элемент И 5 сигналом повходу 11, На информационных входах 9и 10 сигналы отсутствуют.Если первым появляется информационный сигнал на входе 9, то он записывает исходное единичное состояниетриггера б в регистр 7, а также поступает на П в выхо триггеров 4 и 8,которые по синхросигналам от генератора 1, формирующего сигнала типа меандр с периодом следования импульсов не более 2/3 Тс, устанавливаются в единичное состояние, Так как выходы триггеров 4 и 8 соединены с Б-входом триггера 6 через элемент И 5,то срабатывание хотя бы одного из триггеров 8 и 4 обеспечивает сохранение исходного единичного состояния триггера 6.Появившийся на втором информационном входе 10 сигнал вслед за сигналом на первом входе 9 не может вывести триггер 6 из исходного единичного состояния, так как на приоритетный вход (Я-вход) триггера 6 воздействует сигнал с выхода элемента И 5.Если первым появляется сигнал на втором входе 10, то он устанавливает триггер 6 в нулевое состояние. Сигнал, появившийся на первом входе 9, записывает нуль с выхода триггера 6 в регистр 7, а затем этим же сигналом через триггеры 4 и 8 и элемент И 5 триггер 6 устанавливается в исходное единичное состояние. С выхода элемента И 5 сигнал в это время поступает на счетный вход 11-разрядного счетчика 3, состояние которого увеличивается на единицу.Задержка срабатывания триггеров 4 и 8 и элемента И 5 не приводит к опрокидыванию триггера 6 .из нулевого состояния в единичное сигналом, появившимся на первом входе 9, прежде, Чем этим сигналом нулевое состояние триггера 6 не будет записано в регистр 7.Прием информационного бита завершается отсутствием сигналов на первом 9 и втором 10 входах устройства в течение времени не менее 2 Т . За это время триггеры 4 и 8 установятся в исходное состояние и через элемент И 5 разрешат работу триггера 6, сохраняя на его выходе "1". Если сигнал вновь появляется на первом входе 9, процедура обработки и записи информации в регистр 7 повторяется.1При состоянии счетчика 3, равномодиннадцати, на его выходе появляется сигнал, означающий, что в сдвиговый регистр 7 поступило 11 информационных бит, а сам счетчик 3 обнуляется.1517 Преобразователь готов к приемуочередной 11-битной информационнойпосылки11 1 1Составитель Б,ХодовТехред Л,Олийнык Редактор И,П 1 макова Корректор Э,Лончакпва Заказ 6400/56 Тираж 884 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 Производственно в издательск комбинат "Патент", г.ужгород, ул. Гагарина,101 5 формула изобретенияПреобразователь последовательного кода в параллельный, содержащий генератор импульсов, элемент НЕ, счетчик импульсов, выход которого является 10 управляющим выходом преобразователя, первый триггер, инвертирующий выход которого соединен с первым входом элемента И, выход которого соединен с Я-входом второго триггера, выход 15 которого соединен с Р-входом регистра сдвига, выходы которого являются информационным выходом преобразователя, о т л и ч а ю щ и й с я тем, что, с целью упрощения преобраэова 136 6теля и повышения достоверности егоработы, в него введен третий триггер, инвертирукций выход которогосоецинен с вторым входом элемента И,выход генератора импульсов соединеннепосредственно с С-входом первоготриггера и через элемент НЕ с С-входом третьего триггера, вход записирегистра сдвига объединен с Р-входамипервого и третьего триггеров и является первым информационным входомпреобразователя, С-вход второго триггера является вторым информационнымвходом преобразователя, счетныйвход счетчика импульсов подключен квыходу элемента И, К-вход счетчикаимпульсов объединен с Б-входом первого триггера и является установочнымвходом преобразователя,

СмотретьЗаявка

4399377, 28.03.1988

ПРЕДПРИЯТИЕ ПЯ В-2655

ГЕРАСИЧКИН ВЛАДИМИР ДМИТРИЕВИЧ, ДОМНИН ВАЛЕНТИН МИХАЙЛОВИЧ, ПУЗЕЕВ НИКОЛАЙ ПЕТРОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.10.1989

Код ссылки

<a href="https://patents.su/3-1517136-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь последовательного кода в параллельный

Следующий патент: Устройство для мажоритарного декодирования

Случайный патент: Бункер для трудносыпучих материалов