Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1517135

Авторы: Васильев, Кузьменко, Ярмухаметов

Текст

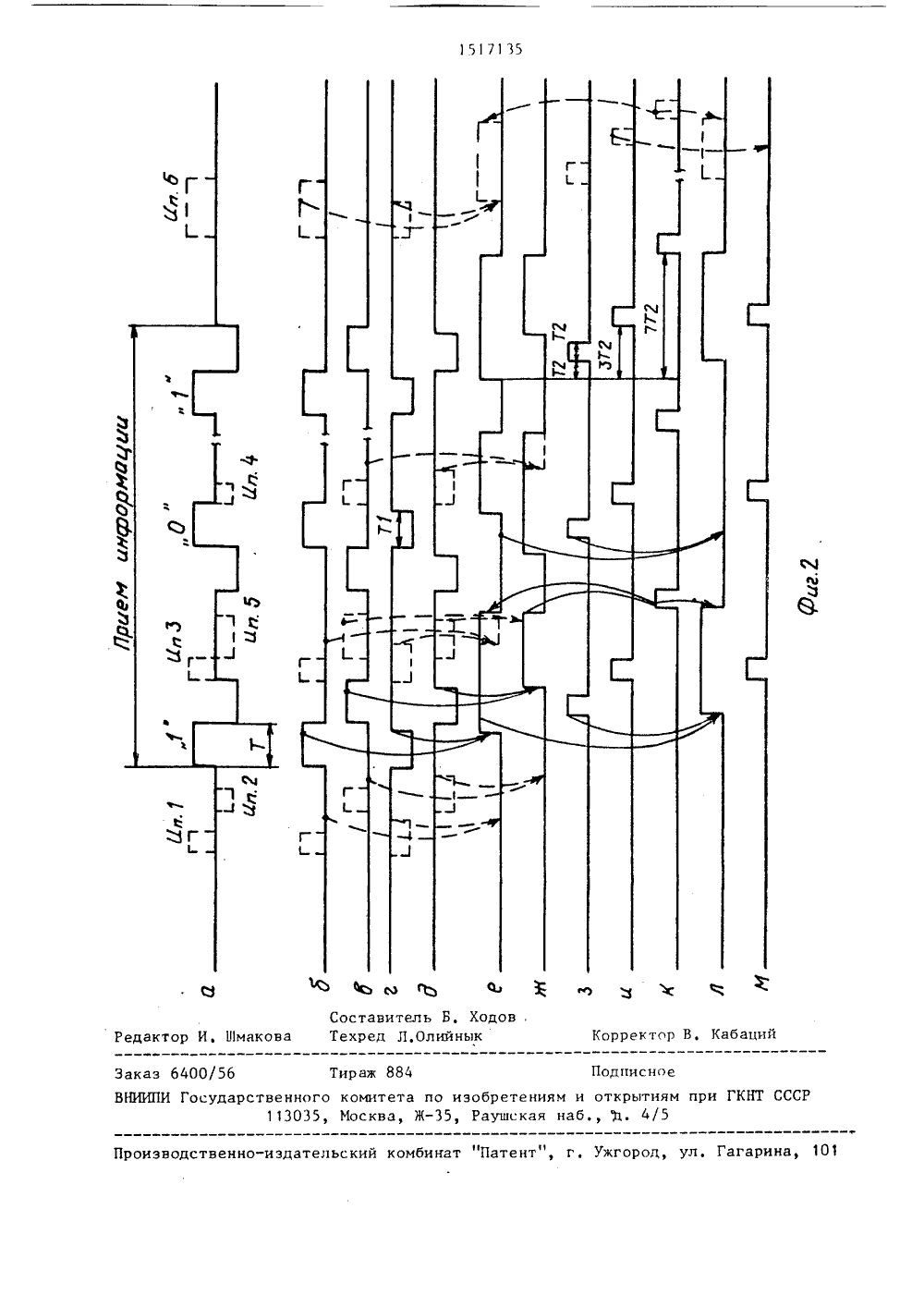

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1 А 1 119) 01) 151) 4 Н 03 М 7/00 Д,"ЦР".Р, ДИТЕКТ 1.).С):.14 Р; 4 Б)Б. О: 1. г ОПИСАНИЕ ИЗОБРЕТЕНИЯ К А ВТОРСКОМУ. СВИДЕТЕЛЬСТВУ фиг. ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР 1(56) Авторское свидетельство СССР 9 045238, кл; Н 03 М 7/00, 1982.Авторское сидетельство СССР йц 1159164, кл, Н 03 М 7/00, 1985. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛ 1 НЫЙ (57) Изобретение относится к вычислительной технике и может быть использовано при создании преобразователей информации, входящих в состав аппаратуры сопряжения цифровых уст 2райств с полудуплексными двухпроводными каналами связиИзобретение обеспечивает защиту преобразователя от коротких импульсных помех, а также одиночных импульсных помех, соизмеримых по длительности с длительностью полезного сигнала, чем обеспечивается повышение помехоустойчнвости преобразователя, Преобразова тель последовательного кода в параллельный содержит три .триггера 1,2 и 13, два элемента ИЛИ 3 и 12, генератор 4 импупьсов, два элемента И 5 и 7, два счетчика 6 и 9 импульсов, регистр 8 сдвига, два Формирователя 10 и 11 импульсов и дешифратор 2 ил.Изобретение относится к вычислительной технике и может быть использовано при создании преобразователей информации, входящих в составаппаратуры сопряжения цифровых устройств с полудуплексными двухпроводным 1 каналами связиЦелью изобретения является повыценце помехоустойчивости преобразов ател я,На фиг, грцведена блок-схема преобразователя ца фиг,2 - временныедиаграммы, поясняющие работу преобразователя с полезными сигналамипри наличии коротких импульсных, атакже одиночных импульсных помехдлительность которых соизмерима сдлительностью полезного сигнала,Преобразователь последовательного кода в параллельный содержит первый 1 и второй 2 триггерыпервыйэлемент ИПИ 3, генератор 4 импульсов,первый элемент И 5 первый счетчик 6импульсов второй элемент И 7, регистр 8 сдвига, второй счетчик 9импульсов, первый 10 и второй 11Формировагели импульсов, второй элемент ИЛИ 12, третий триггер 13 и дешифратор 14 и имеет первый 15 и второй 16 информационные входы и вход17 сброса, информационный 18 и управляющий 19 выходы.На фиг,2 соответствующими индексами обозначены следующие сигналы:а - полезные сигналы и импульсныепомехи из полудуплексного двухпроводного канала связи; б - сигналы ипомехи на входе 15; в - сигналы ипомехи на входе 16; г - сигнал навыходе формирователя 10 д - сигнална выходе формирователя 11; е - сигнал на выходе триггера 1; ж - сигналца выходе триггера 2; з, и, к - сигналы на первом, втором и третьем выходах дешифратора 4; л - сигнал навыходе триггера 13; м - сигнал навыходе элемента И 7, На временных .диаграммах показаны временные соотцоцения между входными сигналами ибиполярцыми сигц:лами канала связи,Сплошными линиями показана полезнаяинформация, пунктирными - импульсныепомехи, Импульсные помехи также помечены Ип, 1-Иц,5 длительность положительного или отрицательного импульса канала связи ранна Т. Период следования ицфор 1 а 1 цц 1 цных битов ранен 4 Т, Временной ицтернал между битами информации, а .также между десятиразрядцыми байтами одинаковый и равен2 Т.Преобразователь работает следующим образом,В исходном положении сигналом"Сброс" на входе 17 триггеры 1, 2,13 и счетчики 6, 9 приведены н нулевое значение, На первый 15 и второй 16 входы поступают полезныесигналы и импульсные помехи иэ полудуплексного двухпроводного каналасвязи.В отсутствие помех на информаци 5онные входы 15 и 16 преобразователяпоступают импульсы единичных или нулевых битов информации,При поступлении иэ канала связиединичного бита информации на входе15 появляется информационный импульсдпительностью Т, который поступаетна вход формирователя 10 и информационный вход триггера 1, По переднему фронту информационного импульсазапускается формирователь 1 О и вырабатывает отрицательный импульс, который поступает на установочный входтриггера 1. Длительность импульсаТ 1 формирователей 10 и 11 должнанаходиться в пределах Тя (Т 1(Тгде Тки - максимальная длительность короткой импульсной помехи, откоторой производится защита, При соблюдении этого неравенства к моменту35окончания импульса на выходе формирователя 10 на информационном входе триггера 1 сохраняется единичноезначение информационного импульса,40 которое заносится в триггер 1 позаднему фронту импульса формирователя 10,После окончания информационногоимпульса на входе 15 появляется45 информационный импульс на входе 16и по заднему Фронту импульса формирователя 1 устанавливается в единичное значение триггер 2.Сигнал с выхода триггера 1 проходит через элемент ИЛИ 3 и разрешает прохождение синхроимпульсов сгенератора 4 через элемент И 5 насчетчик 6 и дешифратор 14, На выходе дешифратора 14 появляются синхро 55импульсы, По переднему фронту синхроимпульса с первого выхода дешифратора 14 в триггер 13 заносится единичное значение триггера 1, Единичныесигналы на выходах триггеров 1 и 25 15поступают на вход элемента И 7 и припоявлении сицхроимпульса с второговыхода дешифратора 14 на выходе элемента И 7 появляется импульс, по которому значение триггера 13 записывается н регистр 8 сдвига, а значениесчетчика 9 увеличивается на "+1"Таким образом гри поступлениииз канала связи единичного бита информации в регистр 8 сдвига записывается единичное значение. По синхросигналу с третьего выхода дешифратора 14 через элемент ИЛИ 12 производится сброс триггеров 1, 2, 13 исчетчика 6, подготавливая преобразователь к приему следующего бита информации,При поступлении из канала сняэцнулевого бита информации информационный импульс на входе 16 появляется раньше, чем информационный импульс на входе 15, Триггер 2 устанавливается первым и запускает счетчик 6 и дешифратор 14, К моменту появления синхроимпульса на первом выходе дешифратора 14 триггер 1 не установлен, поэтому в триггер 13 заносится нулевое значение, котороепо синхроимпульсу второго выхода дешифратора 14 записывается в регистр8 сдвига, а значение счетчика 9увеличивается на "+1",Таким образом, прц поступлениииз канала связи нулевого бита информации в регистр 8 сдвига записывается нулевое значение, Синхроимпульсом с третьего выхода дешифратора14 сбрасываются триггеры 1,. 2, 13и счетчик 6, подготавливая преобразователь к приему следующего бита информации,После приема десяти бит информации на выходе счетчика 9 появляется управляющий сигнал, При приемеследующих байтов информации циклработы преобразователя повторяется,Из канала связи могут поступатькороткие импульстые помехи, например Ип,1-Ип,4, длительность которыхменьше длительности Т 1 импульсовформирователей 10 и 11, а также одиночные импульсные помехи Ип,5;Ип,б,длительность которых больше или равна длительности полезного сигнала1 71.35 1 О 15 20 25 30 35 40 45 50 55 Отсутстние передачи данных, поступают на вход формиронатепей 10 и 11Н 1 выходе сттормттронатетей 10 и 11 формируются ийПульс 1 длительное т 1 ю Т 1, которые соответственно ттосупстют на установочные вход 1 трттгероти 2, К моменту Формцронацця эадццх фронтов импульсон фсрмиронателец ца информационных входах триггеров 1 и 2 вновь устанавливается нулевое значение, Устацонка триггеров 1 и 2н единичное значение це ттроцгходцти сигналы короткой импулт гной помехи не пропускаются н схему преобразователя,В отс.утствце передачи полезнойинформации одиночная импульсная НОмеха, длительность которой соцзРрима с длительцостью поле.той цтФОмации, например Ип,6, ос йуцает цаодин из нходон, напри. ер ц т хг д 15преобразователя, На входе А ттзтронате:тя 1 О формцруетст и тгу т, с;. цтлт -ностью Т 1К момс.нту форм 1 От,:цтт.1заднего фронта импулт,с а с выход;. Ф 11 мир онат РЛЯ 1 0 цл информИИонном 13;0де триггерааходитст е,титц:цдтйСИГНтЛ ПОМЕХ 1.тто Етт;1 Ц.1 ОС ЗпзЧ ННЕзаносится н триггер .1, Ст:",т,стт с 1 йхода триггера 1 через злемецттт 1 т 3и И 5 запускает счетчик 6 дсшцфр втор 14, 1 о пепедцему фро;у сцттхОимпульса с первого 1 шкода дс 1 И 1 рзтора 14 едцштчцое з.ачецц; трггера 1деренсынается и триггер :3, Сцхроимпульс с нтсрот о выхода делфратора 14 поступает ца вход злемец,д7,но с;гнал уцранлештя апет.строй 8сдвига це вырабтт 11 аРтс 1. так;актриггер 2 находится н цуленот зт;ачении, Таким Образом одиночная поискане восприццмаетс.я как поезцая ццформация и не ттзменяет зцачеця регистра 8 сдвит д,Короткие импульсные. помех 1 п,3или Ип,4, тОстуттаютттие ца вход вормирователей 1 О и 11 но время приема полезной инфсрматтитт, нызьтнзнтсрабатывание соответственно формирователя 10 или формиронатепя 11Псзаднему фронту импул са формцроателей 10 или 11 значения триггеровили 2 иэецлются с единичного нанулевое, что не изменяет работупреобразователя, так как к моментусброса по синхроимпульсу с первоговыхода дешифратора 14 триггеров 1или 2 триггер 3 устан"влен, посп:".:.Рс нгпул,с с второго выхода дею;.фратра 14 произведен сДВКГ В реги гр 8 сдига значения сигнала сы. па триггера 13, Работа счетчи 5сд п,яекгифратора 14 поддерживает я с ппни пг 1 м значением одного иэ,.1 паб 1 ьч .;.т поием бита полезной ин. д гп п 1,со конца, Таким образом,дрс; ГКИЕ ИМПУЛЬСНЫЕ ПОМЕХИ ВОЗДЕЙСТу:цлэо н Входы преобразователя воВремя приема полезной информации, невлияют на правильную работу преобоа глаголя15Одиночная импульсная помЕха,а,-,имер 11 п5, длительность котороймерима с длительностью полезно,игнал, поступающая на вход 1 б1 й:.образовачсля во Время приема ио:ной информации, вызывает формиро .пе импульс на входе формировате 11 и не изменяет состояния других,."м, одиночные импульсные помедаительность которых соизмерис длительностью полезного сигнав.а всэдействующие на входы преобрателя во время приема полезной.ормации, не Влияют на правильнуюс .,ту преобр 1 зователя,1,.я правильной работы преобразогеля Временные параметры синхроимпул сс в на выходах дешифратора 14д.и.:а;ь 1 удовлетворять следующим соот 35;,с яениям: длительность синхроимпуль 4 Т - Т 1т 2840 В; мя появления синхроимпульса с;ного гыхода дещифратора 14 отно- . .".ельно времени установки установив. ге,ся первым триггера 1 или 2 равно 3 Т 2; 1 ремя появления синхроимпуль 45)д ;я 1 первого элемента ИЛИ генератор импульсов, выход которого соединен с первым входом первого элемента И, выход которого соединен сосчетным входом первого счетчика импульсов, второй элемент И, регистрсдвига и второй счетчик импульсов,счетный вход которого объединен суправляющим входом регистра сдвига,входы сброса первого и Второго триггеров объединены выходы регистрасдвига и второго счетчика импульсовявляются соответственно информационным и управляющим выходами преобразователя о т л и ч а ю щ и й с ятем, что, с целью повыщения помехоустойчивости преобразователя, в неговведены формирователи импульсов, Второй элемент ИЛИ, третий триггер идешифратор, первый, второй и третийВыходы которого соединены соответс 1 венно с установочным входом третьего триггера, с первым Входом второгоэлемента И и с первым входом второгоэлемента ИЛИ, выход которого соединенс входами сброса первого счетчикаимпульсов, третьЕго триггера и подключен к входу сброса первого триггера, выход третьего триггера соединенс информационным входом регистра сдвига, выходы первого и второго формироВателей импульсов подключены к установочным входам одноименных триггеров, выход первого элемента ИЛИ соединен с вторым входом первого элемента И информационный вход третьеготр"1 ггера объединен с вторым входомвэрого элемента И и, подключен квыходу первого триггера информационный вход которого объединен с входом первого формирователя импульсови является первым информационнымвходом преобразователя, третий входвторого элемента И подключен к выходу Второго триггера, информационныйвход которого объединен с входомвторого формирователя импульсов иявляется вторым информационным входомпреобразователя, выходы первогосчетчика импульсов соединены с входами дещифратора, управляющий входрегистра сдвига подключсн к выходувторого элемента И, вход сброса второго счетчика импульсов объединенс вторым входом второго элементаИЛИ и является входом сброса преобразователя,

СмотретьЗаявка

4391587, 10.03.1988

ПРЕДПРИЯТИЕ ПЯ А-3886

ВАСИЛЬЕВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, КУЗЬМЕНКО ИЛЬМИРА ЗИАТДИНОВНА, ЯРМУХАМЕТОВ АЗАТ УСМАНОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.10.1989

Код ссылки

<a href="https://patents.su/5-1517135-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь кода в сопротивление

Следующий патент: Преобразователь последовательного кода в параллельный

Случайный патент: Способ подачи смеси воздуха и кислорода в скафандр лётчика