Интегратор дельта-модулятора

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1352655

Автор: Алюшин

Текст

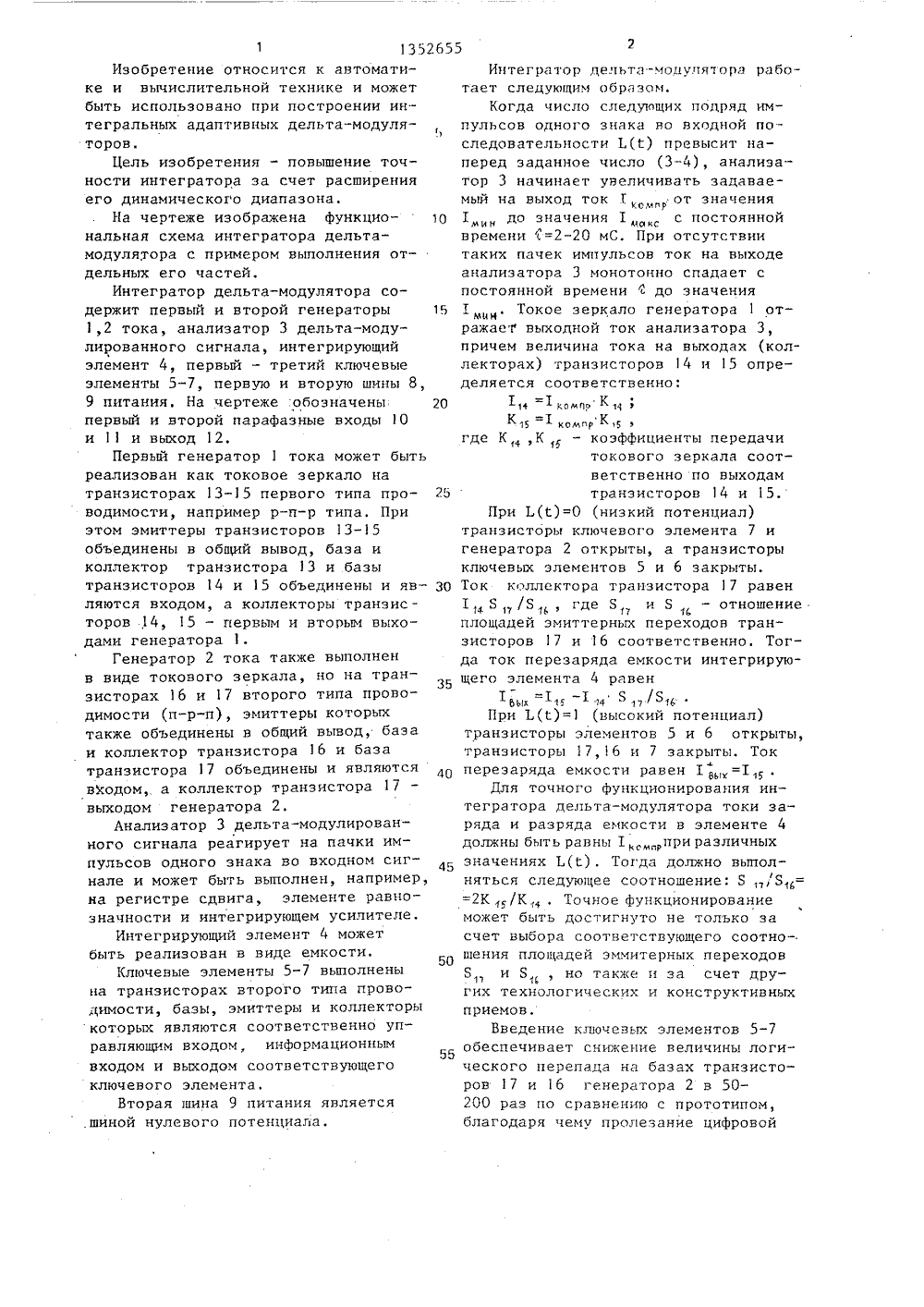

(51) 4 3 02 АНИ ЕТЕНИ Гп ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ К А ВТОРСКОМУ.СВИДЕТЕЛЬСТВ(21) 4063819/24-24 (22) 28.01.86 (46) 15.11.87. Бюл. В 42 (71) Московский инженерно-физически институт (72) А.В, Алюшин и М.В. Алюшин (53) 621.376.56(088.8) (56) Теория и проектирование электронной аппаратуры физического эксперимента/Под ред. Т.М. Агаханяна. М.: Энергоиздат, с. 61-62, рис, 1,2Патент США У 3754234, кл. Н 03 К 13/22, 1973.Авторское свидетельство СССР У 563679, кл. Н 03 М 3/02, 1975.Заявка Франции У 226131, кл. Н 04 В 1/00, 1972.(57) Изобретение относится к автоматике и вычислительной технике. Егоиспользование в интегральных адаптивных дельта-модуляторах позволяетповысить точность интегратора засчет расширения его динамическогодиапазона. Интегратор дельта-модулятора содержит генераторы 1,2 тока(токовые зеркала), анализатор 3 дельта-модулированного сигнала, интегрирующий элемент 4 и источник питания. Благодаря введению ключевыхэлементов 5-7 уменьшается величинасигнала, проникающего на выход 12.1 илИнтегратор дельта-модулятора работает следующим образом.Когда число следующих подряд импульсов одного знака во входной по,)следовательности 1. превысит наперед заданное число (3-4), анализатор 3 начинает увеличивать задаваемый на выход ток 1 к , от значения 10 1 до значения 1, , с постояннойвремени =2-20 мС, При отсутствиитаких пачек импульсов ток на выходеанализатора 3 монотонно спадает спостоянной временидо значения 15 1 . Токое зеркало генератора 1 отражае г выходной ток анализатора 3,причем величина тока на выходах (коллекторах) транзисторов 14 и 15 определяется соответственно: 20 1 1 компр КК 15 1 компр К 5где К, ,К, - коэффициенты передачитокового зеркала соответственно по выходам6 транзисторов 14 и 15,При 1.=0 (низкий потенциал)транзисторы ключевого элемента 7 игенератора 2 открыты, а транзисторыключевых элементов 5 и б закрыты.30 Ток коллектора транзистора 17 равен1 Б д, /Б , где Б, и Б- отношениеплощадей эмиттерных переходов транзисторов 17 и 16 соответственно. Тогда ток перезаряда емкости интегрирую 5 щего элемента 4 равенбык 15 1 м Б,77 БмПри 1.=1 (высокий потенциал)транзисторы элементов 5 и 6 открыты,транзисторы 17,16 и 7 закрыты, Токперезаряда емкости равен 1 ы=15 .Для точного функционирования интегратора дельта-модулятора токи заряда и разряда емкости в элементе 4должны быть равны 1,при различныхзначениях 1.(г) . Тогда должно выполняться следующее соотношение: Б Б,г==2 К 5/К Точное функционированиеможет быть достигнуто не только засчет выбора соответствующего соотноВ 0 шения площадей эммитерных переходовБ, и Б , но также и за счет других технологических и конструктивныхприемов,Введение ключевых элементов 5-7обеспечивает снижение величины логического перепада на базах транзисторов 17 и 16 генератора 2 в 50200 раз по сравнению с прототипом,благодаря чему пролезание цифровой 1 1352655Изобретение относится к автоматике и вычислительной технике и можетбыть использовано при построении интегральных адаптивных дельта-модуляторов.Цель изобретения - повышение точности интегратора за счет расширенияего динамического диапазона.На чертеже изображена функциональная схема интегратора дельтамодулятора с примером выполнения отдельных его частей,Интегратор дельта-модулятора содержит первый и второй генераторы1,2 тока, анализатор 3 дельта-модулированного сигнала, интегрирующийэлемент 4, первый - третий ключевыеэлементы 5-7, первую и вторую шины 8,9 питания. На чертеже обозначеныпервый и второй парафазные входы 10и 11 и выход 12,Первый генератор 1 тока может бытьреализован как токовое зеркало натранзисторах 13-15 первого типа проводимости, например р-н-р типа. Приэтом эмиттеры транзисторов 13-15объединены в общий вывод, база иколлектор транзистора 13 и базытранзисторов 14 и 15 объединены и являются входом, а коллекторы транзис -торов,14, 15 - первым и вторым выходами генератора 1.Генератор 2 тока также выполненв виде токового зеркала, но на транзисторах 16 и 17 второго типа проводимости (п-р-п), эмиттеры которыхтакже объединены в общий вывод, базаи коллектор транзистора 16 и базатранзистора 17 объединены и являютсявходом. а коллектор транзистора 17выходом генератора 2.Анализатор 3 дельта-модулированного сигнала реагирует на пачки импульсов одного знака во входном сигнале и может быть выполнен, например,на регистре сдвига, элементе равнозначности и интегрирующем усилителе.Интегрирующий элемент 4 можетбыть реализован в виде емкости.Ключевые элементы 5-7 выполненына транзисторах второго типа проводимости, базы, эмиттеры и коллекторыкоторых являются соответственно управляющим входом, информационнымвходом и выходом соответствующегоключевого элемента.Вторая шина 9 питания являетсяЗаказ 5577/57 Тираж 900 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 3 135последовательности Ь(С) на выход ин,тегратора через емкость перехода база коллектор транзистора 17 уменьшаетсяво столько же раз,Для нормального функционированияпрототипа размах Ь(1) должен бытьсравним с напряжением питания. По-:этому логический перепад на базахтранзисторов, эквивалентных транзисторам 7 и 16, составляют 2-15 В приЕ =2-15 В.В предлагаемом интеграторе величина логического перепада на базахтранзисторов 17 и 16 равна 50-100 мВ.Следовательно, шумы на выходе 12интегратора также уменьшены и дельтамодулятор с таким интегратором можетобработать значительно меньше (в 50200 раз) входные сигналы.Кроме того, интегратор обладаетбольшим размахом выходного напряжения П , которое может изменятьсяПкэ нас до Е и жакэ нсс где Пкэ наснапряжение насыщения транзистора.При Е п=2 В, Бнэ нас=0,1 В Б,=ЕПэас =1,7 В, что более чем в 3 раза превышают максимальный размахвыходного напряжения для прототипа.Таким образом, интегратор дельтамодулятара обладает по сравнениюс прототипом значительно большим динамическим диапазоном (в 50-700 раз),Формула изобретенияИнтегратор дельта-модулятора, содержащий анализатор дельта-модули 26554рованного сигнала, первый и второйвходы которого являютсяодноименнымивходами интегратора, выход анализатора дельта-модулированного сигнала соединен с первым входом первогогенератора тока, второй вход которого подключен к первой шине питания, второй генератор тока, вторуюшину питания и интегрирующий элемент,выход которого является выходом интегратора, о т л и ч а ю щ и й с ятем, что, с целью повышения точностиинтегратора за счет расширения егодинамического диапазона, в интегратор введены ключевые элементы, первый выход первого генератора токаподключен к первому входу второго генератора тока и к управляющему входуи выходу первого ключевого элемента,выходы второго и третьего ключевыхэлементов соединены соответственнос информационным входом первого ключевого элемента и с вторым входомвторого генератора тока, выход которого объединен с вторым выходом первого генератора тока и подключенк входу интегрирующего элемента, управляющие входы второго и третьегоключевых элементов соединены соответственно с первым и вторым входамиинтегратора, информационные входывторого и третьего ключевых элементов объединены и подключены к второмуисточнику питания.35

СмотретьЗаявка

4063819, 28.04.1986

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ

АЛЮШИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, АЛЮШИН МИХАИЛ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-модулятора, интегратор

Опубликовано: 15.11.1987

Код ссылки

<a href="https://patents.su/3-1352655-integrator-delta-modulyatora.html" target="_blank" rel="follow" title="База патентов СССР">Интегратор дельта-модулятора</a>

Предыдущий патент: Дельта-модулятор

Следующий патент: Устройство для преобразования цифрового сигнала

Случайный патент: Ассоциативное запоминающее устройство