Устройство для вычисления функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

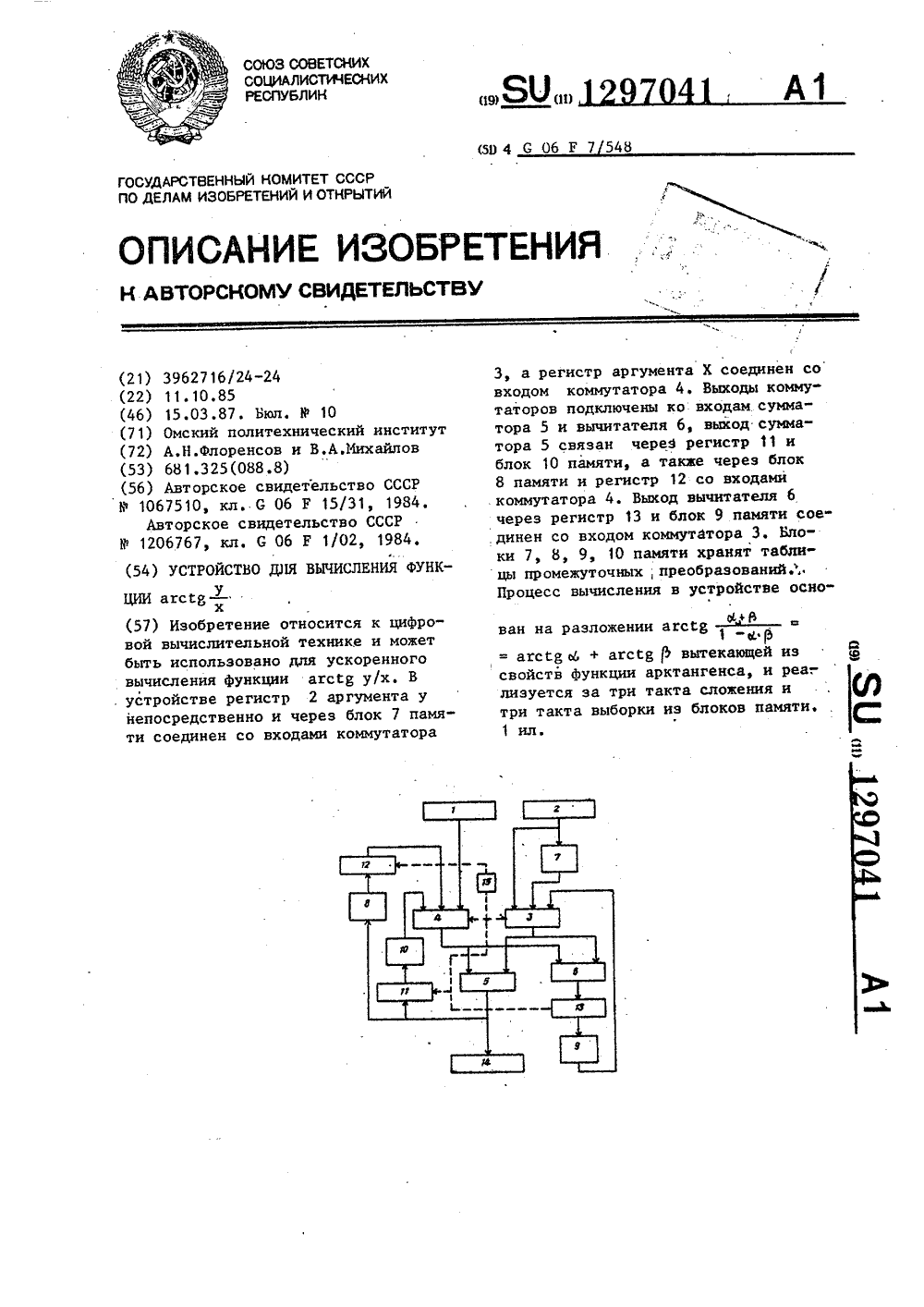

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКРЕСПУБЛИК 9) (11) 48 51)4 60 ЦИИ агсС 8 -ух ро Фф 9 ахссВ --- .1-крвытекающей рктангенса, и акта сложения из блоков па ан на разложени= агсг 8 Ы + агс свойств функции лизуется за три три такта выбор 1 иле реа-, имяти. ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗОБРЕВТОРСКОМУ СВИДЕТЕЛЬСТВ(71) Омский политехнический институт(56) Авторское свидетельство СССРР 1067510, кл. 6 06 Р 15(31, 1984.Авторское свидетельство СССРУ 1206767, кл. 6 06 Р 1/02, 1984.(54) УСТРОЙСТВО Д)И ВЫЧИСЛЕНИЯ ФУНК(57) Изобретени вой вычислитель быть использова вычисления функ . устройстве реги непосредственно ти соединен со относится к цифой технике и можето для ускоренногоции агсгя у/х. Втр 2 аргумента уи через блок 7 памяходами коммутатора 3, а регистр аргумента Х соединен совходом коммутатора 4. Выходы коммутаторов подключены ко входам сумматора 5 и вычитателя 6, выход сумматора 5 связан через регистр 11 иблок 10 памяти, а также через блок8 памяти и регистр 12 со входамикоммутатора 4. Выход вычитателя 6через регистр 13 и блок 9 памяти соединен со входом коммутатора 3. Блоки 7, 8, 9, 1 О памяти хранят таблицы промежуточных, преобразований;Процесс вычисления в устройстве осноИзобретение относится к вычисли тельной технике и предназначено для ускоренного вычисления функций агсТц - , необходимои при выполненииухпреобразования декартовых координат в полярные координаты.Цель изобретения - повьгпение точ- ности вычислений. Ба чертеже изображена блок-схема10 предлагаемого устройстваУстройство содержит регистр 1 первого аргумента, регистр 2 второго аргумента, первый и второй коммутаторы 3 и 4, сумматор 5, вычитатель 6, первый, второй, третий и четвертый блоки 7- 10 памяти, первый, второй и третий буферные регистры 11-13, регистр 14 результата и блок 15 синхронизации.Устройство вычисляет значения определяющее соотношение у- = агсгд( - , +х 2 3 позволяющее на всех этапах промежуточных, преобразований вычислять вспо" 4 могательные функции от одного аргумента разрядности и, а наличие двух аргументов учитывать с помощью суммирования на сумматоре или вычитателе.Регистр 1 первого аргумента хранит 4 значение аргумента Х, а регистр 2 второго аргумента содержит значение аргумента У, В первом блоке 7 памятих хранится таблица значений (у /4 - 1), во втором блоке 8 памяти - таблица 5 значений квадратного корня, а в третьем и четвертом блоках 9-10 памяти - таблица значений арктангенса.Устройство работает в три такта, определяемых блоком 15 синхронизации следующим образом, В первом такте сигналы от блока 15, воздействуя на управляющие входы, подключают к выходу первого коммутатора 3 первый 0 функции агсСц - путем введения вспохмогательных переменных . и Д , при 25 которых р += у, 1 - к= х,МФ (3 использования формулы агсу1-(к /:/ = агссд М + агсгц , вытекающей из свойств Функции арктангенса. Это да ет для вычисления Функции агсТд -у хВо втором такте сигналы от блока 15, воздействуя на управляющие входы, подключают к выходу первого коммутатора 3 третий его вход, к выходу второго коммутатора 4 - первый его вход, а первый и третий буферные регистры 11 и 13 фиксируют в этом такте поступающую на его вход информацию, Выход регистра 2 второго аргумента подключен к третьему входу первого коммутатора 3 со смещением на один двоичный разряд вправо, чтобы обеспечить Формирование на этом входе значения кода у/2. Ка первые входы сумматора 5 и вычитателя 6 поступает значение у/2, а на вторые их входы с выхода второго блока памяти 8 значение у /4 - 1 + х . На выходе суммато а 5 Формируется значение у/2 + у /Е - 1 з х , запоминаемое на первом буферном регистре 11, а на выходе вычитателя 6 - значение у/2 -ут/Ф - 1 т х, запоминаемое а тоетьем буферном регистре 13. В третьем та 15, воздействуя подключают второго коммута их входы, Трети 9-10 памяти вып арктангенса от тов, а сумматор результаты, обрналы от блокавляющие вхоу первого ии 4 вторыевертый блокивычисление е н о дЬ о е няют ромежуточных аргумен 5 складывает этизуя на своем выходе льтат агссц - ,у х 1 й окончател запоминаемый в регистре 14 результ та. его вход, к выходу второго коммутатора 4 третий его вход, а второй бу.ферный регистр 13 фиксирует в этомтакте поступающую на его вход информацию,В первом такте значение у с регистра 2 второго аргумента преобразуется в первом блокепамяти, образуя на его выходе значение у /4 - 1,тпоступающее через первый вход первогокоммутатора 3 на первый вход сумматора 5, на второй вход которого поступает через третий вход второгокоммутатора 4 с регистра 1 первогоаргумента значение Х. В результатена выходе сумматора 5 формируетсязначение ( в , - 1 + х), запоминаемоево втором буферном регистре 12.Составитель З,ШершневаТехред М,Ходанич Корректор Т.Колб Редактор Л,Повхан Тираж 673 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Заказ 782/52 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 3 12 КО Формула изобретенияУстройство для вычисления функции агссц - , содержащее регистр аргуменухта Х, регистр аргумента У, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сум матора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены 15 соответственно, с управляющими входами первого и второго коммутаторов, о т л и ч а ю щ е е ся тем, что, с целью повышения точности, в него введены вычитатель, блок памяти зна чений (у /4 - 1), блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами пер вого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента 41 4У и регистра аргумента Х соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений (у /4 - 1) и второго буферного регистра соответственно, адресный вход блока памяти значений (у /421) соединен с выходом регистра аргумента У, выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенсов, выход сумматора соединен . с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным вхоДЬм второго буферного регистра, третИй, четвертый и пятый выходы блока синхронизации соединены с входами синхронизации соответственно первого, втот. рого и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенса.

СмотретьЗаявка

3962716, 11.10.1985

ОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ФЛОРЕНСОВ АЛЕКСАНДР НИКОЛАЕВИЧ, МИХАЙЛОВ ВЯЧЕСЛАВ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/548

Метки: вычисления, функции

Опубликовано: 15.03.1987

Код ссылки

<a href="https://patents.su/3-1297041-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции</a>

Предыдущий патент: Устройство для вычисления функций

Следующий патент: Устройство для возведения в квадрат

Случайный патент: Звукометрический способ диагностики состояния шаровой мельницы