Цифровой синтезатор сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

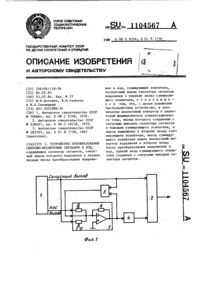

)4 НОЗВ 190 ВСЕ 1.йЖ ОПИСАНИЕ ИЗОБРЕТЕНИ У ЛЬС ВТОРСКОМУ СВ л. У 14заочный электроитут связиов и А.Д.Ревун(54 (57 ЦИФРОВОЙИзобретен ОВ ЕЗАТОР С тносится адиоспользовано технике и м.бформированиятот в радиолсистемах. Сных составля сигналов и синтеза час кационнь в язнь нижается уровень паразитющих выходных сигналов.жит блок формирования1, накопитель фазы 2,ератор 3, счетчик 4,стр-во соде ода частоть талонный г ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское сУ 813675, кл. Н25.1078Патент США Укл. 328-14, 18.0 ЦАП 5) ФНЧ 6, три регистра памяти(РП) 7, 8 и 9, умножитель кодов 10,три инвертора 11, 12 и 13, сумматор14 и коммутатор 15. Коды, формируемые счетчиком 4, подаются в качествеуправляющих на коммутатор 15, обеспечивая последовательно появление навыходах коммутатора 15 приближенныхвыборок, присутствующих на его 4-хвходах. При этом один код поступаетна вход коммутатора 15 непосредственно с выхода РП 7, а остальныекоды вычисляются при помощи РП 9,умножителя кодов 10, инверторов 11,12, 13 и сумматора 14. Полученныйс выхода коммутатора 15 код черезРП 9 поступает на ЦАП 15 и далеена ФНЧ 6, в результате чего формируется желаемый синусоидальный сигнал. Цель достигается введением РП7,8,9, умножителя кодов 10, инверторов 11,12,13, сумматора 14 и коммутатора 15. 2 ил.Изобретение относится к области радиотехники и может бытьсипользовано для формирования сигналов и синтеза частотв радиолокационных и связных системах. 5Цель изобретения - снижение уровня паразитных составляющих выходных сигналов,На фиг. изображена структурная электрическая схема цифрового синте б затора сигналов; на Фиг.2 - Форма сигнала. Цифровой синтезатор сигналов содержит блок 1 формирования кода1 частоты, накопитель 2 Фазы, эталонный генератор 3, счетчик 4, цифроаналоговый преобразователь (ЦАП) 5, фильтр 6 нижних частот (ФНЧ), первый пегистр 7 памяти, второй регистр 8 памяти, третий регистр 9 памяти, умножитель 10 кодов, первый 11, второй 2 и третий 13 инверторы, сумматор 4 и коммутатор 15.Цифровой синтезатор сигналов работает следующим образом.На периоде сиитеэируемого сигнала формируется Фиксированное число отсчетов 4 (фиг.2), Формируются выборкири и = 4, где и = 0,1, 2 1 = 0,1,2,3, При и =:411 Формируются выборки2 при и = 4+2 - выборки -, при и = 41+3 - выборки -1+ - и- .Поскольку2в общем случае синтезируемая часто- З 5 та Е и опорная частота Г, эталонного генератора не кратны между собой, значения Фазы синтезируемого сигнала в моменты переполнения накопителя фазы 2 равны " + 11, Поскольку обычно Г, Гто Я- . Таким образом, при небольших Яобеспечивается высокая точность представления выборок и, следовательно низкий уровень паразитных составляю щих. В процессе работы импульсы переполнения (появление каждого из них соответствует приращению фазы примерно на т /2) поступают на счетчик 4, выполненный двухразрядным, в котором И последоваетльно формируются коды 00,01,10,11,00 и т,д. В первый регистр 7 памяти в момент переполнения накопителя 2 Фазы записывается значение остатка кода Фазы О, которое 33 хранится в нем до появления следующего импульса переполнения накопителя 2 фазы. формируемые коды подаются в качестве управляющих на коммутатор5, обеспечивая последовательно появление на выходе коммутатора приближенных выборок Я ,1-Ц+1 О,-Я+ 2 л1+0,2,и т,д которые присутствуют на четырех его входах, причемкоды , поступают на первый входкоммутатора 15 непосредственно свыхода первого регистра 7 памяти, аостальные. вычисляются. Так, кодФазы - , , подаваемый на третийвход коммутатора 15, формируется по.средством изменение знака кода свыхода первого регистра 7 памяти,код на четвертом входе Формируется посредством возведения в квадратзначений кода фазы Цв моментыпереполнения, делением полученногорезультата на два и вычитанием этого числа из единицы, хранимой в .третьем регистре 9 памяти. Код напервом входе коммутатора 15 формируется изменением знака кода, присутствующего на четвертом входе коммутатора 15,Вычисление кодов (2 и 1 в2осуществляется соответственно в умножителе 10 кодов и сумматоре 14.Из этих приблюкенных выборок, присутствующих на четырех входах коммутатора 15, на выход при очередномпереполнении накопителя 2 фазы проходит лишь одна, причем порядок ихпоявления на выходе коммутатора 15определяется кодом, формируемым всчетчике 4. Так, например, при управляющем коде 00 на выход коммутатора 15 проходит код числа Я свторого входа. При управляющем коде01 к выходу коммутатора 15 подключентретий вход, т,е. передается код2числа 1-0, 12.При коде управления 10на выход проходит код числа (-Я)с четвертого входа, а при коде 11 квыходу коммутатора 15 подсоединен2первый вход, т,е. код числа -(1- Я,/2) .Далее процесс повторяется.1При этом деление на два выходного кода умножителя 1 О кодов осуществляется простым сдвигом выходныхразрядов в сторону уменьшения на1 разряд. Полученный с выхода комму -татора 15 код через третий регистр 9памяти поступает на ЦАП 5 и далее наФНЧ 6, в результате чего и Формируется желаемый синусоидальный сигнал,1224949 1 О Составитель Н,Чеканактор Е.Копча Техред И.Попович ектор М.Максимишинец 1961/55 Тираж 81 ВНИИПИ Государственн по делам изобрет 113035, Москва, ЖПодписно к ета СССРкрытийя наб., д.4/5 о комий и ска роизводственно-полиграфическое предприятие,г.ужгрод,ул.Проектная, 4 Формула изобретения Цифровой синтезатор сигналов, содержащий блок формирования кода частоты, выход которого соединен 5 с кодовым входом накопителя фазы, тактовый вход которого подключен к выходу эталонного генератора, а выход переполнения соединен с счетным входом счетчика, а также последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, о т л и ч а ю щ и й с я тем, что, с целью снижения уровня паразитных составляющих выходных сигналов, введены последовательно соединенные первый регистр памяти, умножитель кодов, первый инвертор, сумматор, второй инвертор, коммутатор и второй регистр памяти, а так же третий регистр памяти и третий инвертор, вход которого соединен с выходом первого регистрапамяти, с вторым входом умножителя кодов и с вторым входом коммутатора, а выход подсоединен к третьему входу коммутатора, четвертый входкоторого подключен к выходу сумматора, вход управления коммутатораподключен к выходу счетчика, второйвход сумматора подключен к выходутретьего регистра памяти, тактовыйвход второго регистра памяти подключен к выходу переполнения накопителя фазы, выход второго регистра памяти подключен к входу цифроаналогового преобразователя, тактовый вход блока формирования кодачастоты подсоединен к выходу, эталонного генератора, а кодовый входи тактовый вход первого регистрапамяти подключены соответственно к кодовому выходу и к выходу переполнения накопителя фазы.

СмотретьЗаявка

3804087, 18.10.1984

ВСЕСОЮЗНЫЙ ЗАОЧНЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

КОЧЕМАСОВ ВИКТОР НЕОФИДОВИЧ, РЕВУН АЛЕКСАНДР ДМИТРИЕВИЧ

МПК / Метки

МПК: H03B 19/00

Метки: сигналов, синтезатор, цифровой

Опубликовано: 15.04.1986

Код ссылки

<a href="https://patents.su/3-1224949-cifrovojj-sintezator-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой синтезатор сигналов</a>

Предыдущий патент: Кварцевый генератор

Следующий патент: Многоканальный имитатор случайных сигналов

Случайный патент: Ткацкий станок с волнообразно подвижным в направлении основы зевом