Устройство преобразования синусно-косинусных сигналов в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

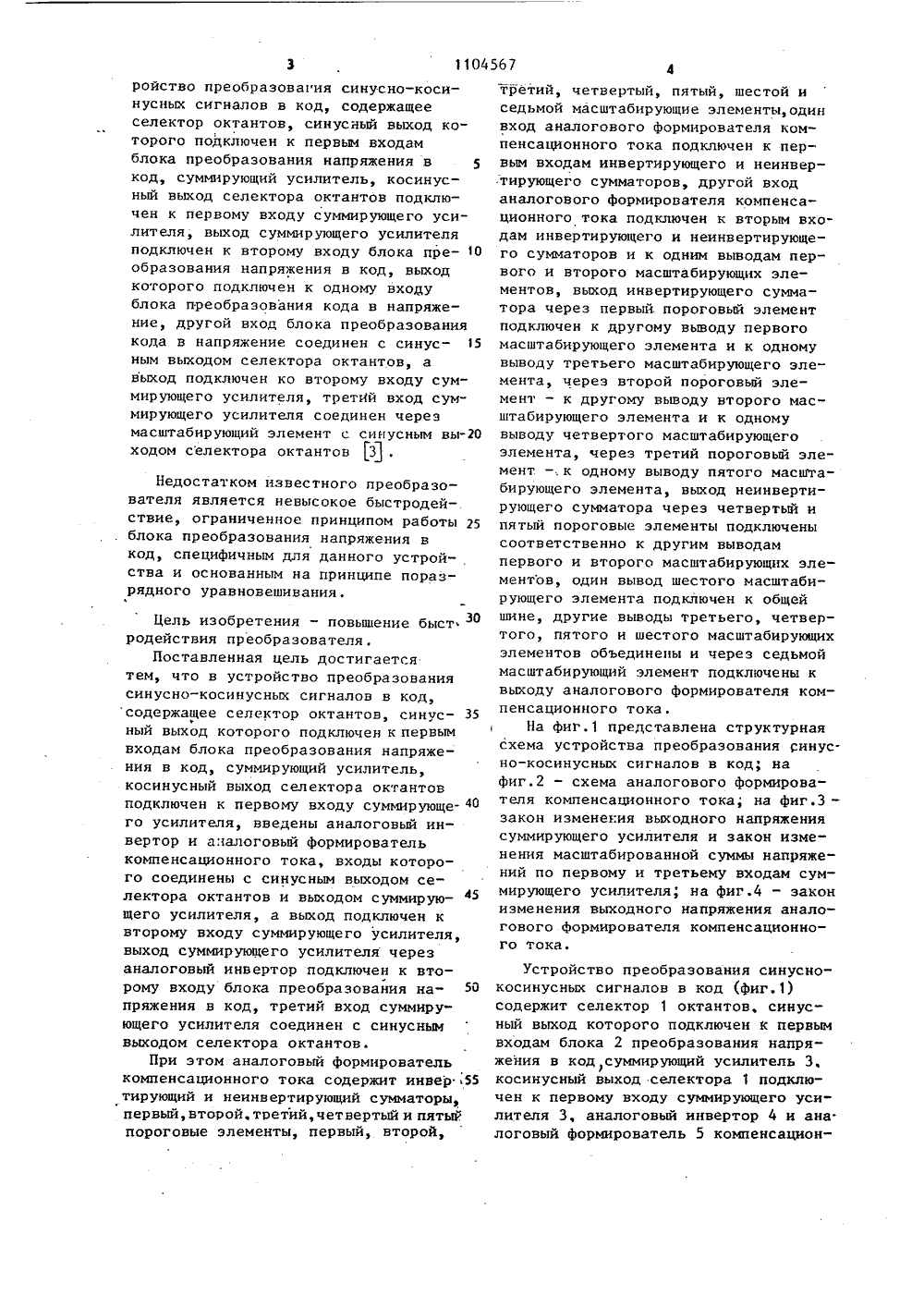

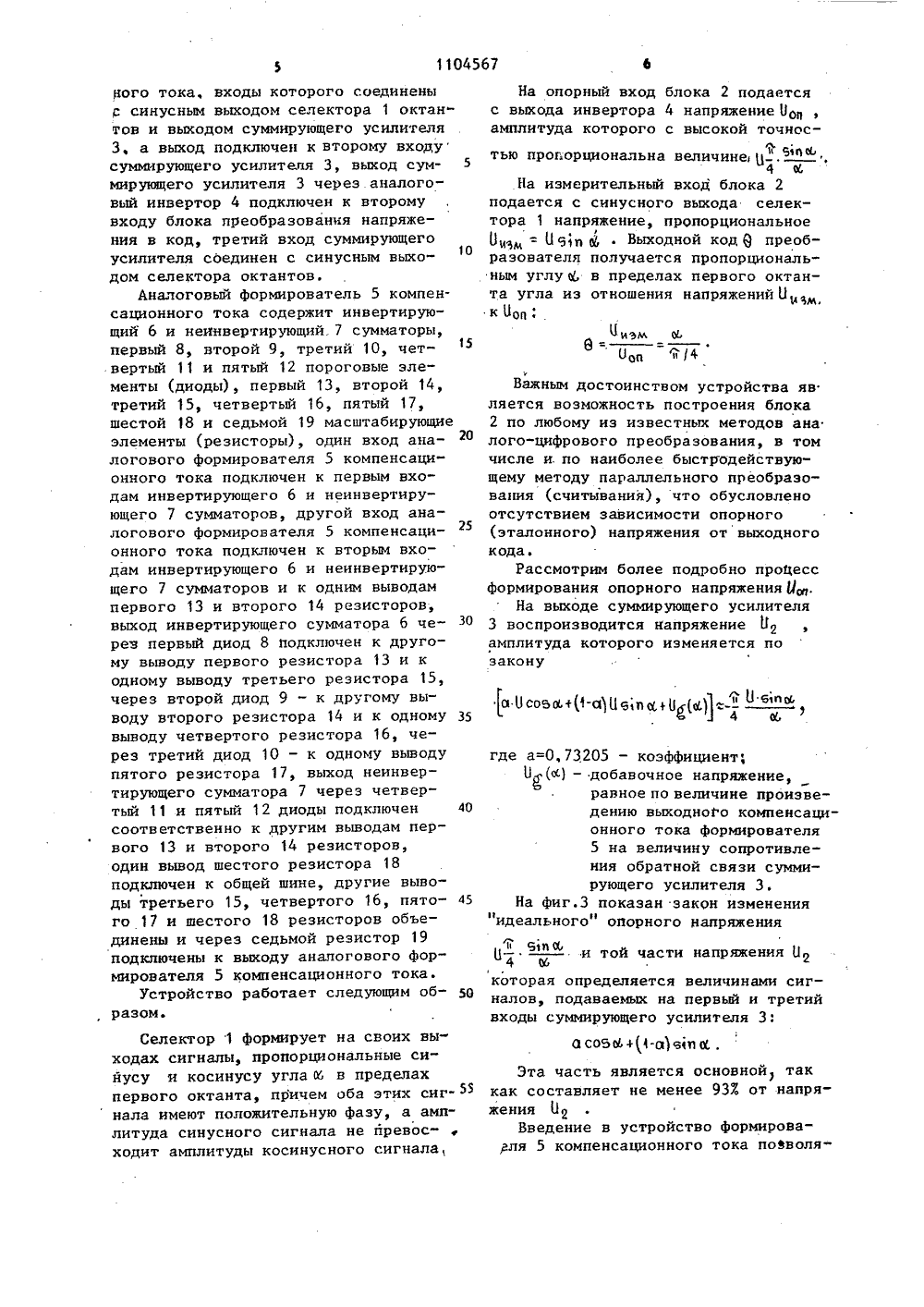

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 09 011 С 08 С 9/04; С 01 В 7/30 ПИСАНИЕ ИЗОБРЕТЕНИ АВТОРСК ВИДЕТЕЛЬСТВ(54) (57) СИНУСНО-К содержаще ный выход входам бл ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(56) 1. Авторское свидетельство ССС, У 706864, кл. С 08 С 9/00, 19762. Авторское свидетельство СССРУ 328497, кл. С 08 С 19/28, 1970.3. Авторское свидетельство СССРВ 283701, кл. С 01 В 7/30, 1967(прототип).УСТРОЙСТВО ПРЕОБРАЗОВАНИЯСИНУСНЫХ СИГНАЛОВ В КОД,селектор октантов, синускоторого подключен к первымка преобразования напряжения в код, суммирующий усилитель, косинусный выход селектора октантов подключен к первому входу суммирующего усилителя, о т л и ч а.ю щ е - е с я тем, что, с целью повышения быстродействия устройства, в него введены аналоговый инвертор и аналоговый формирователь компенсационного тока, входы которого соединены с синусным выходом, селектора октантов и выходом суммирующего усилителя, а выход подключен к второму входу сум мирующего усилителя, вьжод суммирующего усилителя через аналоговый инвертор подключен к второму входу блока преобразования напряжений в код, третий вход суммирующего усилителя соединен с синусным выходом селектора октантов.11045 б 7 2. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что аналоговый формирователь компенсационного тока содержит инвертирующий и неинвертирующий сумматоры, первый, второй, третий, четвертый и пятый пороговые элементы, первый, второй, третий, четвертый, пятый, шестой иедьмой масштабирующне элементы, один вход аналогового формирователя компенсационного тока подключен к первым входам инвертирующего и неинвертирующего сумматоров, другой вход аналогового формирователя компенсационного тока подключен к вторым входам инвертирующего и неинвертирующего сумматоров и к одним выводам первого и второго масштабирующих элементов, выход инвертирующего сумматора через первый пороговый элемент подключен к другому выводу первого масштабирующего Изобретение относится к автоматике и вычислительной технике, в частности к аналого-цифровым преобразователям, обеспечивающим связь цифровых вычислительных машин с устройствами, выдающими информацию в аналоговой форме.Известен преобразователь угла поворота вала в код, содержащий синус- но-косинусный датчик, выходы которого 10 через фазосдвигаюшую цепь подключены к выпрямителю, а через фазовые детек. торы - к селектору октантов, другие входы фазовых детекторов соединены с выходом источника опорного напряжения, первые выходы селектора октантов подключены к одним входам преобразователя напряжения в код, вторые - к первым двум входам операционного уси лителя, а выход операционного усили- о теля подключен к другому входу преоб. разователя напряжения в код (ПНК) 1,Недостатками такого преобразователя являются его сложность, невысокие точность и быстродействие. Так, ве личина методической погрешности преобразования превосходит 7 . В формировании опорного напряжения ПНК участвуют блоки (фазосдвигающая цепь и выэлемента и к одному выводу третьегомасштабирующего элемента, через вто-,рой пороговый элемент - к другому. вы.воду второго масштабирующего элемента и к одному выводу четвертого масштабирующего элемента, Через третийпороговый элемент - к одному выводупятого масштабирующего элемента, выход неинвертирующего сумматора черезчетвертый и пятый пороговые элементыподключены соответственно к другим выводам первого и второго масштабирующих элементов, один вывод шестогомасштабирующего элемента подключенк общей шине, другие выводытретьего, четвертого, пятого ишестого масштабирующих элементовобъединены и через седьмой масштабирующий элемент подключены к выходуаналогового формирователя компенсационного тока. прямитель), усложняющие преобразователь и увеличивающие как инструментальную погрешность, так и инерционность формирования опорного напряжения ПНК, что ограничивает возможности такого преобразователя при организации, например, многоканальной работы.Известен преобразователь угла поворота в цифровой код, содержащий суммирующий усилитель, ко входам которого через селектор октантов и резисторы связи подключены синусная и косинусная обмотки синусно-косинусного вращающегося трансформатора (СКВТ), а выход соединен с шиной питания декодирующего преобразователя (ПКН), сумматор, подключенный к выходам преобразователя напряжение - код (ПНК) и блок формирования корректирующего кода, выполненный в виде дешиф- ратора с элементами ИЛИ, входы которого подсоединены к выходам старших разрядов ПНК, а выходы соединены с сумматором 21.Недостатком данного преобразовате. ля является его сложность. Наиболее близким по техническомурешению к изобретению является устройство преобразования синусно-косинусных сигналов в код, содержащее селектор октантов, синусный выход которого подключен к первым входам блока преобразования напряжения в код, суммирующий усилитель, косинусный выход селектора октантов подключен к первому входу суммирующего усилителя, выход суммирующего усилителя подключен к второму входу блока пре О образования напряжения в код, выход которого подключен к одному вхоцу блока преобразования кода в напряжение, другой вход блока преобразования кода в напряжение соединен с синус ным выходом селектора октантов, а выход подключен ко второму входу суммирующего усилителя, третий вход суммирующего усилителя соединен через масштабирующий элемент с синусным выходом селектора октантов 3.Недостатком известного преобразователя является невысокое быстродействие, ограниченное принципом работы 25 блока преобразования напряжения в код, специфичным для данного устройства и основанным на принципе поразрядного уравновешивания,Цель изобретения - повышение быст родействия преобразователя.Поставленная цель достигается тем, что в устройство преобразования синусно-косинусных сигналов в код, содержащее селектор октантов, синус ный выход которого подключен к первым входам блока преобразования напряжения в код, суммирующий усилитель, косинусный выход селектора октантов подключен к первому входу суммирующе О го усилителя, введены аналоговый инвертор и аналоговый формирователь компенсационного тока, входы которого соединены с синусным выходом селектора октантов и выходом суммирующего усилителя, а выход подключен к второму входу суммирующего усилителя, выход суммирующего усилителя через аналоговый инвертор подключен к второму входу блока преобразования на О пряжения в код, третий вход суммирующего усилителя соединен с синусным выходом селектора октантов.При этом аналоговый формирователь компенсационного тока содержит инвер 55 тирующий и неинвертирующий сумматоры, первый, второй. третий,четвертыйи пятык пороговые элементы, первый, второй,третий, четвертый, пятый, шестой и седьмой масштабирующие элементы, один вход аналогового формирователя компенсационного тока подключен к первым входам инвертирующего и неинвертирующего сумматоров, другой вход аналогового формирователя компенсационного тока подключен к вторым входам инвертирующего и неинвертирующего сумматоров и к одним выводам первого и второго масштабирующих элементов, выход инвертирующего сумматора через первый пороговый элемент подключен к другому выводу первого масштабирующего элемента и к одному выводу третьего масштабирующего элемента, через второй пороговый элемент - к другому выводу второго масштабирующего элемента и к одному выводу четвертого масштабирующего элемента, через третий пороговый элемент в ,к одному выводу пятого масштабирующего элемента, выход неинвертирующего сумматора через четвертый и пятый пороговые элементы подключены соответственно к другим выводам первого и второго масштабирующих элементов, один вывод шестого масштабирующего элемента подключен к общей шине, другие выводы третьего, четвертого, пятого и шестого масштабирующих элементов объединены и через седьмой масштабирующий элемент подключены к выходу аналогового формирователя компенсационного тока.На фиг.1 представлена структурная схема устройства преобразования синус. но-косинусных сигналов в код; на фиг.2 - схема аналогового формирователя компенсационного тока; на фиг.3 - закон изменения выходного напряжения суммирующего усилителя и закон изменения масштабированной суммы напряжений по первому и третьему входам суммирующего усилителя; на фиг.4 - закон изменения выходного напряжения аналогового формирователя компенсационного тока.Устройство преобразования синуснокосинусных сигналов в код (фиг.) содержит селектор 1 октантов, синусный выход которого подключен к первым входам блока 2 преобразования напряжения в код суммирукнций усилитель 3,)косинусный выход селектора 1 подключен к первому входу суммирующего усилителя 3, аналоговый инвертор 4 и ана. логовый формирователь 5 компенсацион1104567 51 О15 иэм М0 "оп ц /ф Селектор 1 формирует на своих выходах сигналы, пропорциональные си" йусу и косинусу угла м в пределах первого октанта, причем оба этих сиг"55 ного тока, входы которого соединеныс синусным выходом селектора 1 октан" тов и выходом суммирующего усилителя 3, а выход подключен к второму входу суммирующего усилителя 3, выход суммирующего усилителя 3 через аналоговый инвертор 4 подключен к второму входу блока преобразования напряжения в код, третий вход суммирующего усилителя соединен с синусным выходом селектора октантов.Аналоговый формирователь 5 компенсационного тока содержит инвертирующий 6 и неинвертирующий. 7 сумматоры, первый 8, второй 9, третий 10, четвертый 11 и пятый 12 пороговые элементы (диоды), первый 13, второй 14, третий 15, четвертый 16, пятый 17,шестой 18 и седьмой 19 масштабирующие элементы (резисторы), один вход аналогового формирователя 5 компенсационного тока подключен к первым входам инвертирующего 6 и неинвертирующего 7 сумматоров, другой вход аналогового формирователя 5 компенсационного тока подключен к вторым входам инвертирующего 6 и неинвертирующего 7 сумматоров и к одним выводам первого 13 и второго 14 резисторов, выход инвертирующего сумматора 6 через первый диод 8 подключен к другому выводу первого резистора 13 и к одному выводу третьего резистора 15, через второй диод 9 - к другому выводу второго резистора 14 и к одному выводу четвертого резистора 16, через третий диод 10 - к одному выводу пятого резистора 17, выход неинвертирующего сумматора 7 через четвертый 11 и пятый 12 диоды подключен соответственно к другим выводам первого 13 и второго 14 резисторов, один вывод шестого резистора 18 подключен к общей шине, другие выводы третьего 15, четвертого 16, пятого 17 и шестого 18 резисторов объединены и через седьмой резистор 19 подключены к выходу аналогового формирователя 5 компенсационного тока.Устройство работает следующим образом. нала имеют положительную фазу, а амплитуда синусного сигнала не йревосходит амплитуды косинусного сигнала,20 25 30 35 40 45 50 На опорный вход блока 2 подается с выхода инвертора 4 напряжение Ц амплитуда которого с высокой точносг тью пропорциональна величине цФ аНа измерительный вход блока 2 подается с синусного выхода селектора 1 напряжение, пропорциональноеЦм = 091 в. Выходной код Я пРеобраэователя получается пропорциональным углу , в пределах первого октанта угла из отношения напряжений ц, к цоп,УВажным достоинством устройства яв ляется возможность построения блока 2 по любому из известных методов ана лого-цифрового преобразования, в том числе и.по наиболее быстродействующему методу параллельного преобразования (считывания), что обусловлено отсутствием зависимости опорного (эталонного) напряжения от выходного кода.Рассмотрим более подробно процесс формирования опорного напряжения Иц,На выходе суммирующего усилителя 3 воспроизводится напряжение В амплитуда которого изменяется по закону где а=0,73205 - коэффициент;Ц( - добавочное напряжение,равное по величине произведению выходноГо компенсационного тока формирователя5 на величину сопротивления обратной связи суммирующего усилителя 3.На фиг.3 показан закон изменения"идеального" опорного напряженияЦ -- и той части напряжения 01 Ъиа,4 (6которая определяется величинами сигналов, подаваемых на первый и третийвходы суммирующего усилителя 3: Эта часть является основной так как составляет не менее 932 от напряжения цВведение в устройство формировааля 5 компенсационного тока позволя

СмотретьЗаявка

3561061, 04.03.1983

ПРЕДПРИЯТИЕ ПЯ М-5537

КОТОВИЧ ЮРИЙ ВИКТОРОВИЧ, СЕМЕНЕЦ ВАЛЕНТИН МИХАЙЛОВИЧ, ТЕПЛИЦКИЙ ВЛАДИМИР ЛЬВОВИЧ

МПК / Метки

Метки: код, преобразования, сигналов, синусно-косинусных

Опубликовано: 23.07.1984

Код ссылки

<a href="https://patents.su/6-1104567-ustrojjstvo-preobrazovaniya-sinusno-kosinusnykh-signalov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Устройство преобразования синусно-косинусных сигналов в код</a>

Предыдущий патент: Преобразователь угла поворота вала в код

Следующий патент: Преобразователь перемещений в код

Случайный патент: Пресс-подборщик