Преобразователь синусно-косинусных сигналов в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

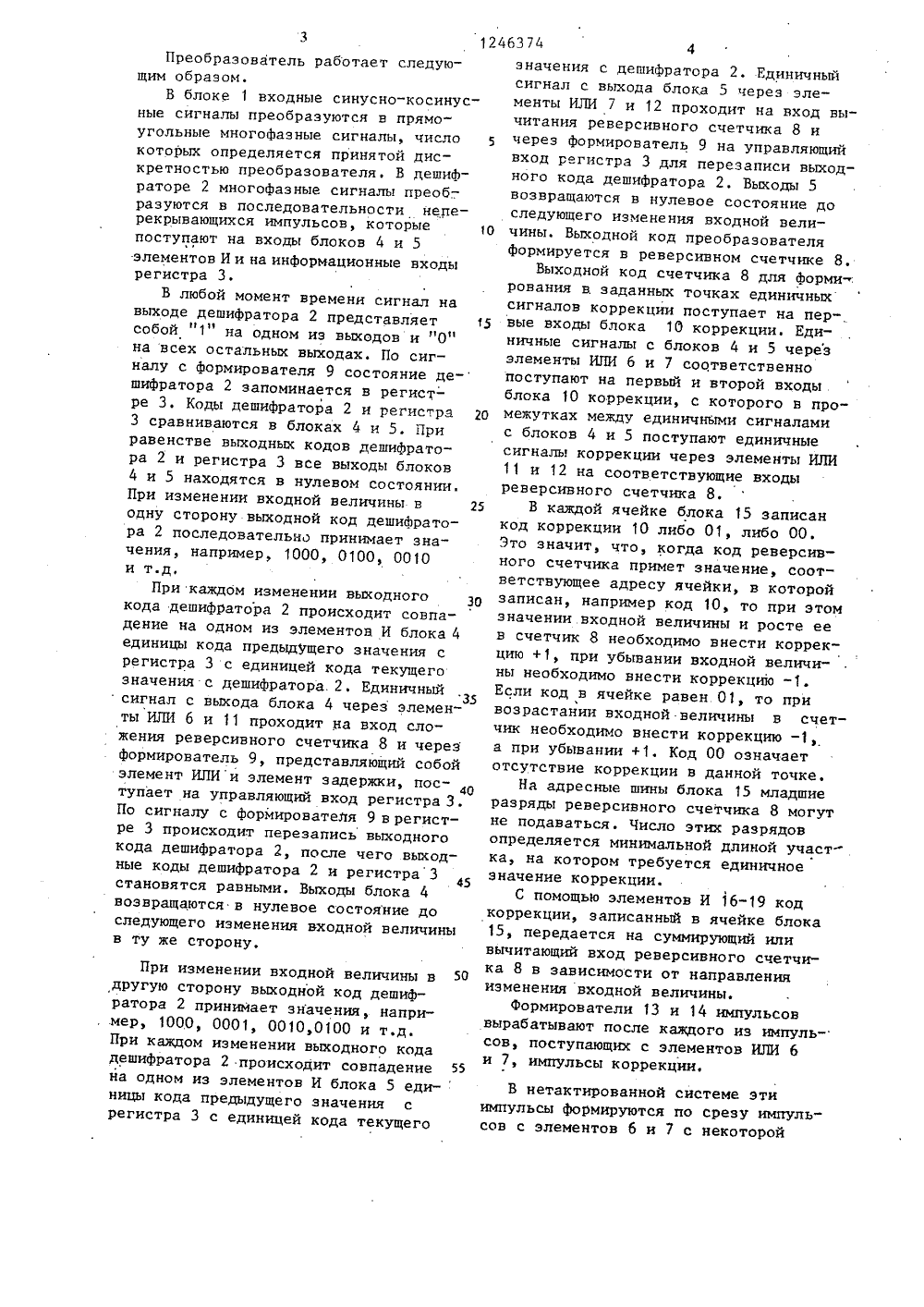

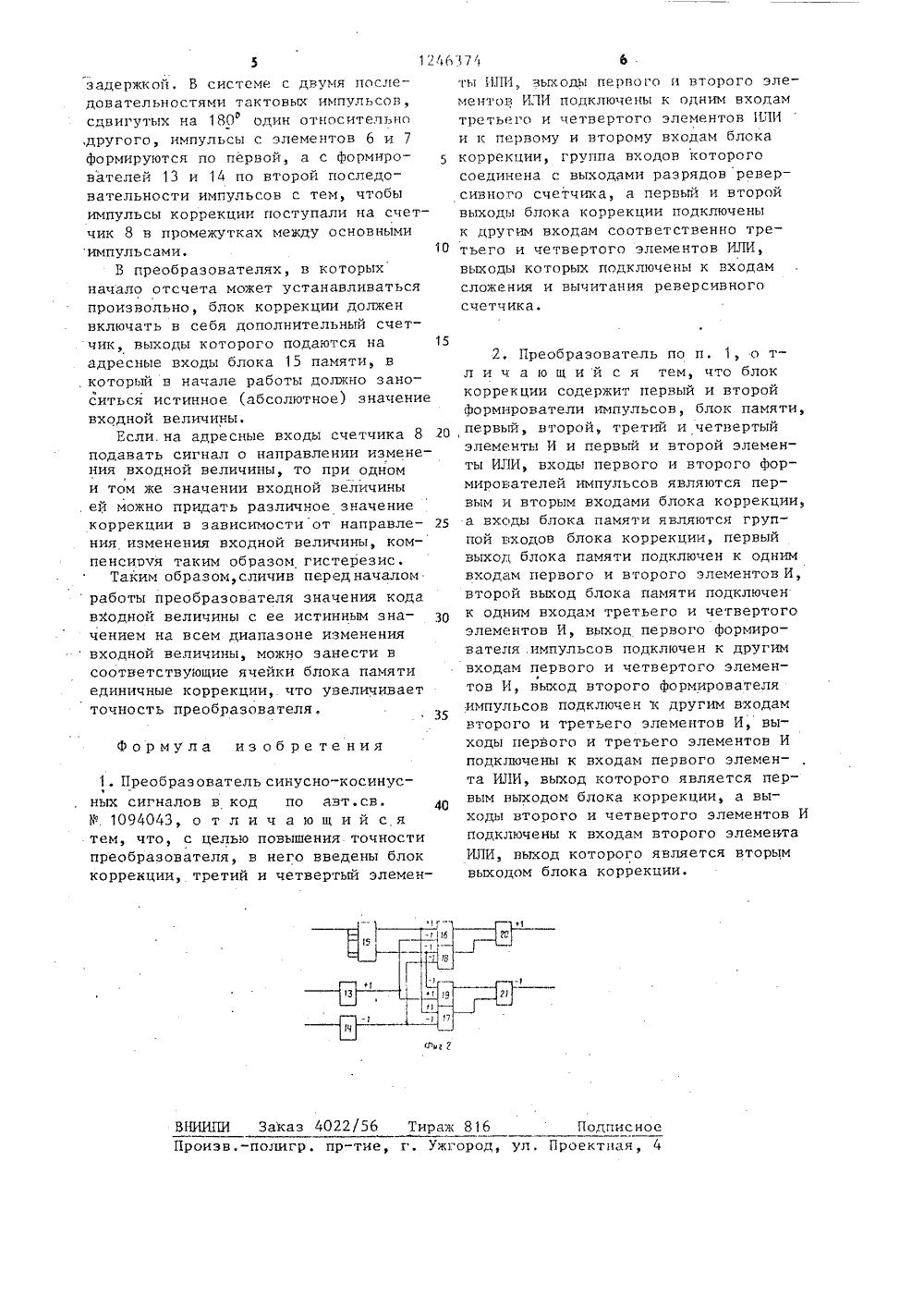

СРЫТИЙ ЕТЕЛЬСТ ВТОРСКОМУ 54 ЫХ 57 ПРЕОБРАЗО ИГНАЛОБ В Изобретен и вычисли 24юл,927Э.М.Колес тик быт использов сточников числительнь СССР1982. ния то коррек идетельст 08 С 9/00 е ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И О САНИЕ ИЗОБРЕТЕНИ(53) 681,325(08 (56) АвторскоеВ 1094043, кл,АТЕЛЬ СИНУСНО-КОСИНУСе относится к автомаельной технике и может но для связи аналого- информации с цифровым устройством. С целью сти преобразователя величины выходногокода по известной заранее величинеошибки синусно-косинусные сигналыпреобразуются в блоКе 1 в системумногофазных сигналов, В зависимостиот соотношения амплитуды входных сигналов преобразователя на одном извыходов дешифратора 2 формируется еди-ничный сигнал, Значение предыдущегосигнала хранится в регистре 3, В блоках 4 и 5 элементов И сравниваютсязначения кода текущего сигнала с предыдущим. При изменении на "1" в однусторону текущего кода по сравнению спредыдущим Формируются импульсы навыходе элемента ИЛИ б, код реверсивного счетчика 8 изменяется на "1" в одну сторону, а содержимое дешифратора 2 переписывается в регистр 3 повыходному импульсу формирователя 9,При изменении на "1" в другую сторонутекущего кода Формируются импульсына выходе элемента ИЛИ 7 а код реверсивного счетчика 8 изменяется на"1 в другую сторону, и содержимоедешифратора 2 переписывается в .регистр 3. В блоке 10 коррекции хранится код поправки, который в зависимости отвыходного кода реверсивногосчетчика 8 инаправления его изменениявводится через элементы ИЛИ 11,ИПИ 12на входы сложения или вычитания реверсивного счетчика 8.1,э.п.ф-лы, 2 ил.Изобретение относится к автоматике и вычислительной технике, может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством и является усовершенствованием изобретения по авт,св. Р 1094043. Цель изобретения - повышение точиости преобразователя путем коррекции величины выходного кода по известной заранее величине ошибки.На Фиг. 1 представлена структурная схема преобразователя; на фиг. 2 - структурная схема блока коррекции. 10 Преобразователь содержит блок 1 преобразования синусно-косинусных сигналов в многофазные сигналы, выходы которого через дешифратор 2 подключены к информационным входам ре гистра 3 и к одним группам входов первого 4 и второго 5 блоков элементов И, другие группы входов которых соединены с выходами разрядов регистра 3, а выходы первого 4 и второго 5 блоков элементов И подключены соответственно к входам первого 6 и вто. - рого 7 элементов ИЛИ, реверсивный счетчик 8, формирователь 9 импульсбв, входы которого соединены с выходами 30 элементов ИЛИ б и 7, а выход подключен к синхронизирующему входу регистра 3. Выходы элементов ИЛИ 6 и 7 подклчены к первому и второму входам блока 10 коррекции, группа входов которого соединена с выходами разрядов реверсивного счетчика 8.Выход элемента ИЛИ 6 и первый выходблока 10 через элемент ИЛИ 11 подключены к входу сЛожения реверсивного счетчика 8, а выход элемента ИЛИ 7 и второй выход блока 10 через элемент ИЛИ 12 - к входу вычитания реверсивного счетчика 8.Блок 10 коррекции содержит формирователи 13 и 14 импульсов, блок 15 памяти, первый 16, второй 17, третий 18 и четвертый 19 элементы И, первый 20 и второй 21 элементы ИЛИ. Входы Формирователей 13 и 14 импульсов являются первым и вторым входами блока 10 коррекцииа входы блока 15 памяти - группой входов блока 10 коррекции:, Первый выход блока 15 памяти подключен к одним входам элементов И 16 и 17, второй выход блока 15 - к одним входам элементов И 18 и 19. Выход формирователя 13 подключен к другим входам элементов И 16 и 19, а выход Формирователя 14 - к другим входам элементов И 17 и 18. Выходы элементов И 16 и 18 подключены к входам элемента ИЛИ 20, выход . которого является первым выходом блока 10 коррекции, а выходы элементов И 17 и 19 подключены к входам элемента ИЛИ 21, который является вторым выходом блока 10 коррекции, 1246374Преобразователь работает следующим образом.В блоке 1 входные синусна-касинусные сигналы преобразуются в прямоугольные мнагофазные сигналы, число которых определяется принятой дискретностью преобразователя, В дешифратаре 2 мнагофазные сигналы преобразуются в последовательности неперекрывающихся импульсов, которые поступают на входы блоков 4 и 5 элементов И и на информационные входы регистра 3.В любой момент времени сигнал на выходе дешифратора 2 представляет 5 собой "1" на одном из выходов и "0" на всех остальных выходах. Па сигналу с формирователя 9 состояние де- шифратора 2 запоминается в регистре 3. Коды дешифратора 2 и регистра 20 3 сравниваются в блоках 4 и 5. При равенстве выходных кодов дешифратора 2 и регистра 3 все выходы блоков 4 и 5 находятся в нулевом состоянии. При изменении входной величины в 25 одну сторону выходной код дешифратара 2 последовательна принимает значения, например, 1000, 0100, 0010При каждбм изменении выходного щ кода дешифратора 2 происходит совпадение на одном из элементов И блока 4 единицы кода предыдущего значения с регистра 3 с единицей хода текущего значения с дешифратора. 2. Единичный сигнал с выхода блока 4 через элементы ИЛИ 6 и 11 проходит на вход сложения реверсивного счетчика 8 и через формирователь 9, представляющий собой элемент ИЛИ и элемент задержки, пос тупает на управляющий вход регистра 3. По сигналу с формирователя 9 в регистре 3 происходит перезапись выходного кода дешифратора 2, после чего выходные коды дешифратора 2 и регистра 3 становятся равными. Выходы блока 4 возвращаются в нулевое состояние до следующего изменения входной величины в ту же сторону,При изменении входной величины в 50 другую сторону выходной код дешифратара 2 принимает значения, напри.мер, 1000, 0001, 0010,0100 и т.д.При каждом изменении выходного кода дешифратора 2 происходит совпадение 55 на одном из элементов И блока 5 еди-ницы кода предыдущего значения с регистра 3 с единицей кода текущего значения с дешифратора 2. Единичный сигнал с выхода блока 5 через элементы ИЛИ 7 и 12 проходит на вход вычитания реверсивного счетчика 8 и через формирователь 9 на управляющий вход регистра 3 для перезаписи выходного кода дешифратора 2. Выходы 5 возвращаются в нулевое состояние до следующего изменения входной величины. Выходной код преобразователя формируется в реверсивном счетчике 8Выходной код счетчика 8 для форми-: рования в. заданных точках единичных сигналов коррекции поступает на пер-. вые входы блока 16 коррекции. Единичные сигналы с блоков 4 и 5 через элементы ИЛИ б и 7 соответственно поступают на первый и второй входы блока 10 коррекции, с которого в промежутках между единичными сигналами с блоков 4 и 5 поступают единичные сигналы коррекции через элементы ИЛИ 11 и 12 на соответствующие входы реверсивного счетчика 8.В каждой ячейке блока 15 записан код коррекции 10 либо 01, либо 00. Это значит, что, когда код реверсивного счетчика примет значение, соответствующее адресу ячейки, в которой записан, например код 10, то при этом значении входной величины и росте ее в счетчик 8 необходимо внести коррекцию +1, при убывании входной величины необходимо внести коррекцию -1. Если код в ячейке равен 01, то при возрастании входной величины в счетчик необходимо внести коррекцию -1, а при убывании + 1. Код 00 означает отсутствие коррекции в данной точке.На адресные шины блока 15 младшие разряды реверсивного счетчика 8 могут не подаваться. Число этих разрядов определяется минимальной длиной участ- . ка, на котором требуется единичное значение коррекции.С помощью элементов И 16-19 код коррекции, записанный в ячейке блока 15, передается на суммирующий ипи вычитающий вход реверсивного счетчика 8 в зависимости от направления изменения входной величины.Формирователи 13 и 14 импульсов вырабатывают после каждого из импульсов, поступающих с элементов ИЛИ 6и 7, импульсы коррекции. В нетактированной системе эти импульсы формируются по срезу импульсов с элементов 6 и 7 с некоторой146374 счетчика. Фиг 2 аказ 4022/56 Подписно аж олигр. пр-тие, г. Ужгород, ул. Проектная, 4 ро задержкой. В системе с двумя последовательностями тактовых импульсов,сдвигуть.х на 180 один относительно,другого, импульсы с элементов 6 и 7формируются по первой, а с формирователей 13 и 14 по второй последовательности импульсов с тем, чтобыимпульсы коррекции поступали на счетчик 8 в промежутках между основнымиимпульсами, 1 ОВ преобразователях, в которыхначало отсчета может устанавливатьсяпроизвольно, блок коррекции долженвключать в себя дополнительный счетчик, выходы которого подаются на 15адресные входы блока 15 памяти, в. который в начале работы должно заноситься истинное (абсолютное) значениевходной величины,Если.на адресные входы счетчика 8 20подавать сигнал о направлении изменения входной величины, то при одноми том же значении входной величины. ей можно придать различное значениекоррекции в зависимости от направления изменения входной величины, компенсируя таким образом гистерезис.Таким образом, сличив перед началомработы преобразователя значения кодавХодной величины с ее истинным зна- ЗОчением на всем диапазоне изменениявходной величины, можно занести всоответствующие ячейки блока памятиединичные коррекции, что увеличиваетточность преобразователя. формула из об ре те ния 1. Преобразователь синусно-косинус 1ных сигналов в код по авт.св.Р 1094043, отличающийсятем, что, с целью повышения точностипреобразователя, в него введены блоккоррекции, третий и четвертый элементы ИЛИ выходы первого и второго элементов ИЛИ подключены к одним входамтретьего и четвертого элементов ИЛИи к первому и второму входам блокакоррекции, группа входов которогосоединена с выходами разрядов реверсивногоо счетчика, а первый и второйвыходы блока коррекции подключенык другим входам соответственно третьего и четвертого элементов ИЛИ,выходы которых подключены к входамсложения и вычитания реверсивного 2, Преобразователь по и, 1, о тл и ч а ю щ и й с я тем, что блок коррекции содержит первый и второй формирователи импульсов, блок памяти, первый, второй, третий и четвертый элементы И и первый и второй элементы ИЛИ, входы первого и второго формирователей импульсов являются первым и вторым входами блока коррекции, а входы блока памяти являются группой входов блока коррекции, первый выход блока памяти подключен к одним входам первого и второго элементов И, второй выход блока памяти подключен к одним входам третьего и четвертого элементов И, выход первого формирователя импульсов подключен к другим входам первого и четвертого элементов И, выход второго формирователя импульсов подключен к другим входам второго и третьего элементов И, выходы первого и третьего элементов И подключены к входам первого элемента ИЛИ, выход которого является первым выходом блока коррекции, а выходы второго и четвертого элементов И подключены к входам второго элемента ИЛИ, выход которого является вторым выходом блока коррекции.

СмотретьЗаявка

3841285, 10.01.1985

ПРЕДПРИЯТИЕ ПЯ Р-6495

БАБЕР АЛЕКСАНДР ИОСИФОВИЧ, КОЛЕСНИК ЭДУАРД МИРОНОВИЧ, СЕЛЯНТЬЕВ АЛЕКСЕЙ ГЕОРГИЕВИЧ

МПК / Метки

МПК: H03M 1/30

Метки: код, сигналов, синусно-косинусных

Опубликовано: 23.07.1986

Код ссылки

<a href="https://patents.su/4-1246374-preobrazovatel-sinusno-kosinusnykh-signalov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь синусно-косинусных сигналов в код</a>

Предыдущий патент: Преобразователь угла поворота вала в код

Следующий патент: Многоканальное измерительное устройство

Случайный патент: Щелевой фильтр для жидкости