Интегральный формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

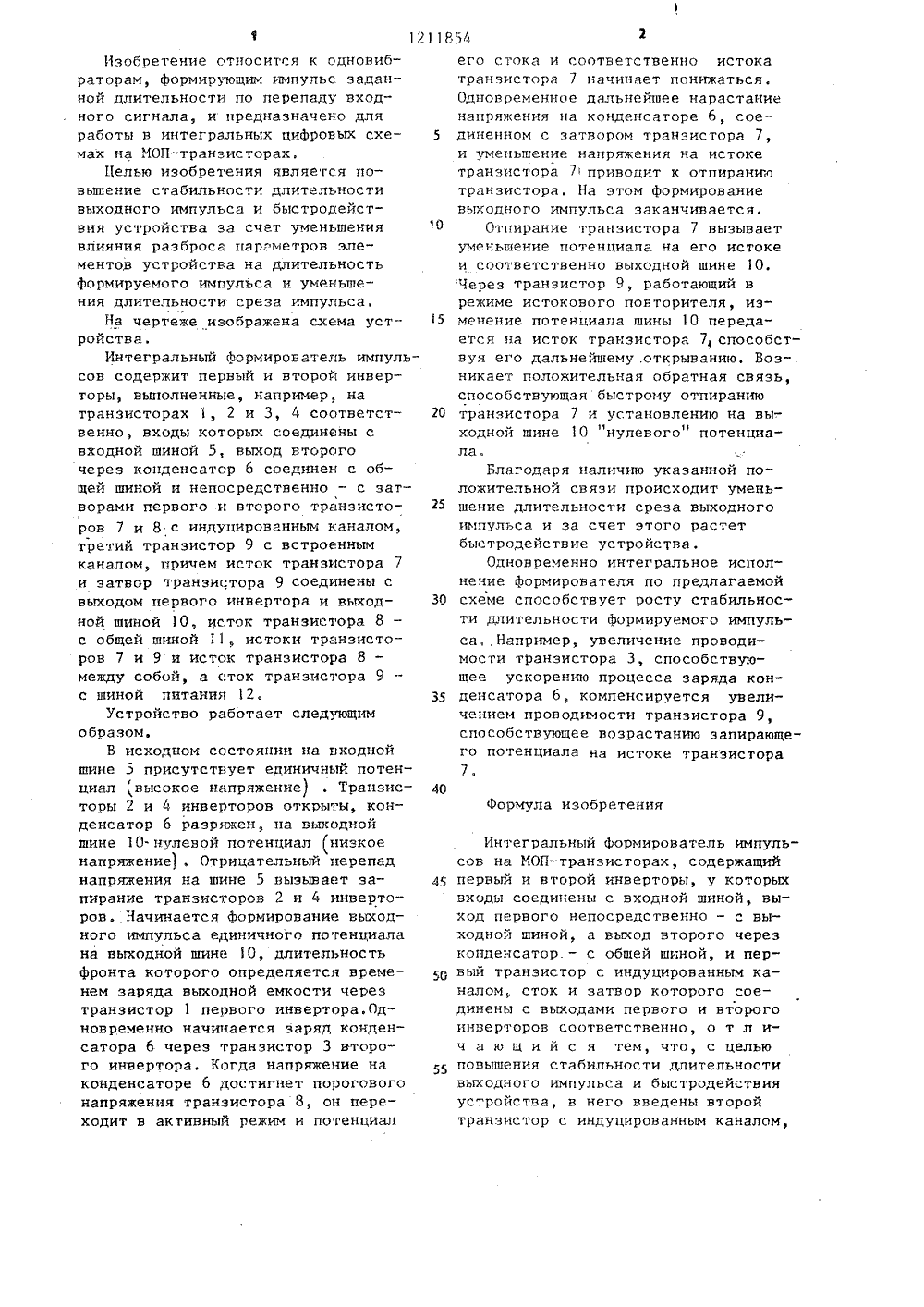

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ПИСАНИЕ ИЗОБРЕТАВТОРСКОМУ СВИДЕТЕЛЬСТВУ Попов ы прямоу-элементах. -102,ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Волков С, Генеоатор гольных. импульсов на МОП М.: Энергоиздат, 1981, с рнс. 3.28.Микросхема К 1809 РУ 1 бК 0.348.727-02 ТУ.(54) ИНТЕГРАЛЬНЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ(57) Изобретение относится к одновибраторам, формирующим импульс заданной длительности по перепаду входного сигнала, и предназначено для работы в интегральных цифровых схемах на МОП-транзисторах. Устройство содержит два инвертора, выполненных, например, на транзисторах 1, 2 и 3, 4 соответственно,входную шину 5, конденсатор 6, транзисторы 7 и 8 с индуцированным каналом, транзистор 9 с встроенным каналом, выходную шину 10 и общую шину 11. Введение транзистора 8 синдуцированным каналом и транзистора 9 с встроенным каналом позволяетповысить стабильность длительностивыходного импульса и быстродействиеустройства за счет уменьшения влияния разброса параметров элементовустройства на длительность формируемого импульса и уменьшить длительность среза импульса. 1 ил.Изобретение относится к одновибраторам, формирующим импульс заданной длительности по перепаду входного сигнала, и предназначено дляработы в интегральных цифровых схемах на МОП-транзисторах.Целью изобретения является повышение стабильности длительностивыходного импульса и быстродействия устройства за счет уменьшениявлияния разброса параметров элементов устройства на длительностьформируемого импульса и уменьшения длительности среза импульса.На чертеже изображена схема устройства.Интегральный формирователь импульсов содержит первый и второй инверторы, выполненные, например, натранзисторах 1, 2 и 3, 4 соответственно, входы которых соединены свходной шиной 5, выход второгочерез конденсатор 6 соединен с общей шиной и непосредственно - с затворами первого и второго транзисторов 7 и 8 с индуцированным каналом,третий транзистор 9 с встроеннымканалом, причем исток транзистора 7и затвор транзистора 9 соединены свыходом первого инвертора и выходной шиной 10, исток транзистора 8 -с общей шиной 11, истоки транзисторов 7 и 9 и исток транзистора 8 -между собой, а сток транзистора 9с шиной питания 12,Устройство работает следующимобразом.В исходном состоянии на входнойшине 5 присутствует единичный потенциал высокое напряжение) . Транзисторы 2 и ч инверторов открыты, конденсатор 6 разряжен, на выходнойшине 10- нулевой потенциал (низкоенапряжение) . Отрицательный перепаднапряжения на шине 5 вызывает запирание транзисторов 2 и 4 инверторов. Начинается формирование выходного импульса единичного потенциалана выходной шине 10, длительностьфронта которого определяется временем заряда выходной емкости черезтранзистор 1 первого инвертора,Одновременно начинается заряд конденсатора 6 через транзистор 3 второго инвертора. Когда напряжение наконденсаторе 6 достигнет пороговогонапряжения транзистора 8, он переходит в активный режим и потенциал.11 Р 5.его стока и соответственно истокатранзистора 7 начинает понижаться,Одновременное дальнейшее нарастаниенапряжения на конденсаторе 6, сое диненном с затвором транзистора 7,и уменьшение напряжения на истокетранзистора 7 приводит к отпираниютранзистора. На этом формированиевыходного импульса заканчивается.Отпирание транзистора 7 вызываетуменьшение потенциала на его истокеи соответственно выходной шине 10,Через транзистор 9, работающий врежиме истокового повторителя, из менение потенциала шины 10 передается на исток транзистора 7 способствуя его дальнейшему .открыванию. Возникает положительная обратная связь,способствующая быстрому отпиранию 20 транзистора 7 и установлению на вы-.ходной шине 1 О "нулевого" потенциала.Благодаря наличию указанной положительной связи происходит умень 25 шение длительности среза выходногоимпульса и за счет этого растетбыстродействие устройства,Одновременно интегральное исполнение формирователя по предлагаемой30 схеме способствует росту стабильности длительности формируемого импульсаНапример, увеличение проводимости транзистора 3, способствующее ускорению процесса заряда конЗ 5 денсатора 6, компенсируется увеличением проводимости транзистора 9,способствующее возрастанию запирающего потенциала на истоке транзистора7.4 ОФормула изобретения Интегральный формирователь импульсов на ИОП-транзисторах, содержащий первый и второй инверторы, у которых входы соединены с входной шиной, выход первого непосредственно - с выходной шиной, а выход второго через конденсатор. - с общей шиной, и пер вый транзистор с индуцированным каналом сток и затвор которого соединены с выходами первого и второго инверторов соответственно, о т л ич а ю щ и й с я тем, что, с целью 55 повышения стабильности длительностивыходного импульса и быстродействия устройства, в него введены второй транзистор с индуцированным каналом,УСоставитель С.Агеев Редактор Л.Авраменко Техред О.Ващишина Корректор Г.Решетник Заказ 649/59 Тираж 818 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д.4/5ГФилиал ППП "Патент", г.Ужгород, ул,Проектная,4 затвор и сток которого соединены сзатвором и истоком первого транзистора соответственно, а исток - собщей шиной, и третий транзистор с 1211854 4встроенным каналом, затвор и исток которого соединены со стоком и истоком первого транзистора соответственно, а сток - с шиной питания.

СмотретьЗаявка

3769276, 05.07.1984

ОРГАНИЗАЦИЯ ПЯ Х-5263

СВЕРДЛОВ АЛЬФРЕД САМУИЛОВИЧ, ПОПОВА РЕВЕККА ЯКОВЛЕВНА

МПК / Метки

МПК: H03K 3/284, H03K 3/353

Метки: импульсов, интегральный, формирователь

Опубликовано: 15.02.1986

Код ссылки

<a href="https://patents.su/3-1211854-integralnyjj-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Интегральный формирователь импульсов</a>

Предыдущий патент: Сглаживающий фильтр

Следующий патент: Многостабильный триггер богдановича

Случайный патент: Способ работы системы подогрева воздуха