Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1195364

Авторы: Дычаковский, Кузнецов, Ланнэ, Осокин, Страутманис, Титов

Текст

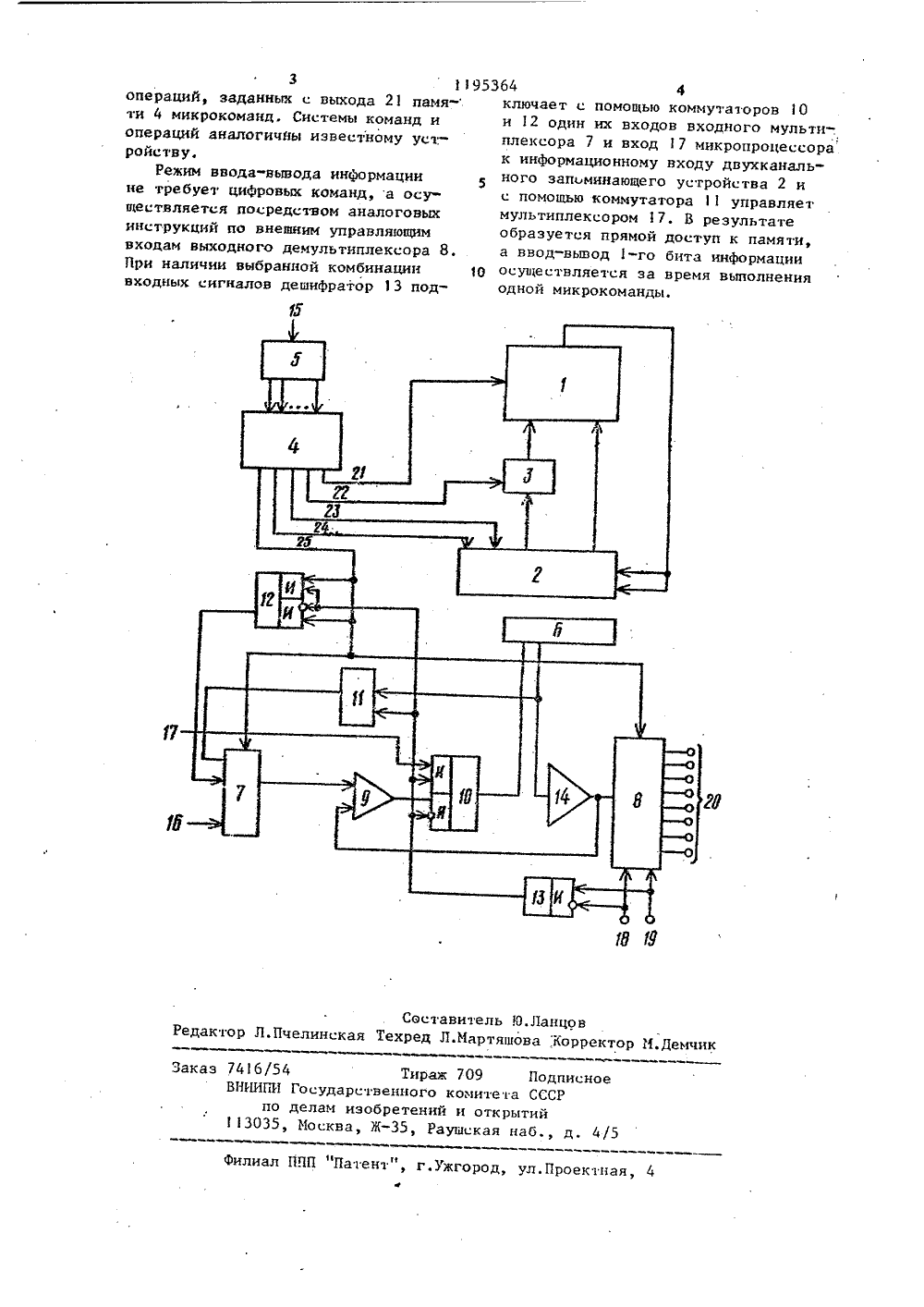

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) Ш) С 061/00 С 06 Е 15 0 ПИСАНИЕ ИЗОБРЕТЕНИЯ адресные выходы ко соответственно с п рого соединенывым и вторым СССР198 С,осе 5 зоггр.,ГОСУДАРСТВЕННЫИ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ ОРСКОМУ СВИДЕТЕЛЬСТ(56) Авторское свидетельство Р 976447, кл. 6 06 Г 15/00,ТЬе 2920 апа 1 оц з 19 па рг дезз 1 п 9 Ьапс ЬооЕ. - пе со ОБА, Г 19. 3-1. 1980.(54)(57) ЖКРОПРОЦЕССОР, содержащийарифметико-логическое устройство,двухканальное оперативное запоминающее устройство с произвольной выборкой, блок регистров обмена, масштабируощий блок, блок памяти микрокоманд, счетчик команд, входной мультиплексор,выходной демультиплексор,цифроаналогоный преобразователь и компаратор,причем синхровход микропроцесссора подключен к счетному входу счетчика команд, группа выходов которого соединена с группой адресных входовблока памяти микрокоманд, выход кодамикрооперации которого соединенс входом кода операции арифметикологического устройства, первый ивторой информационные входы которогосоединены соответственно с выходоммасштабирующего блока и с первымвыходом двухканального оперативногозапоминающего устройства с произвольной выборкой, второй выход которого соединен с информационным вхо-.дом масштабирующего блока, управляющий вход которого соединен с выходом.управления масштабированием блокапамяти микрокоманд, первый и второй адресными входами двухканальногооперативного запоминающего устройствс произвольной выборкой, первый ивторой информационные входы которогосоединены с выходом арифметико-логического устройс 1 ва, информационныйвход аналоговых сигналов микропроцессора подключен к информационномувходу входного мультиплексора, первый упранляюцнй вход которого соединен с первым управляющим входомвыходного демультиплексора и выходомполя управления вводом-выводом инФормации блока памяти микрокоманд,выход входного мультиплексора соединен с первым входом компаратора,второй вход которого соединенс выходом цифроаналогового преобразователя и информационным входомвыходного демультиплексора, выходыкоторого являются выходами микропроцессора, выход признака обменаблока памяти микрокоманд соединенс адресным входом блока регистровобмена, выход которого соединенс входом цифроаналогового преобразователя, о т л и ч а ю щ и й с ятем, что, с целью расширения функциональных возможностей путем реализации режима обработки, помимоаналоговых, цифровых сигналов, ондополнительно содержит дешифраторрежима и три коммутатора, причемпервый и второй информационные входьпервого коммутатора соединены ссоответствующими разрядами выходаполя управления вводом-выводоминформации блока памяти микрокоманд,управляющие входы первого, второго1 ,и третьего коммутаторов соединены с выходом дешифратора режима, первый и второй входы которого соеди.нены соответственно с вторым и третьим управляющими входами выходного демультиплексора и являются соответственно первым и вторым входами управления вводом-выводом информации микропроцессора, выход ,блока регистров обмена соединен с, информационным входом второго коммутатора, выход которого соединен 195364с вторым управляющим входом входного мультиплексора, третий управляющий вход которого соединен с выходом первого коммутатора, информационный вход цифровых сигналовмикропроцессора подключен к первомуинформационному входу третьего коммутатора, второй информационныйвход которого соединен с выходомкомпаратора, выход третьего коммутатора соединен с информационнымвходом блока регистров обмена.Изобретение относится к вычислительной технике, в частности к устройствам для цифровой обработки аналоговых и цифровых сигналов.Цель изобретения - расширение функциональных возможностей путем реализации режима обработки, помимо аналоговых цифровых сигналов.На чертеже приведена схема предлагаемого. микропроцессора.Микропроцессор содержит арифметико-логическое устройство 1, двухканальное оперативное запоминающее устройство 2, масштабирующий блок 3, память 4 микрокоманд, счетчик 5 команд, блок регистров б обмена, входной мулыиплектор 7, выходной демультиплексор 8, компаратор 9, третий 10, второй 11 и первый 12 коммутаторы, дешифратор 13 режима, цифроаналоговый преобразователь 14, синхровход 15, информационный вход 6 аналоговых сигналов, информационный вход 17 цифровых сигналов, первый 18 и второй 19 входы управления вводом-выводом информации, выходы 20, выход 21 кода операции памяти микрокоманд выход 22 управления1масштабированием памяти микрокоманд, первый 23 и второй 24 адресные выходы памяти микрокоманд и выход 25 поля управления вводом-выводом инФормации памяти микрокоманд. Микропроцессор работает следующим образом.Предварительно в память 4 микрокоманд записывают программу. Память 4 микрокоманд управляется от счетчика 5 команд внутренним или внешнимтактовым сигналом.Основной тактовый сигнал разделяется на несколько сдвинутых по 5 фазе тактовых сигналов для внутренней синхронизации микропроцессора.Счетчик 5 команд при этом обеспечивает повышение на один счет командпри четырех циклах основного тактового сигнала и считает дальше дотех пор, пока пе достигнет численного значения, равного емкости памяти4, поскольку он не перемещаетсяобратно командой "Конец программы" 1 или сигналом возврата. Во время работы микропроцессорасчетчик 5 команд последовательнообращается к каждой из микрокоманд.20 Переходы в программе в данном случаене находят применения.По сигналам с соответствующихвыходов памяти 4 считываются операнды из двухканального запоминающего 25 устройства 2 и передают их непосредственно или через масштабирующийблок 3 в арифметико-логическое устройствоЯчейки памяти в двухканальномзапоминающем устройстве 2 могутодновременно адресоваться для передачи как по первому, так и по второму выходам. Это позволяет осуществдять подвод различных операндовиз одного запоминающего устройствабез двух раздельных адресных циклов.Над поступившими операндами А и Варифметико-логическое устройствопроизводит некоторое число известныхСоставитель Ю.ЛанцовРедактор Л.Пчелинская Техред Л.Иартяшова Корректор И.Демчи аказ 741 б/54 Тираж 709 Подписное ВНИИА Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Филиал ППП "Патент", г.ужгород, ул.Проектная,з 1операций, заданных с выхода 21 памяти 4 микрокоманд. Системы команд иопераций аналогичны известному усч-,ройству,Режим ввода-вывода информациине требует цифровых команд, а осуществляется посредством аналоговыхинструкций по внешним управляющимвходам выходного демультиплексора 8.При наличии выбранной комбинациивходных сигналов дешифратор 13 под 1953 б 4 4ключает с помощью коммун а 1 оров 1 Ои 12 один их входов входного мультиплексора 7 и вход 17 микропроцессорак информационному входу двухканального запоминающего устройства 2 ис помощью коммутатора 1 управляетмультиплексором 17. В результатеобразуется прямой доступ к памяти,а ввод-вывод 1-го бита информации 1 О осуществляется за время выполненияодной микрокоманды.

СмотретьЗаявка

3675701, 29.12.1983

ОРГАНИЗАЦИЯ ПЯ М-5222, ВОЕННАЯ АКАДЕМИЯ СВЯЗИ ИМ. С. М. БУДЕННОГО

ДЫЧАКОВСКИЙ ВИКТОР БРОНИСЛАВОВИЧ, КУЗНЕЦОВ АЛЕКСАНДР АНАТОЛЬЕВИЧ, ЛАННЭ АРТУР АБРАМОВИЧ, ОСОКИН ЮРИЙ ВАЛЕНТИНОВИЧ, СТРАУТМАНИС ГУНДАР ФРИЦЕВИЧ, ТИТОВ МИХАИЛ АРТЕМЬЕВИЧ

МПК / Метки

МПК: G06F 15/00, G06J 1/00

Метки: микропроцессор

Опубликовано: 30.11.1985

Код ссылки

<a href="https://patents.su/3-1195364-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Интегрирующее устройство

Следующий патент: Головка для записи информации на электрочувствительном носителе

Случайный патент: Преобразователь переменного напряжения в постоянное