Вычислитель разности квадратов двух чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

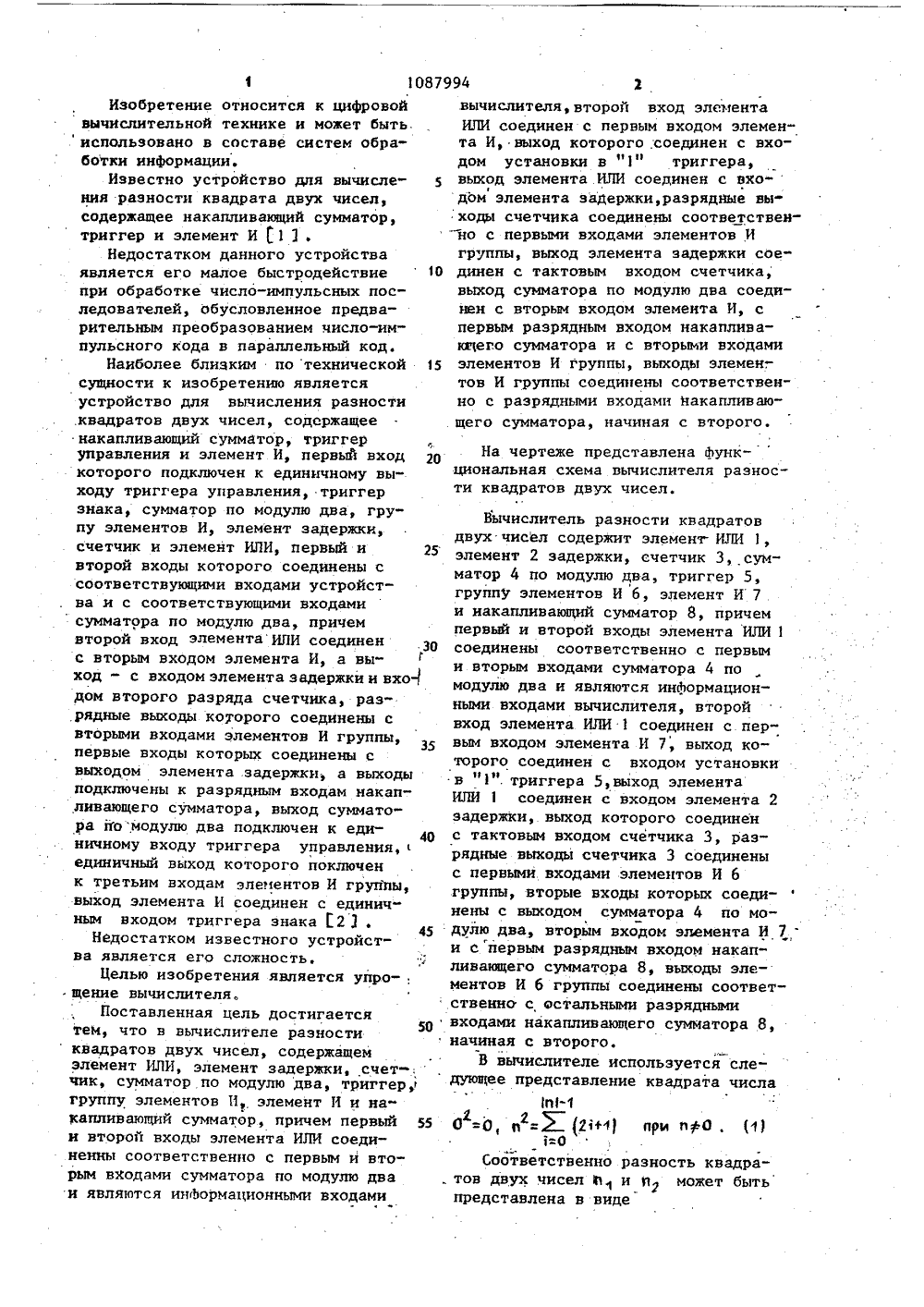

,рым Ф Вь ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТЮ ОПИСАНИЕ АВТОРСКОМУ(56) 1. Авторское свидетельство СССР9 430389, кл., С 06 Г 7/38, 1974,2, Авторское свидетельство СССРВ 780006, кл. С 06 Р 7/38, 1980(54)(57) ВЬЗЧИСЛИТЕЛЬ РАЗНОСТИ 1(ВАД-,РАТОВ ДВУХ ЧИСЕЛ, содержащий элемент ИЛИ, элемент задержки, счетчик,сумматор по модулю два, триггер,группу элементов И, элемент И и накапливающий сумматор, причем первыйи второй входы элемента ИЛИ соединен соответственно с первым и вто- .входами сумматора по.модулю два и являются информационными входами вычислителя, второй вход элемента ИЛИ соединен с первым входомэлемента Ивыход которого соединенс входом установки в "1" триггера,выход элемента ИЛИ соединен с входом элемента задержки, разрядныевходы счетчика соединены соответственно с первыми входами элементов Игруппы, отличающийсятем, что, с целью упрощения вычислителя, выход элемента задержки соединен с тактовым входом счетчика,выход сумматора по модулю два соединен с вторым входом элемента И, спервым разрядным входом накапливающего сумматора и с вторыми входамиэлементов И группы, выходы элементов И группы соединены соответственно с разрядными входами накапливающего сумматора, начиная с второгоИзобретение относится к цифровойвычислительной технике и может быть.использовано в составе систем обработки информации,Известно устройство для вычисления разности квадрата двух чисел,содержащее накапливающий сумматор,триггер и элемент И1 3 .Недостатком данного устройстваявляется его малое быстродействие1 Опри обработке число-импульсных последователей, обусловленное предварительным преобразованием число-импульсного кода в параллельный код.Наиболее близким по технической 15сущности к изобретению являетсяустройство для вычисления разности.квадратов двух чисел, содержащеенакапливающий сумматор, триггеруправления и элемент И, первый вход 2 Окоторого подключен к единичному выходу триггера управления, триггерзнака, сумматор по модулю два, групу элементов И, элемент задержки,счетчик и элемент ИЛИ, первый и 25второй входы которого соединены ссоответствующими входами устройства н с соответствующими входамисумматора по модулю два, причемвторой вход элемента ИЛЙ соединен 3 Ос вторым входом элемента И, а выход - с входом элемента задержки и вхо 4дом второго разряда счетчика, разрядные выходы которого соединены свторыми входами элементов И группы,35первые входы которых соединены свыходом элемента задержки, а выходыподключены к разрядным входам накапливающего сумматора, выход сумматора помодулю два подключен к единичному входу триггера управления,единичный выход которого поключенк третьим входам элементов И группы,выход элемента И соединен с единичным входом триггера знака 2145Недостатком известного устройства является его сложность,Целью изобретения является упро-,. щение вычислителя.Поставленная цель достигаетсятем, что в вычислителе разностиквадратов двух чисел, содержащемэлемент ИЛИ, элемент задержки, счет-,чик, сумматор по модулю два, триггер,группу элементов И, элемент И и наКапливающий сумматор, причем первый 55и второй входы элемента ИЛИ соеди.ненны соответственно с первым и вторым входами сумматора по модулю дваи являются информационными входами.вычислителя, второй вход элемента ИЛИ соединен с первым входом элемента И, выход которого, соединен с вхо- дом установки в "1" триггера, выход элемента.ИЛИ соединен с вхо-дом элемента задержки, разрядные выходы счетчика соединены соответственно с первыми входами элементов И группы, выход элемента задержки сое" динен с тактовым входом счетчика, выход сумматора по модулю два соединен с вторым входом элемента И, с первым разрядным входом накапливака 1 его сумматора и с вторыми входами элементов И группы, выходы элемен-, тов И группы соединены соответственно с разрядными входами накапливающего сумматора, начиная с второго.На чертеже представлена Функциональная схема вычислителя разности квадратов двух чисел.Вычислитель разности квадратов двух чисел содержит элемент ИЛИ элемент 2 задержки, счетчик 3, сумматор 4 по модулю два, триггер 5, группу элементов И б, элемент И 7 и накапливающий сумматор 8, причем первый и второй входы элемента ИЛИ 1 соединены соответственно с первым и вторым входами сумматора 4 по модулю два и являются информационными входами вычислителя, второй вход элемента ИЛИ 1 соединен с первым входом элемента И 7, выход которого соединен с входом установки в "1". триггера 5,выход элемента ИЛИ 1 соединен с вхоцом элемента 2 задержки, выход которого соединен с тактовым входом счетчика 3, разрядные выходы счетчика 3 соединены с первыми входами элементов И 6 группы, вторые входы которых соеди- ф иены с выходом сумматора 4 по модулю два, вторым входом элемента И 7и с первым разрядным входом накапливающего сумматора 8, выходы элементов И б группы соединены соответственио с остальными разряднымивходамн накапливающего сумматора 8,начиная с второго. В вычислителе используется следующее представление квадрата числа1 п 1-1О =О, Р= Е (21+1) при п 1 ьО, (1)2 21=0Соответственно разность квадра". тов двух чисел 61 и п может бытьпредставлена в виде(япри п 1 Чп ,гб 3В исхоцном состоянии сцетчик 3, триггер 5 и накапливающий сумма-, тор 8 установлены в "0". ОНеобходимым условием нормальной работы вычислителя является синхронность импульсов па обоих входах (эти импульсы могут Формироватьсяодним и тем же генератором 1.При поступлении импульсов на оба входа элемента ИЛИ 1 на его выходе вследствие синхронности входных импульсов ) Формируется один импульс. Импульс на выходе сумматора 4 по 2 О модулю два формируется только в том случае, когда импульс поступает на один из его входов, если же импульсы на входах отсутствуют или появляются на обоих входах одновременно, выходной импульс не возникает (сумматор 4 по модулю два представляет собой в данном случае импульсный элемент неравнозначности 1Числа о 1 и и начинают Формиро- ЗО2ваться на входах вычислителя одновременно. Пусть о 7 пПри этом первые й импульсов бу,- дут поданы синхронно на оба входа вычислителя, На выходе сумматора 4 з 5по модулю два импульсы в этом режиме не возникают, т.е. триггер 5 и накапливающий сумматор 8 остается в исходном нулевом состоянии. Каждыйже импульс с выхода элемента 40 ИЛИ 1, проходя через элемент 2 за-" держки, увеличивает содержимое счет"чика 3 на единицу. Следующий (и +1)-й входной импульс подаетсятолько на вход и устройства. При 45 этом одновременно с ним возникаетимпульс на выходе сумматора 4 по модулю два, этот импульс не из/Уменяя, состояния триггера 5 (так как отсутствует импульс, на втором входе элемента И 7 ) , вызываетприбавление к содержимому накапливающего сумматора 8 числа 2 н 2+1,Действительно, в это время насчетчике 3 зафиксировано число п .1,последний входной импульс ещеВНИИПИ Заказ 2674461 филиал ППП Патент г.УФ 4не достиг счетчика 3 через элемент 2 задержки 1 причем разрядные выходы счетчика 3 соединены с разрядными входами накапливающего сумматора 8 через элементы И 6 группы со сдвигом на один разряд в сторону старших разрядов, а единица в первый (младщий ) разряд накапли" вающего сумматора 8 поступает не-,посредственно с выхода сумматора 4по модулю два.Время задержки элемента 2 выбирается достаточным для завершенияпередачи содержимого счетчика черезэлементы И 6 группы, но меньшим интервала между входными импульсами.С приходом последнего11 -го;входного импульса содержимое накапливающего сУмматора 8 увеличивается,аналогично описанному на 2(п)+1,т,е, результат вычислений форми. руется в соответствии с формулой (2).Если .п 1о , то вычислительработает точно так же при обработкепервых П 1 импульсов, поступающих одновременно на, оба входа. Следующийимпульс поступает только на вход овычислителя, при этом импульсы возникают одновременно на обоих входахэлемента И 7, в результате чего триггер 5 перейдет в единичное, состоя:ние, индицируя этим отрицательный знакрезультата вычислений, в остальномработа вычислителя протекает совер,шенно аналогично раесмотреному случаю.Повышение быстродействия обусловлено тем, что в известном устройственечетное число, которое необходимо1,при поступлении очередного входногоимпульса только на один из входов,устройства ) прибавить к содержимому накапливающего сумматора, формируеся только после прихода этогоимпульса, в то время как в предлагаемом случае оно формируется заранее,в течение предыдущего такта, и припоступлении входного импульса остается лишь прибавить это числс.к предыдущему результату.Предлагаемый способ Формированияуказанных нечетных чисел и состоянийтриггера знака позволяет упроститьвычислитель, исключив из его состава триггер управления и один разрядсчетчика, а также соответствующийему элемент И 6 группы.Тираж 699 Подписноежгород, ул.Проектная, 4

СмотретьЗаявка

3534080, 30.11.1982

ХАРЬКОВСКИЙ ИНЖЕНЕРНО-СТРОИТЕЛЬНЫЙ ИНСТИТУТ

ДОБРЫДЕНЬ ВЛАДИМИР АЛЕКСАНДРОВИЧ, ФЕДОРОВ ВЛАДИМИР ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 7/62

Метки: вычислитель, двух, квадратов, разности, чисел

Опубликовано: 23.04.1984

Код ссылки

<a href="https://patents.su/3-1087994-vychislitel-raznosti-kvadratov-dvukh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Вычислитель разности квадратов двух чисел</a>

Предыдущий патент: Устройство для контроля генератора случайных чисел

Следующий патент: Устройство для вычисления разности число-импульсных кодов

Случайный патент: Катушка индуктивности