Аналоговое запоминающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1038967

Авторы: Вагнер, Сидоров, Шахтшнейдер

Текст

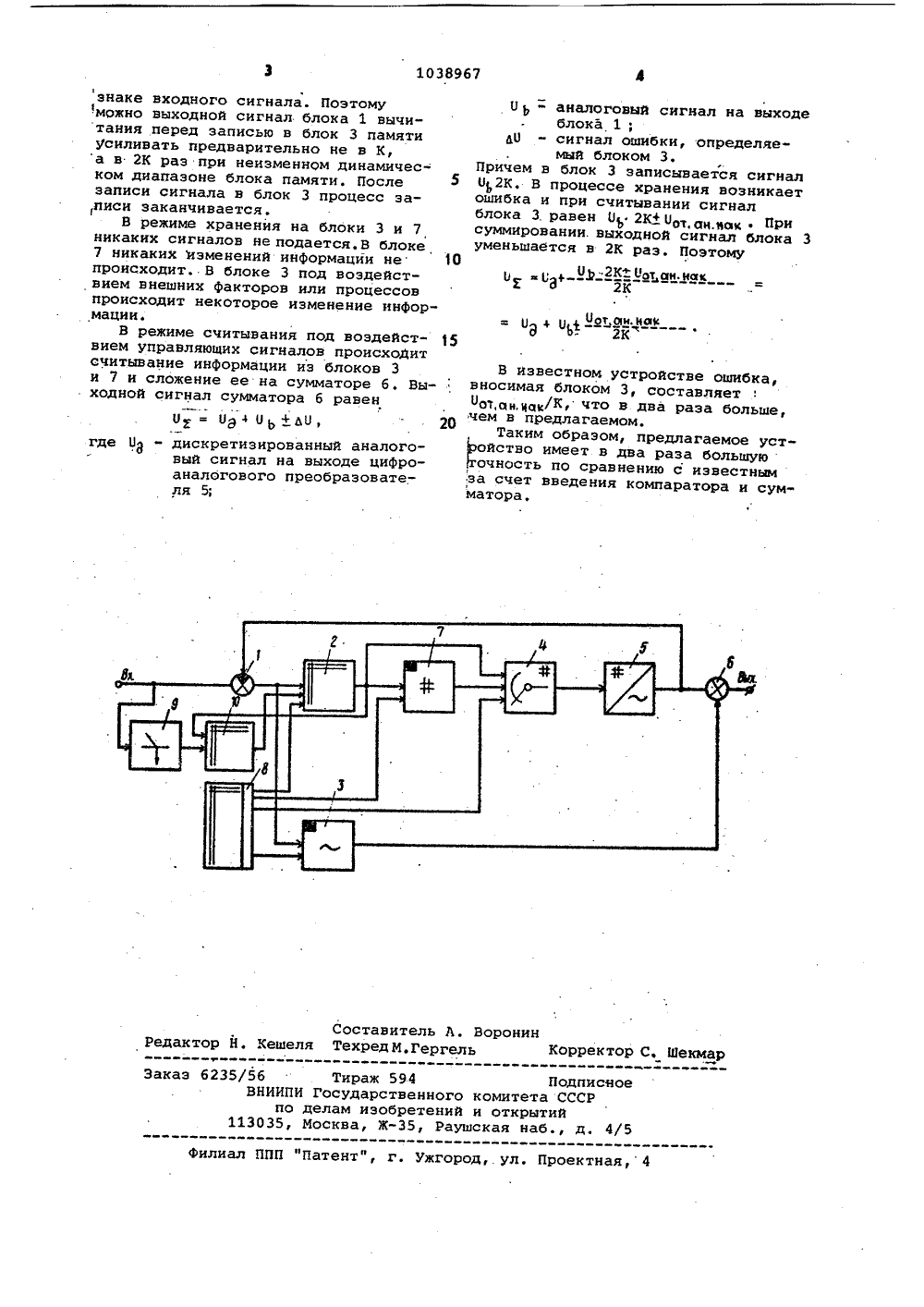

(Я 3 С 11 С 27/00 ПИСАНИЕ ИЗОБРЕТЕНИЯ идоров тротехничестельство СССР 7/00, 2303.8(прототип),ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦТИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Новосибирский элекий институт(54) (57) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕУСТРОЙСТВО по авт. св. 9 1003147,о т л и ч а ю ц е е с я тем, что,с целью повышения точности устройства, в него введены компаратор ивторой сумматор, выход которогосоединен с третьим входом блока формирования адреса, первый вход второго сумматора соединен с выходом компаратора, вход которого соединен спервым входом блока вычитания, второвход второго сумматора соединен свторым входом второго блока памяти.Изобретение относится к аналоговвычислительной технике и может бытьиспользовано для запоминания в уст.- ройствах обработки аналоговой информации, устройствах автоматики, измерительной и вычислительной техники.По основному авт. св. 9 1003147известно аналоговое запоминающееустройство, содержащее блок управления, блоки памяти, коммутатор,сумматор, цифро-аналоговый преобразователь блок формирования адресаи блок вычитания, вход которогосоединен с выходом цифро-аналоговогопреобразователя и входом сумматора,выход сумматора является выходомустройства, а второй вход подключенк выходу первого блока памяти, выход блока вычитания соединен с входами блока выбора адреса и первогоблока памяти, управляющие входы ко.торых подключены к выходам блока управления, выход. коммутатора соединен с входом цифро-аналогового преобразователя, входы коммутатора соединены с выходами второго блока памяти, блока управления и блока формирования адреса, второй вход блока вычитания является входом устройства 1 .Цель изобретения - повышениеточности устройства.Поставленная цель достигается тем, что в аналоговое запоминающее устройство введены компаратор и второй сумматор, выход которого соединен с третьим входом блока Формирования адреса, первый вход второго сумматора соединен с выходом компаратора, вход которого соединен с первым входом блока вычитания, второй вход второго сумматора соединен с вторым входом второго блока памятиНа чертеже приведена функциональная схема предлагаемого устройства.Устройство содержит блок 1 вы.читания, блок 2, первый блок 3 памяти, коммутатор 4, цифро-аналоговый преобразователь 5, сумматор 6, второй блок 7 памяти, блок 8 управления, компаратор 9, сумматор 10.Компаратор 9 принимает значение "0" или ф 1" на выходе в зависимости от знака входного сигнала. Можно использовать компараторы ИМС 252, 521, 597 или любые другие, отвечающие по порогу срабатывания и быстродей" ствию характеристикам ЗУ.Одним операндом для сумматора 10 является код, находящийся в блоке 7 памяти, а другим - единица в младшем разряде блока 2. Сумматор 10 может быть выполнен на интегральных схемах 176, 133, 155 серий.Устройство работает следующим образом.В режиме записи сигнал поступает на вход устройства и на вход компаой ратора 9, Аналого-циФровой преобразователь, образованный блоком 1,блоком 2, коммутатором 4 и цифроаналоговым преобразователем 5, дискретизирует входной сигнал. На выходе5 блока 2 находится цифровой эквивалент преобразований части входнбгосигнала, на выходе цифро-аналоговогопреобразователя 5 - дискретизированный аналоговый эквивалент. Аналого 10 цифровое преобразование по методупоразрядного уравновешивания обеспечивает аналоговый эквивалент по мо"дулю меньше входного сигнала. Поэтому на выходе блока 1 и, соответственно, на входе блока 3 будет положИтельная величина при положительномвходном сигнале и. отрицательнаяпри отрицательном, причем по модулюона превышает величину одной диск"реты аналого-циФрового преобразования, В случае применения при преобразовании метода последовательного приближения аналоговый эквивалент по модулю всегда больше входного сигнала и знак выходной величины блока 1 вычитания отрицательныйпри положительном сигнале и положительный при отрицательном.По окончании преобразования вблоке 2 находится код. На выходецифро-аналогового преобразователя 5присутствует аналоговое напряжение,соответствующее этому коду. При положительном входном сигнале код остается неизменным. При отрицательном35 входном сигнале код необходимо увеличить на величину младшего знача",щего разряда. Для этого напряжениес выхода блока 2 поступает на одиниз входов сумматора 10, на другой40 вход которого поступает выходноенапряжение с компаратора 9. При отрицательном входном напряжении всумматоре 10 происходит увеличениекода на величину младшего разряда.Это напряжение поступает на одиниз входов блока 2. При любом изэтих методов входной сигнал блока 3памяти является двухполярным. Введение компаратора 9 и сумматора 10позволяет после окончания аналогоцифрового преобразования корректировать код блока 2 и аналоговый эквивалент так, что сигнал на выходеблока 1 вычитания и на входе блока 3имеет одну полярность независимоот знака входного сигнала, Это достигается тем, что при входном сигнале одной полярности цифровой кодостается неизменным, а при сигналедругой полярности код увеличивается60 на младший значащий Разряд. В этомслучае аналоговый эквивалент по модулю больше входного сигнала приодной полярности его и меньше придругой. Сигнал на входе блока 3 па 65 мяти имеет одну полярность при любомСоставитель Л. ВоронинКешеля Техред М. Гергель Корректор С. Шекм дакт аказ 6235/56 Тираж 594 ВНИИПИ Государственногпо делам иэобретени 13035, Москва, Ж, Ра Подписикомитета СССРи открытийская наб., д. 4 иал ППП фПатент", г. Ужгород,. Ул. Проектназнаке входного сигнала. Поэтомуможно выходной сигнал блока 1 вычитания перед записью в блок 3 памятиусиливать предварительно не в К,а в 2 К раэ при неизменном динамическом диапазоне блока памяти. Послезаписи сигнала в блок 3 процесс за,писи заканчивается,В режиме хранения на блоки 3 и 7никаких сигналов не подается.В блоке7 никаких изменений информации не 10происходит. В блоке 3 под воздействием внешних факторов или процессовпроисходит некоторое изменение информации.В режиме считывания под воздействием управляюших сигналов происходитсчитывание информации из блоков 3и 7 и сложение ее на сумматоре 6, Выходной сигнал сумматора 6 равенО = Оаф ОЬфц 20где 08 " дискретизированный аналоговый сигнал на выходе цифроаналогового преобразователя 5; О" аналоговый сигнал на выходеблока 1;аО - сигнал ошибки, определяемый блоком 3,Причем в блок 3 записывается сигнал 02 К. В процессе хранения возникает ошибка и при считывании сигнал блока 3 равен О 2 Кф Опт цн вфлаПри суммировании выходной сйгнал блока 3 уменьшается в 2 К раз, ПоэтомуО ь "2 Хф Оот ан. нак2 К В известном устройстве ошибка,вносимая блоком 3, составляетОот,ан.нак/К, что в два раза больше,чем в предлагаемом.Таким образом, предлагаемое устойство имеет в два раза большуюочность по сравнению с известнымза счет введения компаратора и сумматора,

СмотретьЗаявка

3311178, 26.06.1981

НОВОСИБИРСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ

ВАГНЕР ИВАН ГЕОРГИЕВИЧ, СИДОРОВ ВЛАДИМИР МИХАЙЛОВИЧ, ШАХТШНЕЙДЕР ВЛАДИМИР ГЕНРИХОВИЧ

МПК / Метки

МПК: G11C 27/00

Метки: аналоговое, запоминающее

Опубликовано: 30.08.1983

Код ссылки

<a href="https://patents.su/3-1038967-analogovoe-zapominayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговое запоминающее устройство</a>

Предыдущий патент: Способ продвижения решетки цилиндрических магнитных доменов

Следующий патент: Устройство для управления памятью

Случайный патент: Устройство для поверки и подгонки