Мультимикропроцессорная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

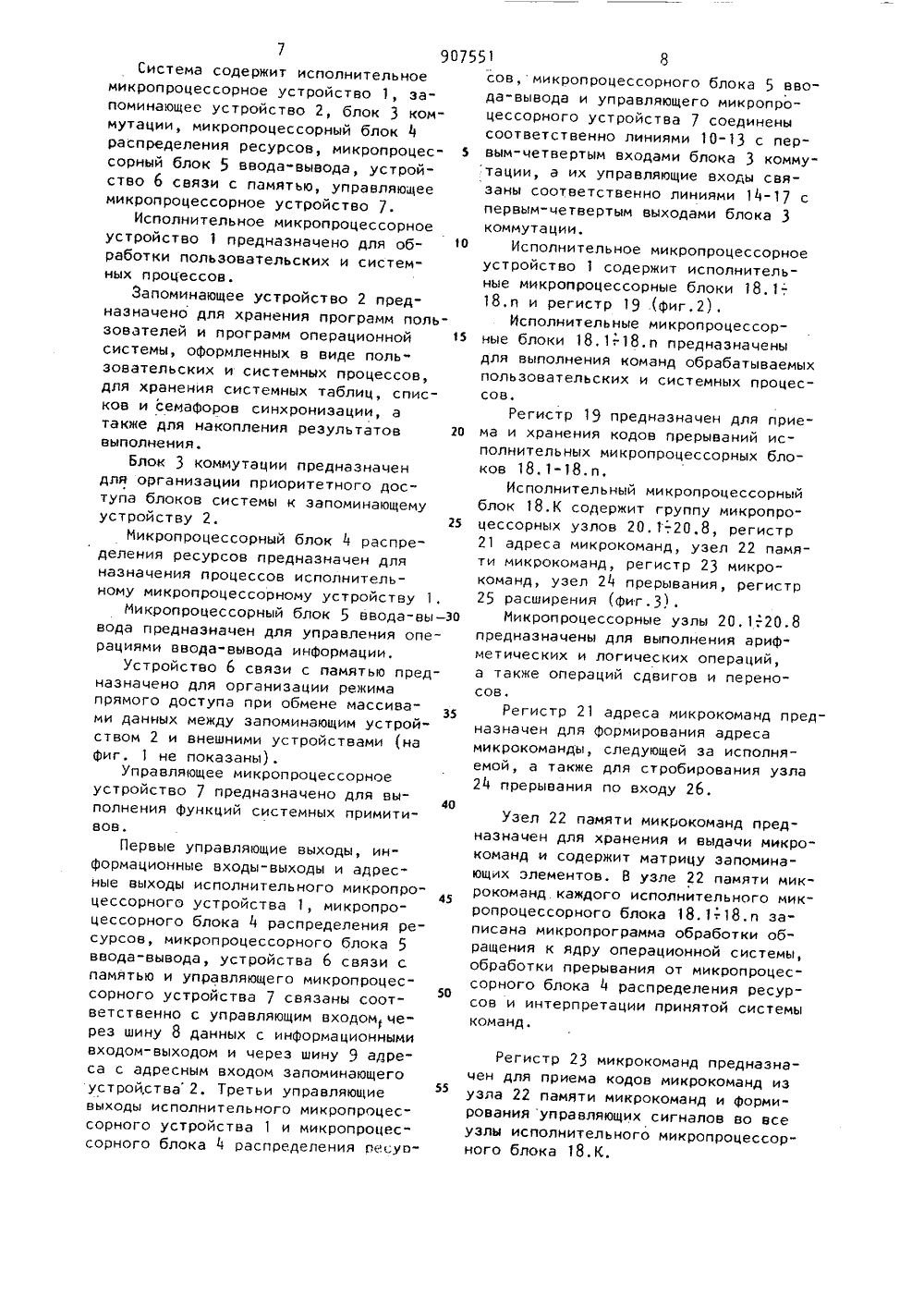

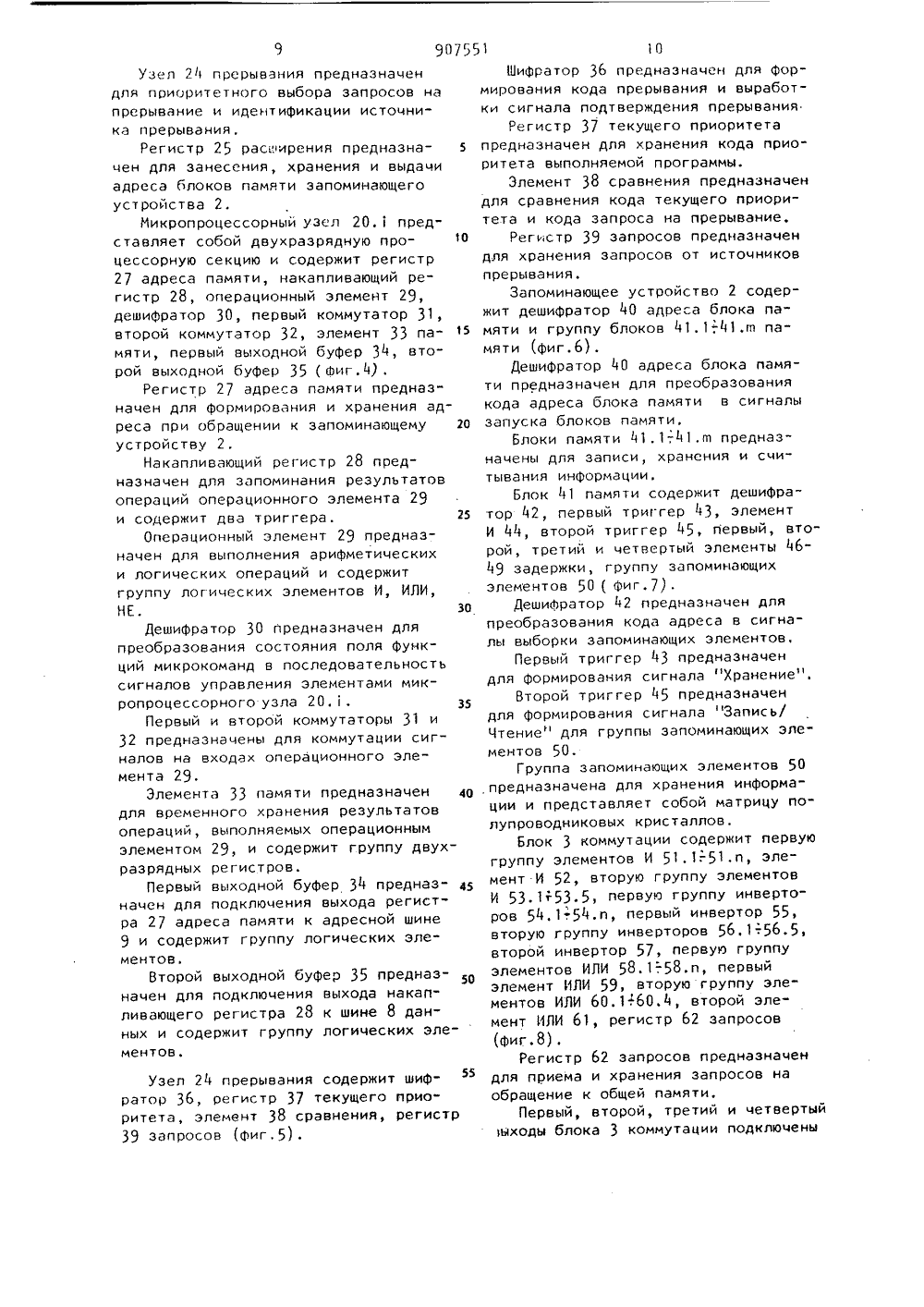

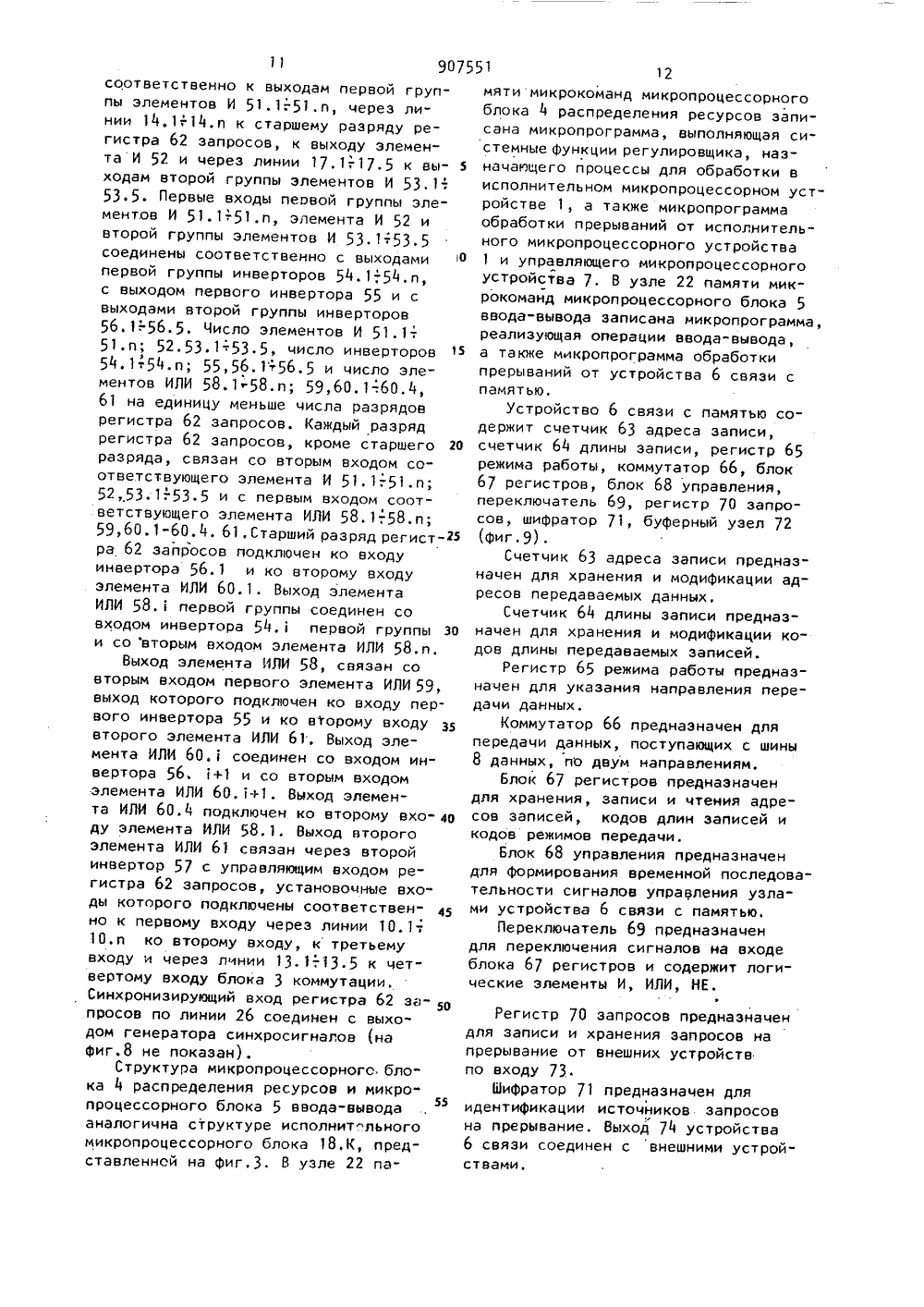

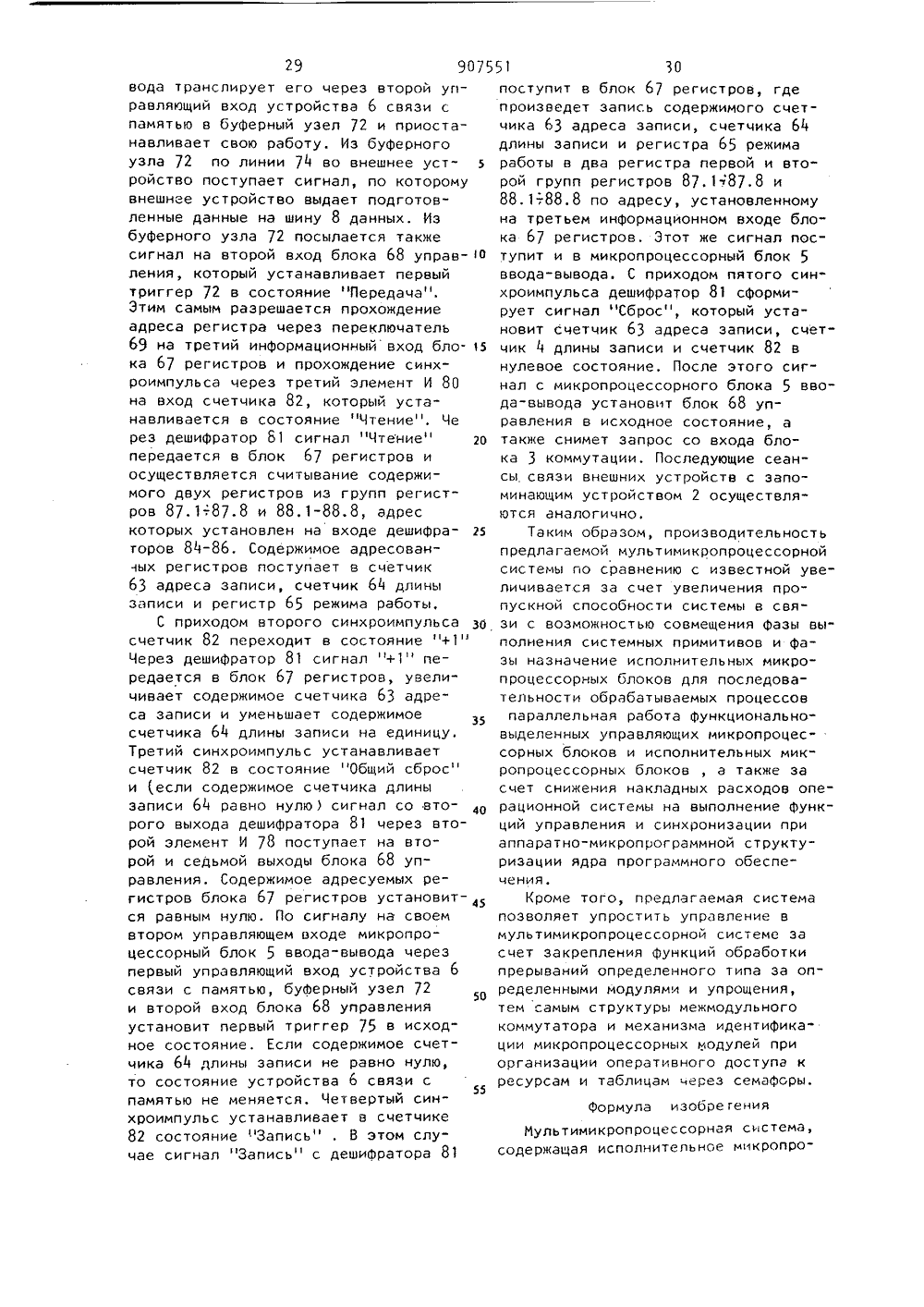

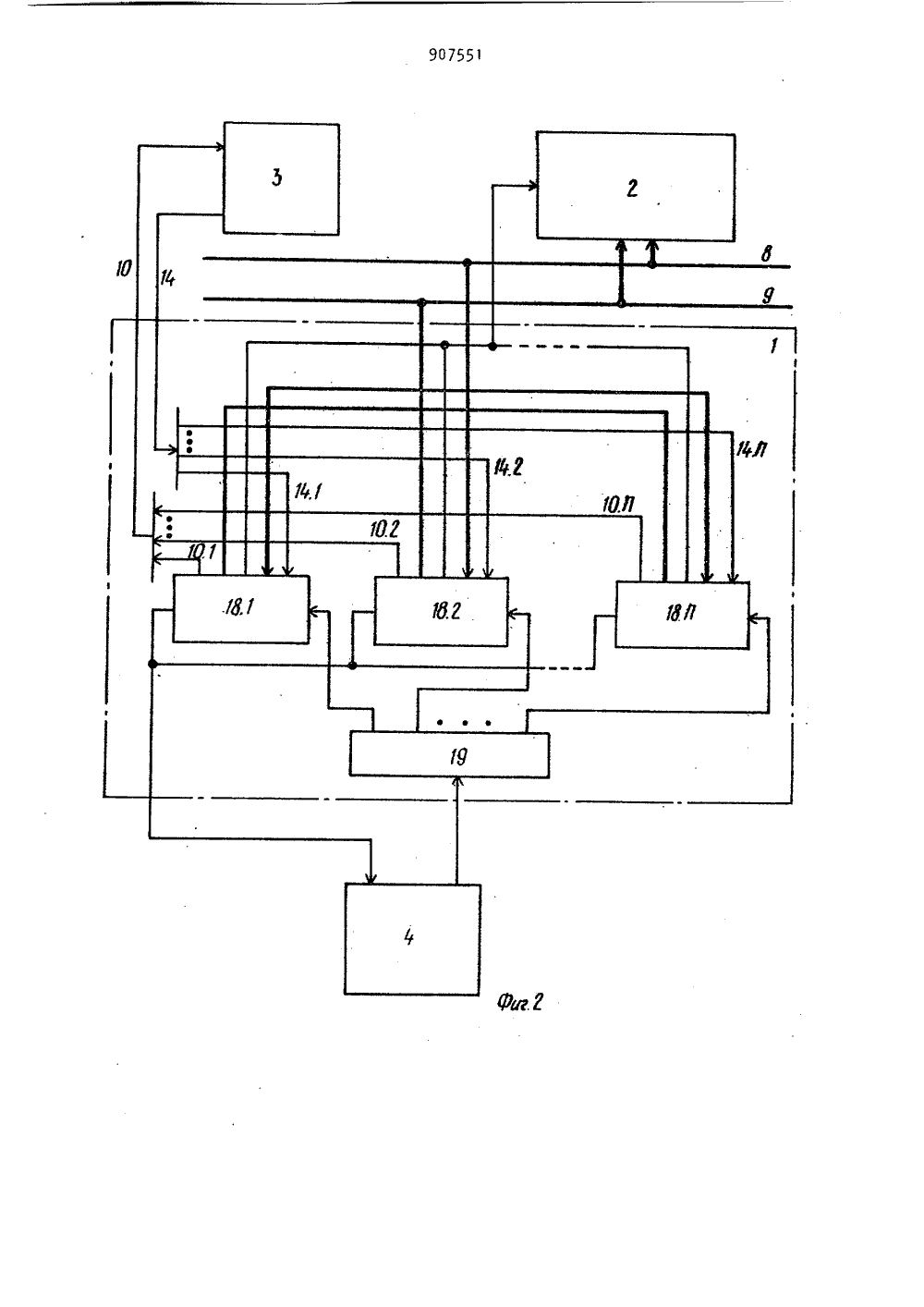

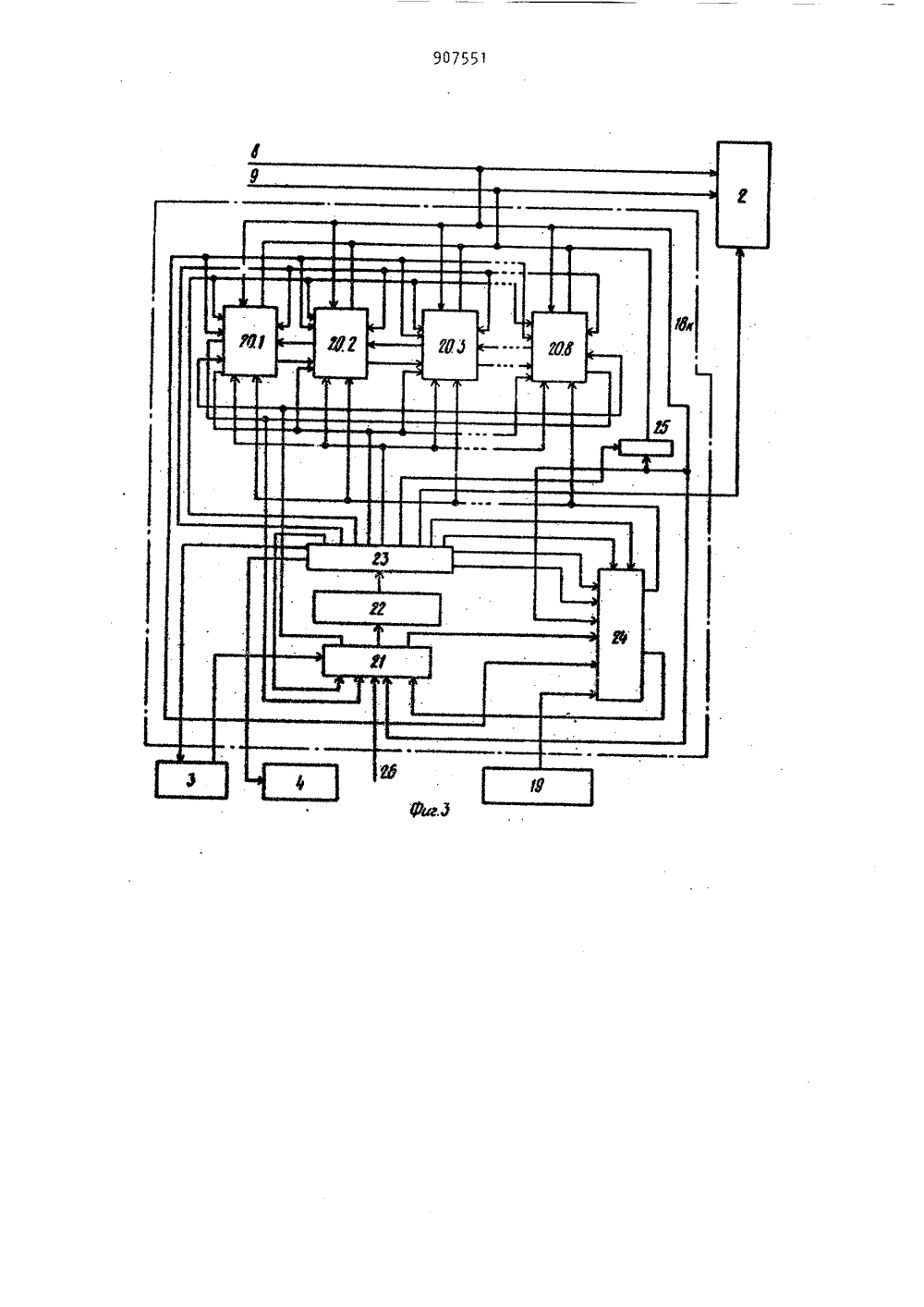

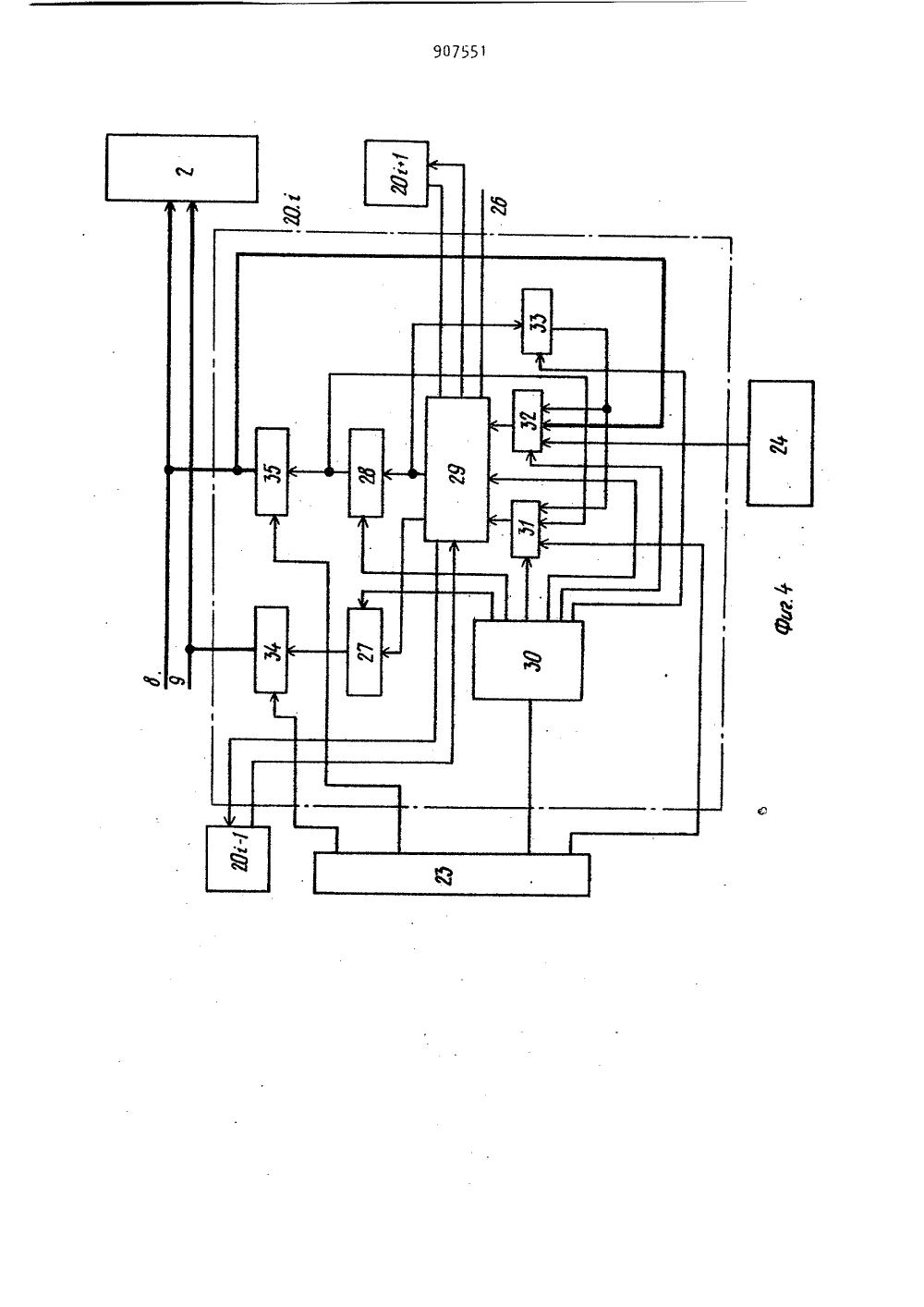

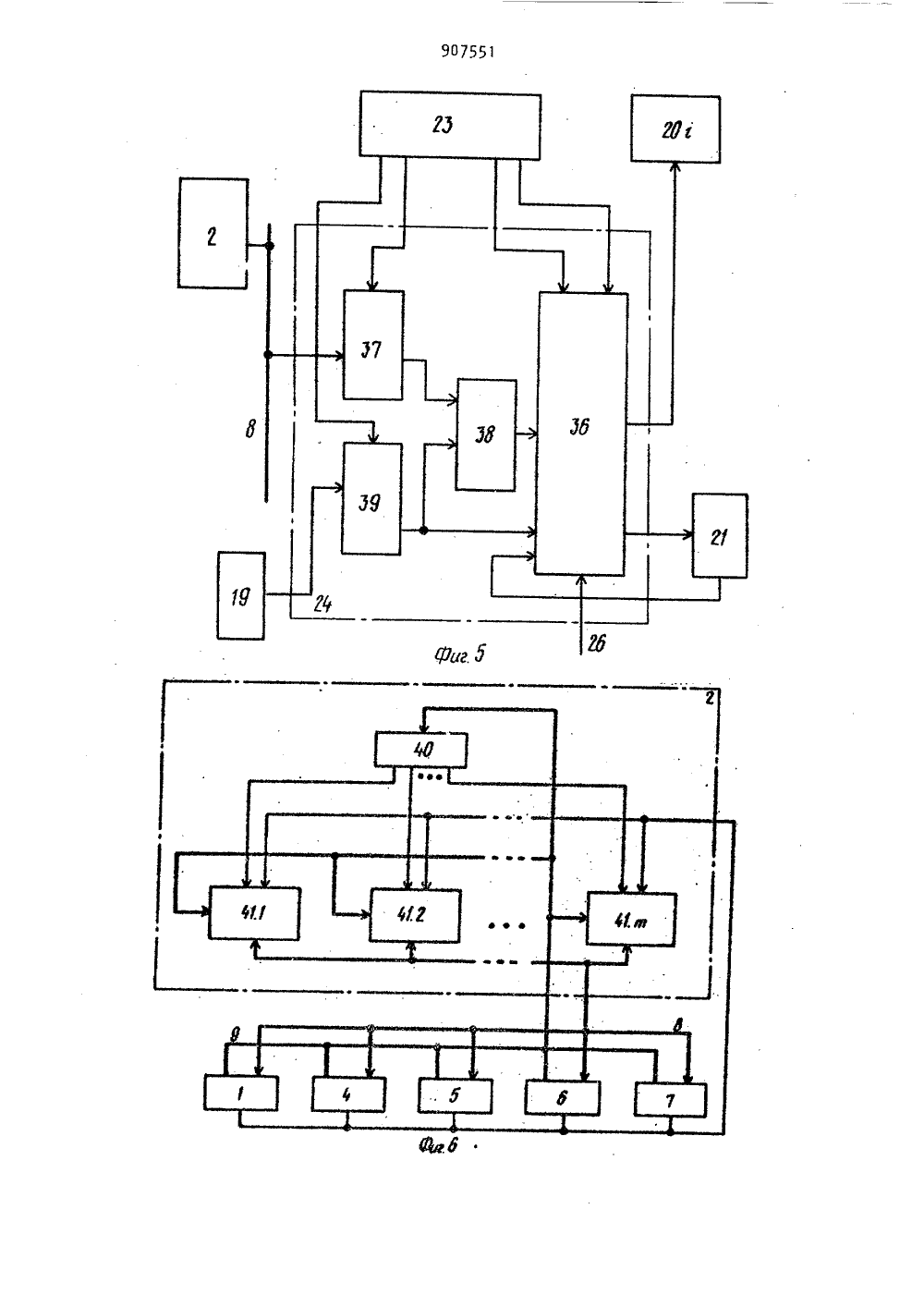

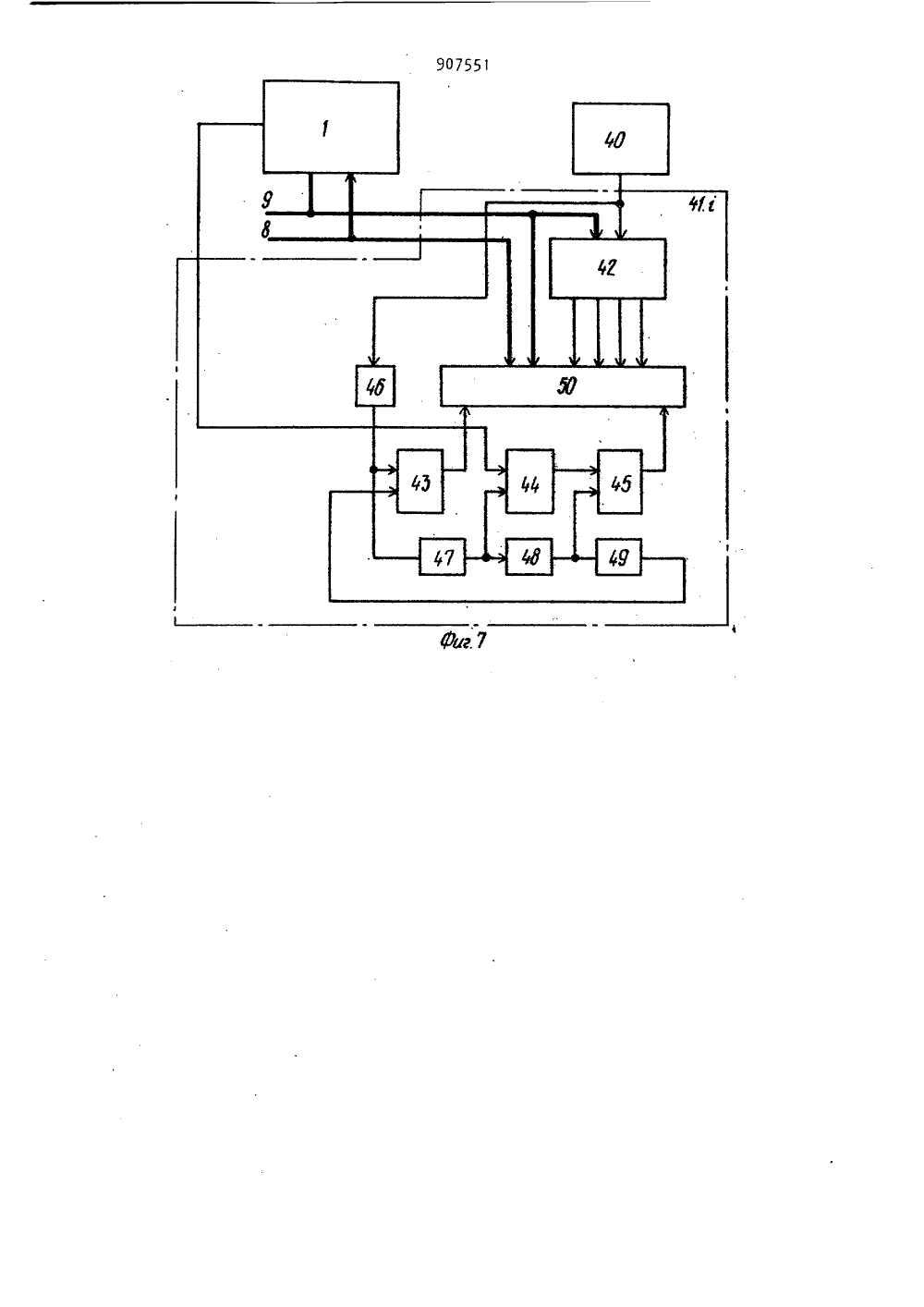

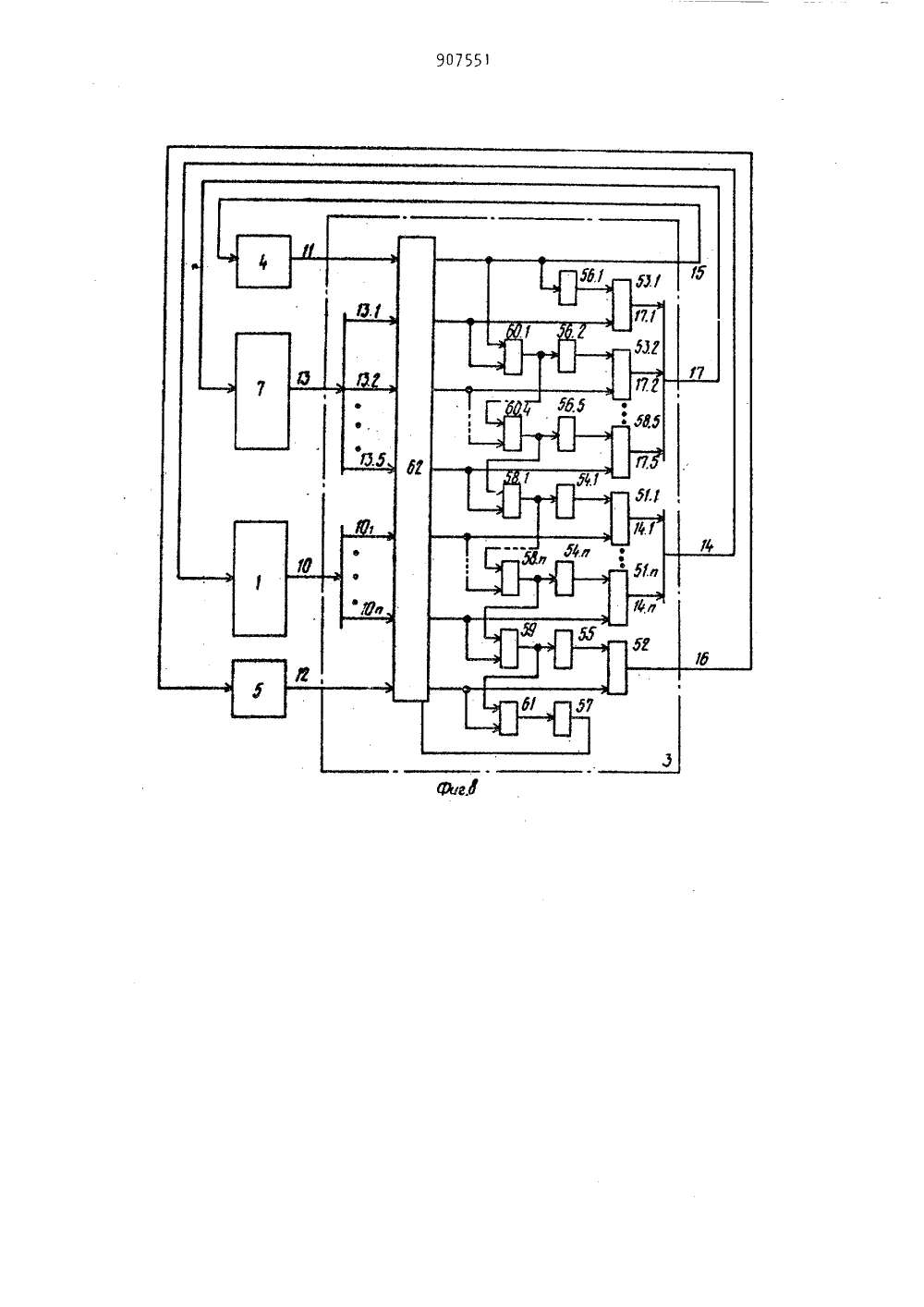

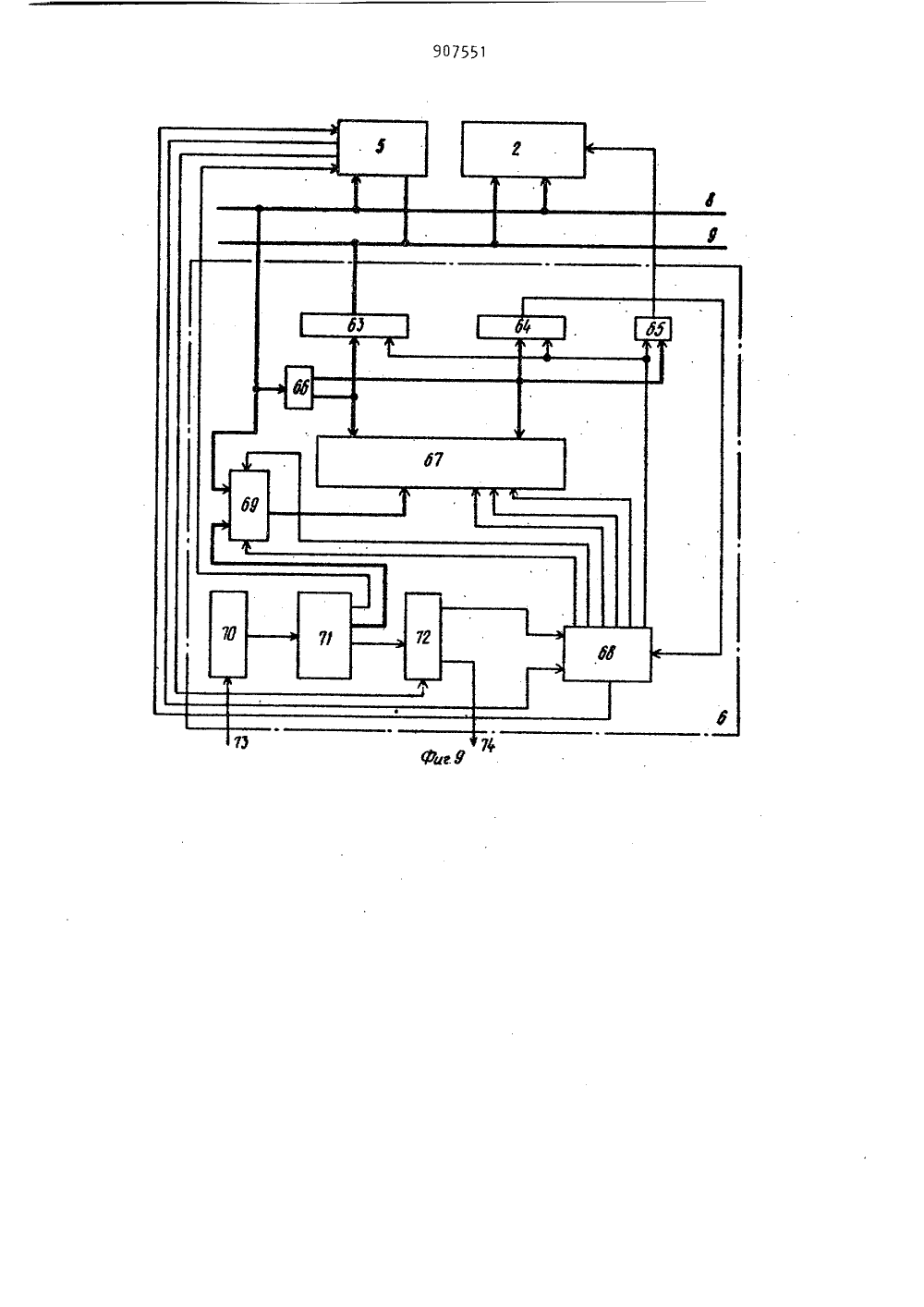

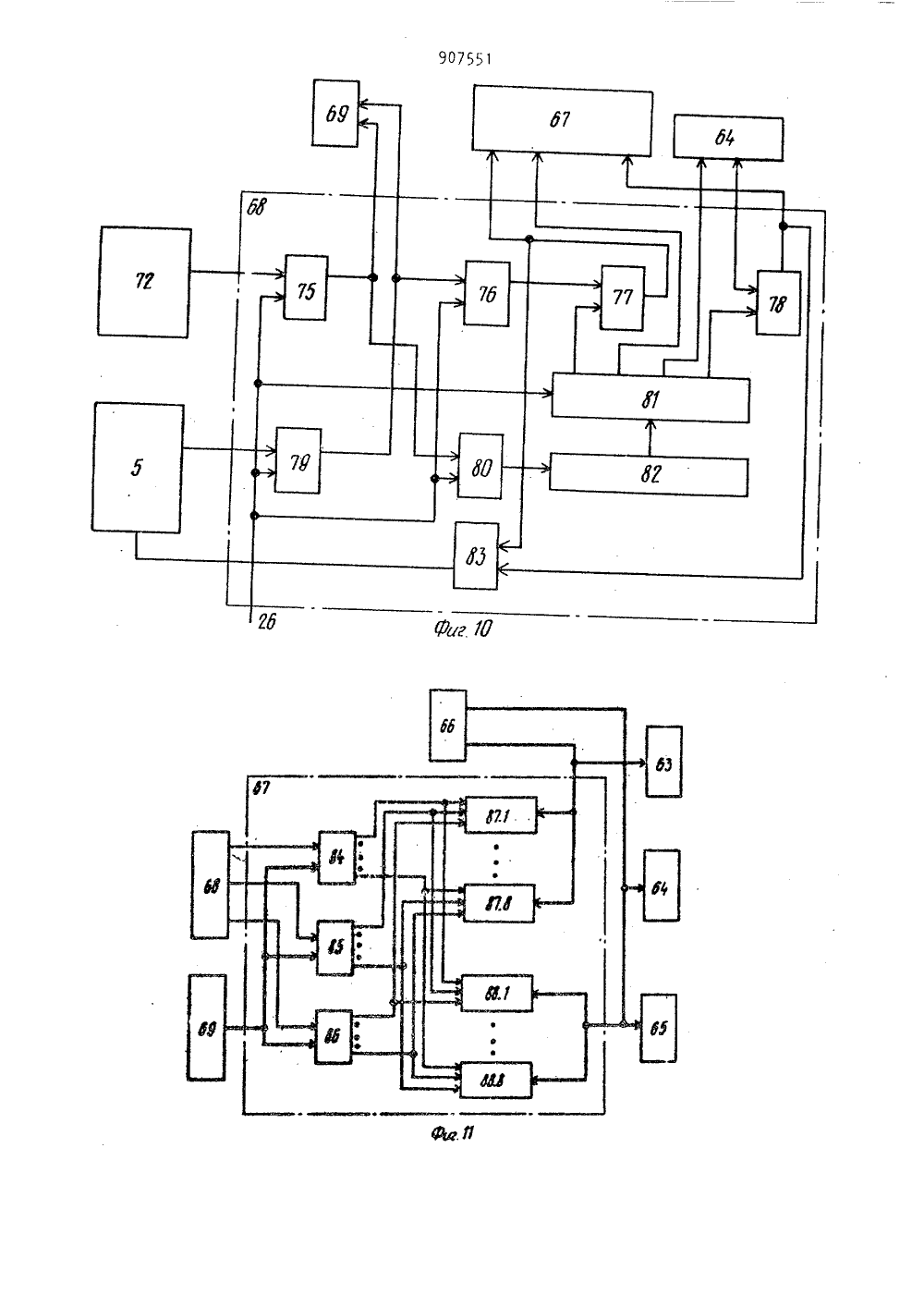

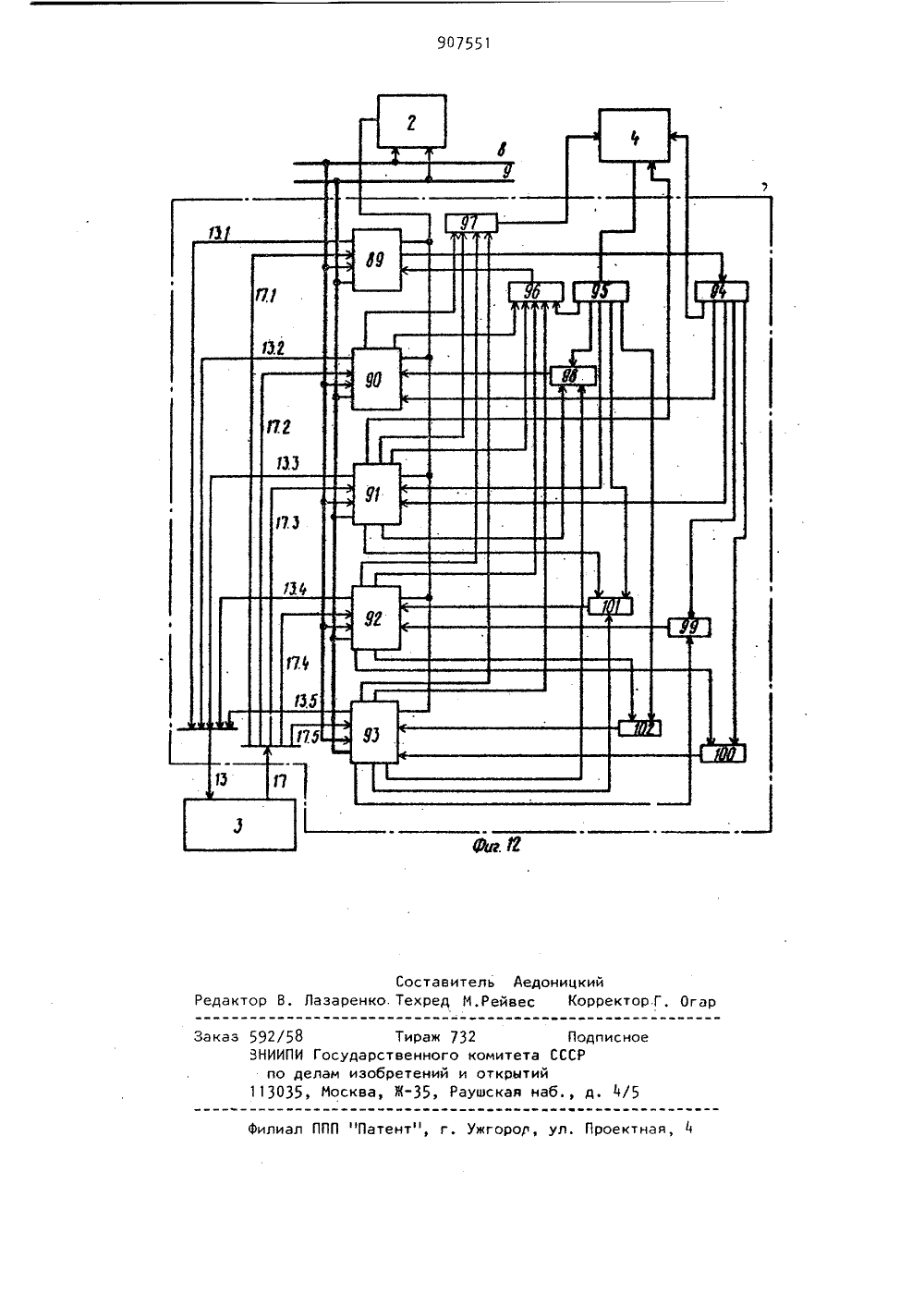

(23) Приоритетво делан нааоретеннй н открытий(54) МУЛЬТИМИКРОПРОЦЕССОРНАЯ СИСТЕМА И обретение относится к вычислительной технике и может быть использовано при проектировании мультимикро процессорных систем.Известны однородные мультимикропроцессорные системы, содержащие бло 5 ки п,мяти и микропроцессорные блоки, связанные шинами адреса и данных и подключенные к коммутатору шин, В однородных мультимикропроцессорных0 системах функции регулировщика и системных примитивов реализованы в виде набора программ ядра операционной системы(ОС) и могут выполняться любым микропроцессорным блоком11 и 1 2,1 ЭНедостатком этих систем являются большие затраты времени на управление и синхронизацию процессов.Наиболее близкой по технической сущности к изобретению является муль" тимикропроцессорная система, содер" жащая группу .исполнительных микро" процессов и микропроцессор распределения ресурсов, связанные шинами с блоками памяти и подсистемой ввода- вывода, оричем управляющие выходы микропроцессора распределения ресурсов подключены к управляющим входам группы исполнительных микропроцессоров, выходы которых связаны по линии запроса ресурсов со входом микропроцессора распределения ресурсов, Микропроцессор распределения ресурсов выполняет здесь функции регулировщика 5.Недостатком известной системы является то, что существует. необходимость реализации коммутатора типа "каждый с каждым" между исполнительными микропроцессорами для организации оперативного выхода микропроцессоров иэ связывающих блокировок на ресурсах. Кроме того, реализация системных примитивов с помощью универсального набора команд, используемого исполнительными микропроцес сорами, приводит к значительным потерям времени при выполнении функ 19 9075цессорного блока 18,К с одиннадцатого выхода регистра 23 микрокомандпоступает сигнал, определяющий режимработы запоминающего устройства 2.Через промежуток времени, определяемый физическими свойствами запо"минающих элементов запоминающегоустройства 2, на информационном входе-выходе исполнительного микропроцессорного блока 18.К устанавливает Ося код адрессованной команды. Адресная часть команды поступает в микропроцессорные узлы 201-,20.8, а операционная часть команды поступает врегистр адреса 21 микрокоманд, 15Операционная часть команды является адресом первой микрокоманды измикропрограммы, интерпретирующейданную команду, Иикрокоманда такжеимеет адресную и операционную часть. 20Адресная часть микрокоманды, содер"жащая адрес следующей за ней микрокоманды, поступает на третий управляющий вход регистра 2 1 адреса микрокоманд. Операционная часть микрокоманды содержит коды микрофункцийпо которым формируются управляющиесигналы, поступающие в узлы и элементы исполнительного микропроцессорного блока 18.К, С приходом каждо- зого синхроимпульса по линии 26 на син"хронизирующие входы микропроцессорныхузлов 20.1-,20.8, на их третьи управ"ляющие входы поступают микрокомандыкоторые декодируются дешифратором30. Первый и второй коммутирующиеэлементы 31 и 32 выбирают операндыи операционный элемент 29 производит нужную операцию. По второму фронту синхроимпульса,результат опеоациипомещается либо в накапливающий регистр 28, либо в заданный регистрэлемента 33 памяти, либо в регистр27 адреса памяти,В конце выполнения каждой команДы 45производится стробирование узла 24прерывания, Запрос, принятый в регистр 39 запросов в течение действиястроба, поступает совместно с кодомиз регистра 37 текущего приоритета на50элемент 38 сравнения, Бсли приоритет поступившего запроса выше текущего приоритета, то шифратор 36 вырабатывает сигнал, поступающий на второй выход узла 24 прерывания. По этому сигналу из регистра 21 адреса мик", 55рокоманд 21 выдается адрес началамикропрограммы обработки прерывания,которая считывает код прерывания и 51 20после соответствующей обработки переписывает этот код в регистр 37 текущего приоритета.Обмен командами и данными между блоками системы и запоминающим устройством 2 осуществляется по шине 8 данных, а выдача адресов производится по шине 9 адреса. При этом запоминающее устройство 2 работает в двух режимах: "Чтениеци "Запись". В режиме "Чтение" код шестнадцати младших разрядов адреса данных поступает на адресные входы блоков 41,1-.41.а памяти, на первых управляющих входах которых устанавливается код режима "Чтение". Код четырех старших разрядов адреса данных, поступающий на вход дешифратора 40, определяет номер блока памяти, На второй управляющий вход выбранного блока 47.1памяти поступает сигнал запуска, с приходом которого на выходе дешифратора 42 появляется сигнал выборки, разрешающий считывание данных из группы запоминающих элементов 50.Через время, определяемое первым элементом 46 задержки первый триггер 43 устанавливается в состояние приема адреса, а на информационный вход- выход блока 4,1.1 памяти выдаются считанные данные. С первого управляющего входа блока 41.1 памяти наэлемент И 44 подается запрещающийсигнал, а второй триггер 46 остается в исходном состоянии "Чтение".Через время, определяемое четвертымэлементом 49 задержки, первый триггер 43 устанавливается в исходное состояние "Хранение", В режиме "Записьн на первых управляющих входахблоков 41,1.-41,щ памяти устанавливается код режима "Запись", а на первый вход элемента И 44 выбранного блока 41.1 памяти поступает разрешающий сигнал, что позволяет сначала установить второй триггер 45, в состояние "Запись, а затемперевести в состояние "Хранение",Блоки системы получают доступ кзапоминающему устройству 2 черезблок 3 коммутации, который обрабатывает запросы. к памяти согласно их приоритетам, Запросы поступают на вход регистра 62 запросов. Наиболееприоритетный запрос формирует наодном из выходов блока 3 коммутации сигнал подтверждения запроса, который одновременно блокирует менее приоритетные запросы. Когда все запросыбудут удовлетворены в порядке очередности, с выхода второго инвертора 57 на управляющий вход регистра 62 запросов поступит сигнал, который с приходом синхроимпульса по линии 26 разрешит прием новой группы запросов.При прохождении пользовательского процесса через систему, он с помощью управляющего микропроцессорного устройства 7 может порождать новые процессы, относящиеся к выполняемому распараллеливаемому заданию, обмениваться сообщениями с ними и с системными процессами, удалять созданные процессы из системы. Запрос управляющего микропроцессорного устройства 7 выполняется исполнительным микропроцессорным блоком 18,К путем обработки экстра кода обращения к ядру ОС, По коду причина прерывания в ТУП пользовательского процесса устанавливается, соответствующий указатель обращения С,У,ПЕР или ПР переписывается, сохраняемая информация и указатель состояния исполнительного микропроцессорного блока 18.К устанавливается в состояние "Свободен", после чего с третьего управляющего выхода исполнительного микропроцессорного блока 18.К выдается сигнал на второй управляющий выход исполнительного микропроцессорного устройства 1, Этот сигнал поступает на первый управляющий вход микропроцессорного блока 11 распределения ресурсов, который начинает просмотр списка УКАЗ СОСТ, анализирует ТУП прерванного процесса и формирует на своем четвертом управляющем выходе соответствующий код прерывания управляющего микропроцессорного устройства 7. После выполнения функций затребованного системного примитива управляющим микропроцессорным устройством 7 а ТУП прерванного процесса устанавливается указатель готовности процесса к выполнению, и на четвертый управляющий вход микропроцессорного блока 4 распределе" ния ресурсов поступает сигнал о наличии готового процесса в системе. Микропроцессорный блок 4 распределения ресурсов через Р-операцию над СЕМ ОБЦ СПИСКА входит в общий список процессов, находит ТУП готового про" цесса, выполняет Ч"операцию над СЕМ ОБЦ 1 СПИСКА, помещает адрес найденной ТУП и метку ЗАНЯТ в УКАЗ СОСТ 5 10 15 20 25 ЗО 35 10 45 50 55 свободного исполнительного микропроцессорного блока 18,1 устанавливает в ТУП указатель А и формируетна своем втором управляющем выходекод номера микропроцессорного блока18,1. Этот код через второй управляющий .вход исполнительного микро"процессорного устройства 1 поступаетна регистр 19. и вызывает прерываниеисполнительного микропроцессорногоблока 18,1, который по адресу ТУП всвоем указателе: состояния находитэту ТУП, загружает на собственныерегистры необходимые параметрь 1 изТУП и переходит к выполнению программы,При выполнении примитивов ядраОС блоки управляющего микропроцессорного устройства 7 работают следующимобразом.Микропроцессорный блок 90 создания процесса при появлении на еговтором управляющем входе сигнала,поступающего со второго управляющеговхода управляющего микропроцессорногоустройства 7 через второй регистр 95 итретий элемент ИПИ 98, выполняет Р-операцию над СЕМ ОБ 51 СПИСКА, находит ТУПс указателем С, загружает на собственные регистры необходимые для выполнения параметры из этой ТУП и выполяет Ч-операцию над СЕМ ОБШ, СПИСКАЗатем производится Р-операция надСЕМ СПИСКА ПАМ, выполняется поисксвободной зоны памяти, объем которой достаточен для оформления ТУПсоздаваемого процесса, и производится Ч"операция над СЕМ СПИСКА ПАМ,Далее в выделенной зоне памяти фор"мируется ТУП создаваемого процесса,выполняется Р"операция над СЕМ ОБО,СПИСКА, данная ТУП включается в об-,щий список процессов, в ТУП процесса-создателя снимается указатель Си, устанавливается указатель Г, а счетвертого управляющего выхода мик"ропроцессорного блока 90 созданияпроцесса через второй элемент ИЛИ 97посылается сигнал на четвертый уп"равляющий выход управляющего микро"процессорного устройства 7.Микропроцессорный блок 91 уничтожения процесса при появлении наего третьем управляющем входе сигнала, поступающего со второго управ"ляющего входа управляющего микропро"цессорного устройства 7 через второй регистр 95, выполняет Р-операциюнад СЕМ ОБЦ СПИСКА, находит ТУП с23 9075 указателем У, загружает на собственные регистры необходимые для выполнения параметры из этой ТУП и произ. водит поиск ТУП уничтожаемого процесса, после чего производится ее исключение из общего списка процессов и выполняется Ч-операция над СЕМ ОБЦ СПИСКА. Затем микропроцессорный блок 91 уничтожения процесса по указателю СЕМ СООБЩ находит адрес списка 1 о сообщений уничтожаемого процесса и через СЕМ СПИСКА ПАМ производитвключение памяти, занимаемой адрессованными этому процессу сообщениями, в СПИСОК ПАМ, после чего в этот 15 же список включается память, занимаемая ТУП уничтожаемого процесса. После этого в ТУП прерванного процесса устанавливается указатель Г и с четвертого управляющего выхода мик о ропроцессорного блока 91 уничтожения процесса через элемент ИЛИ 96 посылается сигнал на четвертый управляющий выход управляющего микропроцессорного устройства 7, Если д 5 микропроцессорный блок 91 уничтожения процесса удаляет из системы процесс, находящийся в стадии выполнения на одном из. исполнительных микропро" цессорных блоков 18. 1-:18.п, то в 3 О УКАЗ СОСТ этого исполнительного блока устанавливается метка "Свободен", а с третьего управляющего выхода микропроцессорного блока 91 уничтожения процесса посылается сигнал на третий управляющий выход управлящего микропроцессорного устройства 7,Микропроцессорный блок 92 передачи сообщения при появлении на его третьем управляющем входе сигнала, поступающего со второго управляющего входа управляющего микропроцессорного устройства 7 через регистр 95 и элемент ИЛИ 101, выполнен Р- операцию над СЕМ ОБЦ СПИСКА, нахо дит ТУП с указателем ПЕР, загружает на собственные регистры необходимые для выполнения примитива параметры из этой ТУП,производит поиск ТУП процесса-приемника и выполняет Ч-опе 50 рацию над СЕМ ОБЩ СПИСКА, Затем над СЕМ СПИСКА ПАМ выполняется Р-опера" ция, производится поиск зоны памяти, объем которой достаточен для оформления передаваемого сообщения, и выполняется Ч-операция над СЕМ СПИСКА ПАМ, После этого оформляется сообщение в выделенной зоне памяти, выполняется Р-операция над СЕМ СПИСКА 24СООБЩ процесса-приемника, сообщение включается в СПИСОК СООБЦ выполняется Ч-операция над СЕМ СПИСКА СООБЩ и производится Ч-операция над СЕМ СООБЩ процесса-приемника, после чего в ТУП процесса-передатчика устанавли" вается указатель Г и с управляющего выхода микропроцессорного блока 92 передачи сообщения посылается сигнал через элемент ИЛИ 97 на чертвертый управляющий выход управляющего микропроцессорного устройства 7.Микропроцессорный блок 93 приема сообщения при появлении на его третьем упразляющем ходе сигнала, поступающего со второго управляющего входа управляющего микропроцессорного устройства 7 через регистр 95 и элемент ИЛИ 102, выполняет Р-операцию над СЕМ ОБЦ СПИСКА, находит ТУП с указателем ПР, загружает на собственные регистры необходимые для выполнения примитива параметры из этой ТУП и производит Ч-операцию над СЕМ ОБШ СПИСКА, Затем над СЕМ СООБЩ в найденной ТУП выполняется Р-операция и, в случае наличия адресованных про-, цессу сообщений, производится Р-операция над СЕМ СПИСКА СООБЩ, из СПИСКА СООБЦ считывается первое сообщение и выполняется Ч-операция над СЕМ СПИСКА СООБЩ, после чего производится Р-операция над СЕМ СПИСКА ПАМ, память, занимаемая прочитанным сообщением, включается в СПИСОК ПАМ и выполняется Ч-операция над СЕМ СПИСКА ПАМ. После этого в ТУП устанав ливается указатель Г и с седьмого управляющего выхода микропроцессорного блока 93 приема сообщения посылается сигнал через элемент ИЛИ 97 на четвертый управляющий выход управляющего микропроцессорного устройства 7. В случае отсутствия адресованных процессу сообщений в ТУП устанавливается указатель БЛОК СООБЩ, что переводит процесс в список блокированных процессов.Если при выполнении микропроцессорным блоком 92 передачи сообщений ,Ч-операции над СЕМ СООБЩ процесс- приемник находится в состоянии БЛОК СООБЩ, то в ТУП процесса-приемника снимается указатель БЛОК СООБЦ, устанавливается указатель ПР и с управляющего выхода микропроцессорного блока 9 передачи сообщения посылается сигнал через элемент ИЛИ 102 на второй управляющий вход микропоо-.цессорного блока 93 приема сообщения.При работе микропроцессорногоблока 90 создания процесса, требующего память для формирования ТУП 5создаваемого процесса, или микропроцессорного блока 92 передачи сообщения, требующего память для формирования посылаемого процессом сообщения, возможно отсутствие достаточного объема свободной памяти. Вэтом случае микропроцессорный блок 90или 92 выполняет Р-операцию над СЕМПАМ, устанавливает в ТУП процессасоздателя или процесса-передатчикасоответствующий указатель БЛОК ПАМ Сили БЛОК ПЯМ ПЕР, выполняет Р-операцию над СЕМ СПИСКА БЛОК ПАМ, вклю"чает ТУП в список блокированныхнад СЕМ ПАМ процессов и выполняет 20Ч-операцию над СЕМ СПИСКА БЛОК ПАМ.При работе микропроцессорногоблока 91 уничтожения процесса освобождается память, занимаемая ТУП исообщениями уничтожаемого процесса,а при работе микропроцессорного блока 93 приема сообщения освобождается память, занимаемая прочитаннымсообщением. После упорядочения СПИСКА ПАМ микропроцессорный блок 91или 93 посредством Ч-операции надСЕМ ПАМ проверяет наличие блокированных на этом семафоре процессов,и в ТУП первого из СПИСКА БЛОК ПАМпроцесса устанавливается указательС или ПЕР, после чего с пятого управляющего выхода микропроцессорногоблока 91 уничтожения процесса или стретьего управляющего выхода микропроцессорного блока 93 приема сообщения посылается сигнал через третий элемент ИЛИ 98 на второй управляющий вход микропроцессорного блока90 создания процесса, либо с шестогоуправляющего выхода микропроцессорного блока 91 уничтожения процесса,или с четвертого управляющего выхо"да микропроцессорного блока 93 приема сообщения посылается сигнал черезэлемент ИЛИ 101 на третий управляющий вход микропроцессорного блока 92передачи сообщения,При асинхронных просмотрах системных списков микропроцессорными бло 55 ками 4,90,91, 92,93 возможно возникновение связывающей блокировки на системных семафорах СЕМ ОБЩ СПИСКА, СЕМ СПИСКА ПАМ и СЕМ СПИСКА БЛОК ПАМ. Оперативный выход из режима связыва ющей блокировки реализуется с гомощью микропроцессорного блока 89 синхронизации. При выполнении одним из микропроцессорных блоков 4,90,91,92,93 Р-операции над системным семафором и в случае блокировки на этом семафоре в памяти устанавливается указатель соответствующего микропроцессорного блока, требующего доступа к системному списку, При выполнении одним из микропроцессорных блоков 4,90, 91,92,93 Ч-операции над системным семафором и в случае наличия блокированного микропроцессорного блока на второй управляющий вход микропроцессорного блока 89 синхронизации поступает сигнал через элемент ИЛИ 96 с соответствующего управляющего выхода одного из микропроцессорных блоков 4,90,91,92,93, выполнявшего Ч-операцию, По этому сигналу микропроцессорный блок 89 синхронизации анализирует соответствующие указатели блокировок, снимает указатель и выдает на третий управляющий выход код, по которому через регистр 95 на третий управляющий вход блокированного микропроцессорного блока 90, и на входы блоков 91, 92,93 или на третий управляющий вход микропроцессорного блока 4 распределения ресурсов поступает сигнал, выводящий блок из режима связывающей блокировки.Между микропроцессорными блоками 92 и 93 может возникать связывающая блокировка на СЕМ СПИСКА СООБЩ. При выполнении микропроцессорным блоком 92 передачи сообщений или микропроцессорным блоком 93 приема сообщения Р-операции над СЕМ СПИСКА СООБЩ и в случае блокировки на этом семаФоре микропроцессорный блок переходит в режим ожидания сигнала на своем втором управляющем входе. При выполнении одним из микропроцессорных блоков 92,93 Ч-операции над СЕМ СПИС" КА СООБЩ и в случае наличия блокировки на этом семафоре другого из микропроцессорных блоков 92 и 93 производится выдача сигнала разблокировки либо с шестого управляющего выхода микропроцессорного блока 92 передачи сообщения через элемент ИЛИ 100 на второй управляющий вход микропроцессорного блока 93 приема сообщения, либо с пятого управляюще28 27 907551 го выхода микропроцессорного блока93 приема сооЬщения через элементИЛИ 99 на второй управляющий входмикропроцессорного блока 92 передачи сообщения,Выполнение пользовательского процесса заканчивается обработкой экстракода обращения к ядру ОС. Приэтом происходит прерывание микропроцессорного блока 92 передачи сообщения, который формирует сообщение планировщику заданий. Планировщик заданий переводится из спискаблокированных процессов в число готовых к выполнению процессов, микропроцессорный блок ч распределения ресурсов назначает ему один изисполнительных микропроцессорныхблоков 18.1-.18.п, после чего планировщик заданий обращается к микропроцессорному блоку 93 приема сообщений, анализирует считанное сообщение, выводит через микропроцессорный блок 5 ввода-вывода и устройство 6 связи с памятью выходные данные пользовательского процесса наустройство печати (не показано) ивыдает экстракод обращений к микропроцессорному блоку 91 уничтоженияпроцесса, Отработавший пользовательский процесс удаляется из системы,а микропроцессорный блок 93 приемасообщения выполняет Р-операцию надСЕИ СООБЩ в ТУП планировщика заданий и включает эту ТУП в список блокированных на ожидании сообщенияпроцессов. После получения сообщения о завершении выполнения 1-гозадания планировщик заданий помещаетв оперативную память очередную порцию из нескольких заданий, хранящихся на магнитном диске, и описанныйвыше цикл работы системы повторяется Взаимодействие системы с внешними устройствами осуществляется через микропроцессорный блок 5 ввода-вывода и устройство 6 связи с памятью. Устройство 6 связи с памятью работает в двух режимах: "Программирование канала" и "Передача". В режиме "Программирование канала" микропроцессор" ный блок 5 ввода-вывода производит запись в блок 67 регистров адреса начала записи, кода длины записи и кода режима передачи данных, причем запись осуществляется в два этапа. На первом этапе адрес начала записи данных через коммутатор 66 поступает 5 0 15 20 25 30 35 40 45 50 55 на второй информационный вход блока 67 регистров, а адрес регистра, в который будет произведена запись, поступает на третий информационный вход блока 67 регистров через переключатель 69. Одновременно с третьего управляющего выхода микропроцессорного блока 5 ввода-вывода через второй управляющий вход устройства 6 связи с памятью на третий вход бло. ка 68 управления поступает сигнал "Запись", который устанавливает второй триггер 79 блока 68 управления в состояние "Программирование канала". В этом со:тоянии разрешено поступление адреса регистра через переключатель 69 на третий информационный вход блока 67 регистров и разрешено прохождение синхроимпульсов через первый элемент И 76 и первый элемент ИЛИ 77 на четвертый и седьмой выходы блока 68 управления. Адрес регистра поступает в блок 67 регистров на дешифраторы 8 чи адрес начала записи данных запоминается в заданном регистре первой группы регистров 87. 1-.87,8, После этого микропроцессорный блок 5 ввода-вывода снимает сигнал Запись", На втором этапе микропроцессорный блок 5 ввода-вывода выдает на шину 8 данных код длины записи данных, код режима передачи и адрес регистра из второй группы регистров 88.1-:88,8 блока 67 регистров, в который должна быть произведена запись. Код длины записи данных и код режима передачи поступают через коммутатор 66 на первый информационный вход блока 67 регистров. Дальнейший порядок работы устройства 6 связи с памятью на втором этапе аналогичен работе устройства на первом этапе.В режиме "Передача" запросы на передачу данных поступают от внешних устройств по линии 73 в регистр 70 запросов. Шифратор 71 формирует на выходе код запроса, который, являясь одновременно адресом регистра в блоке 67 регистров, поступает на вход переключателя 68. С третьего выхода шифратора 71 выдается сигнал нЗапрос шин на третий управляющий выход уст ройства 6 связи с памятью, Этот сигнал транслируется микропроцессорным блоком 5 ввода-вывода в блок 3 коммутации. Получив иэ блока 3 коммутации сигнал "Подтверждение запроса" микропроцессорный блок 5 ввода-вы29 Мультимикропроцессорная система,содержащая исполнительное микропровода транслирует его через второй управляющий вход устройства 6 связи с памятью в буферный узел 72 и приостанавливает свою работу. Из буферного узла 72 по линии 74 во внешнее уст ройство поступает сигнал, по которому внешнее устройство выдает подготовленные данные на шину 8 данных, Из буферного узла 72 посылается также сигнал на второй вход блока 68 управ- )О пения, который устанавливает первый триггер 72 в состояние "Передача". Этим самым разрешается прохождение адреса регистра через переключатель 69 на третий информационный вход бло ка 67 регистров и прохождение синхроимпульса через третий элемент И 80 на вход счетчика 82, который устанавливается в состояние "Чтение. Че реэ дешифратор 81 сигнал "Чтение" 20 передается в блок 67 регистров и осуществляется считывание содержимого двух регистров из групп регистров 87.1-:87,8 и 88.1-88.8, адрес которых установлен на входе дешифра- г 5 торов 84-86. Содержимое адресованных регистров поступает в счетчик 63 адреса записи, счетчик 64 длины записи и регистр 65 режима работы,приходом второго синхроимпульса з) счетчик 82 переходит в состояние "+1" Через дешифратор 81 сигнал +1" передается в блок 67 регистров, увеличивает содержимое счетчика 63 адреса записи и уменьшает содержимое счетчика 64 длины записи на единицу. Третий синхроимпульс устанавливает счетчик 82 в состояние "Общий сброс" и (если содержимое счетчика длины записи 64 равно нулю) сигнал со второго выхода дешифратора 81 через второй элемент И 78 поступает на второй и седьмой выходы блока 68 управления. Содержимое адресуемых регистров блока 67 регистров установит ся равным нулю. По сигналу на своем втором управляющем входе микропроцессорный блок 5 ввода-вывода через первый управляющий вход устройства 6 связи с памятью, буферный узел 72 и второй вход блока 68 управления установит первый триггер 75 в исходное состояние. Если содержимое счетчика 64 длины записи не равно нулю то состояние устройства 6 связи с55 памятью не меняется, Четвертый синхроимпульс устанавливает в счетчике 82 состояние "Запись" , В этом случае сигнал "Запись" с дешифратора 81 51 30поступит в блок 67 регистров, гдепроизведет запись содержимого счетцика 63 адреса записи, счетчика 64длины записи и регистра 65 режимаработы в два регистра первой и второй групп регистров 87. 1 .87.8 и88,1-;88,8 по адресу, установленномуна третьем информационном входе блока 67 регистров. Этот же сигнал поступит и в микропроцессорный блок 5ввода-вывода. С приходом пятого синхроимпульса дешифратор 81 сформирует сигнал "Сброс", который установит счетчик 63 адреса записи, счетчик 4 длины записи и счетчик 82 внулевое состояние, После этого сигнал с микропроцессорного блока 5 ввода-вывода установит блок 68 управления в исходное состояние, атакже снимет запрос со входа блока 3 коммутации. Последующие сеансы связи внешних устройств с запоминающим устройством 2 осуществляются аналогично,Таким образом, производительностьпредлагаемой мультимикропроцессорнойсистемы по сравнению с известной увеличивается за счет увеличения пропускной способности системы в связи с возможностью совмещения Фазы выполнения системных примитивов и фазы назначение исполнительных микропроцессорных блоков для последовательности обрабатываемых процессовпараллельная работа функциональновыделенных управляющих микропроцес"сорных блоков и исполнительных микропроцессорных блоков , а также засчет снижения накладных расходов операционной системы на выполнение Функций управления и синхронизации приаппаратно-микропрограммной структуризации ядра программного обеспечения.Кроме того, предлагаемая системапозволяет упростить управление вмультимикропроцессорной системе засчет закрепления функций обработкипрерываний определенного типа за определенными модулями и упрощения,тем самым структуры межмодульногокоммутатора и механизма идентификации микропроцессорных модулей приорганизации оперативного доступа кресурсам и таблицам через семафоры. Формула изобре гения31 9075цессорное устройство, микропроцессорный блок распределения ресурсов, микропроцессорный блок ввода-вывода,устройство свзяи с памятью, управляющее микропроцессорное устройство,включающее микропроцессорный блоксинхронизации, первые управляющиевыходы, адресные выходы и информационные входы-выходы которых соединены соответственно с управляющим 1 Овходом, через шину адреса - с адресным входом и через шину данных - синформационным входом-выходом запоминающего устройства, блок коммутации, включающий регистр запросов, 15первые группы элементов И, элементов ИЛИ, элементов НЕ, два элементаИЛИ, два элемента НЕ, элемент И, выход которого соединен с первым управляющим входом микропроцессорного блока ввода-вывода, второй и третий управляющие входы и второй, третий и четвертый управляющие выходы которого соединены соответственно с вторым и третьим управляющими выхо дами и с первым и вторым управляющими входами устройства связи с памятью и с входом первого разряда регистра запросов, выход первого разряда регистра запросов блока коммутации сое- ЗО динен с первыми входами элемента И и первого элемента ИЛИ блока коммутации выход первого элемента ИЛИ блока коммутации через первый элемент НЕ соединен с входом синхронизации регистра запросов, выходы элементов И первой группы соединены с первым управляющим входом исполнительного микропроцессорного устройства, второй управляющий вход и второй и третий управляющие выходы которого соединены соответственно с вторым управляющим выходом и с первым управляющим входом микропроцессорного блока распределения ресурсов и с входами первой группы разрядов регистра запросов, выходы последнего разряда первой группы, последнего разряда второй группы разрядов регистра запросов блока коммутации5 О соединены с первыми входами соответственно второго элемента ИЛИ и первого элемента ИЛИ первой группь 1 блока коммутации, первые входы остальных элементов ИЛИ первой группы55 соединены с выходами оставшихся раз- рядов первой группы регистра запросов, первые и вторые входы элементов И первой группы блока коммутации соединены соответственно с выходамиразрядов первой группы регистра Запросов и через элементы НЕ первойгруппы -выходами элементов ИЛИпервой группы, выход каждого предыдущего элемента ИЛИ первой группыблока коммутации соединен с вторымвходом последующего элемента ИЛ 1первой группы, а выход последнегоэлемента ИЛИ первой группы соединенс вторым входом второго элемента ИЛИблока коммутации, выход которогосоединен с вторым входом первого элемента ИЛИ и через второй элемент НЕс вторым входом элемента И блока коммутации, третий управляющий выход ивторой управляющий вход микропроцессорного блока распределения ресурсов соединены соответственно со входом и выходом второго разряда регистра запросов, с т л и ч а ю щ ая с я тем, что, с целью повышенияпр изводительности системы, в управляющее микропроцессорное устройствовведены микропроцессорный блок создания процесса, микропроцессорныйблок уничтожения процесса микропроцессорный блок передачи сообщения,микропроцессорный блок приема сообщения, два управляющих регистра,семь элементов ИЛИ, а в блок коммутации введены вторые группы элементов ИЛИ, элементов НЕ и элементов И,причем первые управляющие входы ивыходы, вторые управляющие выходы,адресные выходы и информационные входы-выходы микропроцессорных блоковсоздания процесса, уничтожения процесса, передачи сообщения, приемасообщения соединены соответственнос выходом второй группы элементов И,с входом второй группы разрядов регистра запросов, с управляющим входом, через шину адреса с адреснымвходом и через шину данных с информационным входом-выходом запоминающего устройства, первый и второй управляющие входы и второй и третийуправляющие выходы микропроцессорно"го блока синхронизации соединены соответственно с выходом второй группыэлементов И, с выходом первого элемента ИЛИ управляющего микропроцессорного устройства, со входом второй группы разрядов регистра запросов, с входом первого регистра, третий и четвертый управляющие выходы ивторой и третий управляющие входымикропроцессорного блока создания про40 Источники информации, принятые во внимание при экспертизе 1. Патент США Г 4034347,4 кл. 6 06 Г 13/10,15/16, 1977 3390 цесса соединены соответственно с первыми входами первого и второго элементов ИЛИ управляющего микропроцессорного устройства, с выходом третьего элемента ИЛИ и с первым выходом первого регистра, второй, третий, четвертый и пятый выходы которого соединены соответственно с третьим управляющим входом микропроцессорного блока распределения ресурсов, с первыми входами четвертого и пятого элементов ИЛИ, с вторым управляющим входом микропроцессорного блока уничтожения процесса, третий управляющий вход, третий, четвертый, пятый, шестой, седьмой управляющие выходы которого соединены соответственно с первым выходом второго регистра, с первым управляющим входом микропроцессорного блока распределения ресурсов, с вторым входом второго элемента ИЛИ управляющего микропроцессорного устройства, с первыми входами третьего и шестого элементов ИЛИ с вторым входом первого элемента ИЛИ управляющего микропроцессорного устройства, третий вход которого сое. динен с вторым выходом второго регистра, вход, третий, четвертый и пятый выходы которого соединены соответственно с четвертым управляющим выходом микропроцессорного блока распределения ресурсов, вторыми входами третьего и шестого элементов ИЛИ, с первым входом седьмого элемента ИЛИ, второй вход которого соединен с третьим управляющим выходом микропроцессорного блока передачи сообщения, второй и третий управляющие входы, четвертый, пятый и шестой управляющие выходы которого соединены соответственно с выходами четвертого и шестого элементов ИЛИ, с третьим входом второго элемента ИЛИ управляющего микропроцессорного устройства, с четвертым входом первого элемента ИЛИ управляющего микропроцес сорного устройства, с вторым входом пятого элемента ИЛИ, выход которого соединен с вторым управляющим входом 7551 34микропроцессорного блока приема сообщения, третий управляющий вход,третий, четвертый, пятый, шестой иседьмой управляющие выходы которогосоединены соответственно с выходомседьмого элемента ИЛИ, с третьимивходами третьего и шестого элементаИЛИ, с вторым входом четвертого элемента ИЛИ, с пятым входом первого и 10 с четвертым входом второго элементов ИЛИ управляющего микропроцессорного устройства, выход второго элемента ИЛИ управляющего микропроцес"сорного устройства соединен с чет вертым управляющим входом микропроцессорного блока распределения ресурсов, выход последнего разряда второйгруппы регистра запросов соединен спервым входом элемента И второй груп пы, выходы остальных разрядов вто-.рой группы регистра запросов соединены с первыми входами оставшихсяэлементов И второй группы и с первыми входами элементов ИЛИ второй 2 Б группы, вторые входы элементов Ивторой группы соединены, с выходамисоответствующих элементов НЕ второйгруппы, вход первого элемента НЕ второй группы соединен с выходом второ- зО го разряда регистра запросов, входыостальных элементов НЕ второй группысоединены с выходами соответствующихэлементов ИЛИ второй группы, выход каждого предыдущего элемента ИЛИ второйгруппы соединен с вторым входом последующего зле мен т а ИЛИ второй г руппы, выходпоследнего элемента ИЛИ второй группысоединен с вторым входом первого элемента ИЛИ первой группы. 2. Патент США 6 4065809,кл, С 06 Г 15/16, 1977.3, "Совросег де 10 п". 1974,й 3, р 865025 3 9075 ций управления процессами, что вызывает снижение производительности системы в целом.Цель изобретения - повышение производительности системы.Поставленная цель достигается тем, что в мультимикропроцессорную систему, содержащую исполнительное микропроцессорное устройство, микропроцессорный блок распределения 1 О ресурсов, микропроцессорный блок ввода-вывода, устройство связи с памятью, управляющее микропроцессорное устройство, включающее микропроцессорный блок синхронизации, первые 15 ,управляющие выходы, адресйые выходы и информационные входы-выходы которых соединены соответственно с уп равляющим входом, через шину адреса - с адресным входом и через шину20 данных - с информационным входом-выходом запоминающего устройства, блок коммутации, включающий регистр запросов, первые группы элементов И, элементов ИЛИ, элементов НЕ, два элемента ИЛИ, два элемента НЕ, элемент И, выход которого соединен с первым управляющим входом микропроцессорного блока ввода-вывода, второй и третий управляющие входы и атоЗ 0 рой, третий и четвертый управляющие выходы которого соединены соответственно со вторым и третьим управляющими выходами и с первым и вторым управляющими входами устройства связи с памятью и со входом первого разряда регистра запросов, выход первого разряда регистра запросов блока коммутации соединен с первыми входами элемента И и первого элемента ИЛИ блока коммутации, выход первого элемента ИЛИ блока коммутации через первый элемент НЕ соединен со входом синхронизации регистра запросов, выходы элементов И первой группы соединены с первым управляющим входом исполнительного микропроцессорного устройства, второй управляющий вход и второй и гретий управляющие выходы которого соединены соответственно со вторым управляющим выходом и с первым управляющим входом микропроцессорного блока распределения ресурсов и со входами первой группы разрядов регистра запросов, вы" ходы последнего разряда первой груп пы разрядов и последнего разряда второй группы разрядов регистра запросов блока коммутации соединены 51с первыми входами соответственно второго элемента ИЛИ и первого элемента ИЛИ первой группы блока коммутации, первые входы остальных элементов ИЛИ первой группы соединены с выходами оставшихся разрядов первои группы регистра запросов, первые и вторые входы элементов И первой группы блока коммутации соединены соответственно с выходами разрядов первой группы регистра запросов и через элементы НЕ первой группы - с выходами элементов ИЛИ первой группы, выход каждого предыдущего элемента ИЛИ первой группы блока коммутации соединен со вторым входом последующего элемента ИЛИ первой группы, а выход последнего элемента ИЛИ первой группы соединен со вторым входом второго элемента ИЛИ блока коммутации, выход которого соединен со вторым входом первого элемента ИЛИ и через второй элемент НЕ- со вторым входом элемента И блока коммутации, третий управляющий выход и второй управляющий вход микропроцессорного блока распределения ресурсов соединены соответственно со входом и выходом второго разряда регистра запросов, в управляющее микропроцессорное устройство дополнительно введены микропроцессорный блок создания процесса, микропроцессорный блок уничтожения процесса, микропроцессорный блок передачи сообщения, микропроцессорный блок приема сообщения, два управляющих регистра, семь элементов ИЛИ, а в блок коммутации введены вторые группы элементов ИЛИ, элементов НЕ и элементов И, причем первые управляющие входы и выходы, вторые управляющие выходы, адресные выходы и информационые входы-выходы микропроцессорных блоков создания процесса, уничтожения процесса, передачи сообщения, приема сообщения соединены соответственно с выходом второй группы элементов И, со входом второй группы разрядов регистра запросов, с управляющим входом, через шину адреса с адресным входом и через шину данных с информационным входом-выходом запоминающего устройства, первый и второй управляющие входы и второй и третий управляющие выходы микропроцессорного блока синхронизации соединены соответственно с выходом второй группы элементов И, с выходом первого элемента ИЛИ управ 907551907551 Заказ 592/58ВНИИПИ Государстпо делам изобр113035, Москва,ираж 732 Подписноенного комитета СССРтений и открытий-35, Раушская наб., д. 4/5 илиал ППП "Патент", г, Ужгорор, ул. Проектна Составитель Аедоницкийедактор В, Лазаренко. Техред М.Рейвес Корректор Г. Огаляющего микропроцессорного устройства, с входом второй группы разрядов регистра запросов, с входом первого регистра, третий и четвертый управляющие выходы и второй и третий управляющие входы микропроцессорного блока создания процесса соединены соответственно с первыми входами первого и второго элементов ИЛИ управляющего микропроцессорного устройства с выходом третьего элемента ИЛИ и с первым выходом первого регистра, второй, третий, четвертый и пятый выходы которого соединены соответственно с третьим управляющим входом микропроцессорного блока распределения ресурсов, с первыми входами четвертого и.пятого элементов ИЛИ, с вторым управляющим входом микропроцессорного блока уничтожения процесса, третий управляющий вход, третий, четвертый, пятый, шестой, седьмой управляющие выходы которого соединены соответственно с первым выходом второго регистра, с первым управляющим входом микропроцессорного блока распределения ресурсов, с вторым входом второго элемента ИЛИ управляющего микропроцессорного устройства, с первыми входами третьего и шестого элементов ИЛИ, с вторым входом первого элемента ИЛИ управляющего микропроцессорного устройства, третий вход которого соединен с вторым выходом второго регистра, вход, третий, четвертый и пятый выходы которого соединены соответственно с четвертым управляющим выходом микропроцессорного блока распределения ресурсов, вторыми входами третьего и шестого элементов ИЛИ, с первым входом седьмого элемента ИЛИ, второй вход которого соединен с третьим управляющим выходом микропроцессорного блока передачи сообщения, второй и третий управляющие входы, четвертый, пятый и шестой управляющие выходы которого соединены соответст" венно с выходами четвертого и шестого элементов ИЛИ, с третьим входом второго элемента ИЛИ управляющего микропроцессорного устройства, с четвертым входом первого элемента ИЛИ управляющего микропроцессорного устройства, с вторым входом пятого элемента ИЛИ, выход которого соединен с вторым управляющим входом микропроцессорного блока приема со 10 15 второй группы, выходы остальных разрядов второй группы регистра запросов соединены с первыми входами оставшихся элементов И второй группы и с первыми входами элементов ИЛИ второй группы, вторые входы элементов И .второй группы соединены с выходами соответствующих элементов НЕ второй группы, вход первого элемента НЕ второй группы соединен с выходом второго разряда регистра запросов, входы остальных элементов НЕ второй группы соединены с выходами соответствующих элементов ИЛИ второй группы, выход каждого предыдущего элемента ИЛИ второй группы соединен с вторым входом последующего элемента ИЛИ второй группы, выход последнего элемента ИЛИ второй группы соединен с вторым входом первого элемента ИЛИ первой группы,На фиг. 1 показана блок-схема мультимикропроцессорной системы; на фиг. 2 - блок-схема исполнительного микропроцессорного устройства; на фиг, 3 - структура микропроцессорного блока; на фиг,- структура микропроцессорного узла; на фиг. 5 структура узла прерывания микропроцессорного блока; на фиг, 6 - блоксхема запоминающего устройства; на фиг. 7 " структура блока памяти запоминающего устройства; на фиг.8- структура блока коммутации; на фиг,9- блок-схема устройства связи с памятью) на фиг.10 - структура блока управления устройства связи с памятью; на фиг. 11 - структура блока регист" ров устройства связи с памятью;на. фиг. 12-блок-схема уп ра вляющего микропроцессорного устройства. го 25 Зо.35 40 45 50 55 общения, третий управляющий вход,третий, четвертый, пятый, шестой иседьмой управляющие выходы которогосоединены соответственно с выходом седьмого элемента ИЛИ, с третьими входами третьего и шестого элементов ИЛИ, с вторым входом четвертого элемента ИЛИ, с пятым входом первогои с четвертым входом второго элементов ИЛИ управляющего микропроцессорного устройства, выход второго ,элемента ИЛИ управляющего микропроцессорного устройства соединен с четвертым управляющим входом микропроцессорного блока распределенияресурсов, выход последнего разряда второй группы регистра запросов соединен .с первым входом элемента И25 7 9075Система содержит исполнительноемикропроцессорное устройство 1, запоминающее устройство 2 блок 3 коммутации, микропроцессорный блок 4распределения ресурсов, микропроцессорный блок 5 ввода-вывода, устройство 6 связи с памятью, управляющеемикропроцессорное устройство 7.Исполнительное микропроцессорноеустройство 1 предназначено для обработки пользовательских и системных процессов.Запоминающее устройство 2 предназначено для хранения программ пользователей и программ операционнойсистемы, оформленных в виде поль"зовательских и системных процессов,для хранения системных таблиц, списков и семафоров синхронизации, атакже для накопления результатов 20выполнения.Блок 3 коммутации предназначендля организации приоритетного доступа блоков системы к запоминающемуустройству 2,Микропроцессорный блок 4 распределения ресурсов предназначен дляназначения процессов исполнительному микропроцессорному устройству 1.Микропроцессорный блок 5 ввода-вы вода предназначен для управления операциями ввода-вывода информации.Устройство 6 связи с памятью предназначено для организации режимапрямого доступа при обмене массивами данных между запоминающим устройством 2 и внешними устройствами (наФиг. 1 не показаны).Управляющее микропроцессорноеустройство 7 предназначено для выполнения Функций системных примитивов.Первые управляющие выходы, ин"Формационные входы-выходы и адресные выходы исполнительного микропроцессорного устройства 1, микропроцессорного блока 4 распределения ресурсов, микропроцессорного блока 5ввода-вывода, устройства 6 связи спамятью и управляющего микропроцес 50сорного устройства 7 связаны соответственно с управляющим входом, через шину 8 данных с информационнымивходом-выходом и через шину 9 адреса с адресным входом запоминающегоустройства 2. Третьи управляющие55выходы исполнительного микропроцессорного устройства 1 и микропроцес"сорного блока 4 распределения песувсов, микропроцессорного блока 5 ввода-вывода и управляющего микропроцессорного устройства 7 соединенысоответственно линиями 10-13 с первым-четвертым входами блока 3 комму"тации, а их управляющие входы связаны соответственно линиями 14-17 спервым-четвертым выходами блока 3коммутации.Исполнительное микропроцессорноеустройство 1 содержит исполнительные микропроцессорные блоки 18.1-:18.п и регистр 19 (фиг,2).Исполнительные микропроцессорные блоки 18,1-, 18.п предназначеныдля выполнения команд обрабатываемыхпользовательских и системных процессов,Регистр 19 предназначен для приема и хранения кодов прерываний исполнительных микропроцессорных блоков 18.1-18,п,Исполнительный микропроцессорныйблок 18.К содержит группу микропроцессорных узлов 20.1-.20,8, регистр21 адреса микрокоманд, узел 22 памяти микрокоманд, регистр 23 микрокоманд, узел 24 прерывания, регистр25 расширения (Фиг.3).Микропроцессорные узлы 20,1-:20,8предназначены для выполнения арифметических и логических операций,а также операций сдвигов и переносов,Регистр 21 адреса микрокоманд предназначен для формирования адресамикрокоманды, следующей за исполняемой, а также для стробирования узла24 прерывания по входу 26.Узел 22 памяти микрокоманд предназначен для хранения и выдачи микро- команд и содержит матрицу запоминающих элементов. В узле 22 памяти микрокоманд каждого исполнительного микропроцессорного блока 18.1-18.п за" писана микропрограмма обработки об" ращения к ядру операционной системы, обработки прерывания от микропроцессорного блока 4 распределения ресурсов и интерпретации принятой системы команд,Регистр 23 микрокоманд предназначен для приема кодов микрокоманд из узла 22 памяти микрокоманд и формирования управляющих сигналов во все узлы исполнительного микропроцессорного блока 18.К.907551 30 Узел 24 прерывания предназначендля приоритетного выбора запросов напрерывание и идентификации источника прерывания,Регистр 25 расширения предназнацен для занесения, хранения и выдачиадреса блоков памяти запоминающегоустройства 2.Микропроцессорный узел 20.1 представляет собой двухразрядную процессорную секцию и содержит регистр27 адреса памяти, накапливающий регистр 28, операционный элемент 29,дешифратор 30, первый коммутатор 31,второй коммутатор 32, элемент 33 памяти, первый выходной буфер 34, второй выходной буфер 35 ( фиг. Ц,Регистр 27 адреса памяти предназначен для формирования и хранения адреса при обращении к запоминающему 70устройству 2,Накапливающий регистр 28 предназначен для запоминания результатовопераций операционного элемента 29и содержит два триггера. 75Операционный элемент 29 предназначен для выполнения арифметическихи логических операций и содержитгруппу логических элементов И, ИЛИ,НЕ.Дешифратор 30 предназначен дляпреобразования состояния поля функций микрокоманд в последовательностьсигналов управления элементами микропроцессорного узла 20.1,35Первый и второй коммутаторы 31 и32 предназначены для коммутации сигналов на входах операционного элемента 29.Элемента 33 памяти предназначен 4 Одля временного хранения результатовопераций, выполняемых операционнымэлементом 29, и содержит группу двухразрядных регистров.Первый выходной буфер 34 предназначен для подклюцения выхода регистра 27 адреса памяти к адресной шине9 и содержит группу логических элементов.Второй выходной буфер 35 предназначен для подключения выхода накапливающего регистра 28 к шине 8 данных и содержит группу логических элементов. Узел 24 прерывания содержит шифратор 36, регистр 37 текущего приоритета, элемент 38 сравнения, регистр 39 запросов (фиг.5). 10Шифратор 36 предназначен для формирования кода прерывания и выработки сигнала подтверждения прерыванияРегистр 37 текущего приоритетапредназначен для хранения кода приоритета выполняемой программы,Элемент 38 сравнения предназначендля сравнения кода текущего приоритета и кода запроса на прерывание.Реги стр 39 запросов предназначендля хранения запросов от источниковпрерывания,Запоминающее устройство 2 содержит дешифратор 40 адреса блока памяти и группу блоков 41.1-;41.в памяти (фиг.6).Дешифратор 40 адреса блока памяти предназначен для преобразованиякода адреса блока памяти в сигналызапуска блоков памяти,Блоки памяти 41,1-,41.щ предназначены для записи, хранения и считывания информации.Блок 41 памяти содержит дешифратор 42, первый триггер 43, элементИ 44, второй триггер 45, первый, второй, третий и четвертый элементы 4649 задержки, группу запоминающихэлементов 50 ( фиг.7).Дешифратор 42 предназначен дляпреобразования кода адреса в сигналы выборки запоминающих элементов,Первый триггер 43 предназначендля формирования сигнала "Хранение",Второй триггер 45 предназначендля формирования сигнала "Запись/Чтение" для группы запоминающих элементов 50,Группа запоминающих элементов 50предназначена для хранения информации и представляет собой матрицу полупроводниковых кристаллов.Блок 3 коммутации содержит первуюгруппу элементов И 51,1.-51.п, элемент И 52, вторую группу элементовИ 53,153.5, первую группу инверторов 54,1-:54.п, первый инвертор 55,вторую группу инверторов 56,1-56,5,второй инвертор 57, первую группуэлементов ИЛИ 58.1-58,п, первыйэлемент ИЛИ 59, вторую группу элементов ИЛИ 60.1-.60.4, второй эле"мент ИЛИ 61, регистр 62 запросов(фиг.8).Регистр 62 запросов предназначендля приема и хранения запросов наобращение к общей памяти,Первый, второй, третий и цетвертыйыходы блока 3 коммутации подключенысоответственно к выходам первой группы элементов И 51,1;51.п, через линии 14.1 г 14.п к старшему разряду регистра 62 запросов, к выходу элемента И 52 и через линии 17.1-, 17,5 к вы ходам второй группы элементов И 53.1-, 53.5. Первые входы пеовой группы элементов И 51.1 т 51,п, элемента И 52 и второй группы элементов И 53.1 т 53,5 соединены соответственно с выходами 0 первой группы инверторов 54.1-.54,п, с выходом первого инвертора 55 и с выходами второй группы инверторов 56.1-, "56 5 Число элементов И 51.1-, 51 п 52.53.1 т 53,5, число инверторов 15 54.1 т 54.п; 55,56.1"56.5 и число элементов ИЛИ 58.1 58.п; 59,60.1-,60,4, 61 на единицу меньше числа разрядов регистра 62 запросов. Каждый разряд регистра 62 запросов, кроме старшего 20 разряда, связан со вторым входом соответствующего элемента И 51.1-,51.п;5253.1-53.5 и с первым входом соответствующего элемента ИЛИ 58,1-,58.п;59,60.1-60.4, 61,Старший разряд регистра 62 запросов подключен ко входу инвертора 56.1 и ко второму входу элемента ИЛИ 60.1, Выход элемента ИЛИ 58,1 первой группы соединен со входом инвертора 54. первой группы 30 и со вторым входом элемента ИЛИ 58,п.Выход элемента ИЛИ 58, связан со вторым входом первого элемента ИЛИ 59, выход которого подключен ко входу первого инвертора 55 и ко второму входу второго элемента ИЛИ 61. Выход элемента ИЛИ 60.1 соединен со входом инвертора 56, 1+1 и со вторым входом элемента ИЛИ 60. 1+1. Выход элемента ИЛИ 60.4 подключен ко второму вхо ду элемента ИЛИ 58,1, Выход второго элемента ИЛИ 61 связан через второйинвертор 57 с управляющим входом регистра 62 запросов, установочные входы которого подключены соответствен но к первому входу через линии 10.1 т10,п ко второму входу, к третьему входу и через линии 13. 1-,13.5 к четвертому входу блока 3 коммутации. Синхронизирующий вход регистра 62 за просов по линии 26 соединен с выходом генератора синхросигнагов (на фиг.8 не показан).Структура микропроцессорного блока 4 распределения ресурсов и микро 55 процессорного блока 5 ввода-вывода аналогична структуре исполнит"льного микропроцессорного блока 18.К, представленной на фиг,3, В узле 22 памяти микрокоманд микропроцессорногоблока 4 распределения ресурсов записана микропрограмма, выполняющая системные функции регулировщика, назначающего процессы для обработки висполнительном микропроцессорном устройстве 1, а также микропрограммаобработки прерываний от исполнительного микропроцессорного устройстваи управляющего микропроцессорногоустройства 7, В узле 22 памяти микрокоманд микропроцессорного блока 5ввода-вывода записана микропрограмма,реализующая операции ввода-вывода,а также микропрограмма обработкипрерываний от устройства 6 связи спамятью.Устройство 6 связи с памятью содержит счетчик 63 адреса записисчетчик 64 длины записи, регистр 65режима работы, коммутатор 66, блок67 регистров, блок 68 управления,переключатель 69, регистр 70 запросов, шифратор 71, буферный узел 72фиг.9).Счетчик 63 адреса записи предназначен для хранения и модификации адресов передаваемых данных.Счетчик 64 длины записи предназначен для хранения и модификации кодов длины передаваемых записей.Регистр 65 режима работы предназначен для указания направления передачи данных.Коммутатор бб предназначен дляпередачи данных, поступающих с шины8 данных, пь двум направлениям,Блок 67 регистров предназначендля хранения, записи и чтения адресов записей, кодов длин записей икодов режимов передачи.Блок 68 управления предназначендля формирования временной последовательности сигналов управления узлами устройства 6 связи с памятью.Переключатель 69 предназначендля переключения сигналов на входеблока 67 регистров и содержит логические элементы И, ИЛИ, НЕ.Регистр 70 запросов предназначендля записи и хранения запросов напрерывание от внешних устройствпо входу 73.шифратор 71 предназначен дляидентификации источников запросовна прерывание. Выход 74 устройства6 связи соединен с внешними устройствами,длительной системы 13, З 07Блок 68 управления содержит первый триггер 75, первый элемент И 76, первый элемент ИЛИ 77, второй элемент И 78, второй триггер 79, третий элемент И 80, дешифратор 81, счетчик 82, второй элемент ИЛИ 83 (Фиг.10).Первый триггер 75 предназначен для Формирования сигнала разрешения режима "Передача".Второй триггер 79 предназначен 10 для формирования сигнала разрешения режима "Программирование канала".Дешифратор 81 предназначен для формирования сигнала "Чтение", "Запись" "+1", Сброс", 35Счетчик 82 предназначен для формирования последовательности кодов управления.Блок 67 регистров содержит первый, второй и третий дешифраторы 84- 2 о 86, первую группу регистров 87,1-: 87.8 и вторую группу регистров 88. 1-: 88.8 (Фиг,11).Дешифраторы 84-86 предназначены для преобразования кодов адресов ре гистров в сигналы "Чтение", "Запись" "Сброс".Первая группа регистров 87.1-:87,8 предназначена для хранения адресов записей. 30Вторая группа регистров 88, 1-.88.8 предназначена для хранения кодов длин записей.Управляющее микропроцессорное устройство 7 содержит микропроцессорныйЭ 5 блок 89 синхронизации, микропроцессорный блок 90 создания процесса, микропроцессорный блок 91 уничтожения процесса, микропроцессорный блок 92 передачи сообщения, микропроцес" сорный блок 93 приема сообщения, пер" вый регистр 94, второй регистр 95, первый - седьмой элементы ИЛИ 96102 (фиг.12).Микропроцессорный блок 89 синхро 45 низации .предназначен для синхронизации микропроцессорных блоков 4, 9 О-. 93 при обращении к системным сема" форам. Структура микропроцессорного блока 89 синхронизации аналогична структуре исполнительного микропро 50 цессорного блока 18.К, представлен" ной на фиг.3. В узле 22 памяти микрокоманд микропроцессорного блока 89 синхронизации записана микропрограмма просмотра .указателей системных 55 семафоров по сигналам прерываний.Микропроцессорный блок 90 созда.ния процесса, микропроцессорный 551 блок 91 уничтожения процесса, микро процессорный блок 92 передачи сообщения. и микропроцессорный блок 93 приема сообщения предназначены соответственно для выполнения системных функций по созданию и уничтожениюпроцессов, по передаче и приему сообщений. Их структуры аналогичныструктуре исполнительного микропроцессорного блока 18.К, представленной на Фиг.3. В узле 22 памяти микрокоманд каждого микропроцессорногоблока 90-;93 записаны микропрограмма обработки прерываний и микропрограмма соответствующего системного примитива.Первый 94 и второй 95 регистры предназначены для приема и хранения кодов причин прерываний,Система работает следуоцим образом.Иультимикропроцессорная система обрабатывает как независимые последовательные задания, так и задания алгоритмы выполнения которых допускают распараллеливание. Обработказаданий выполняется в пакетном режиме с мультипрограммированием под управлением операционной системы. В мультимикропроцессорных системах, работающих в режиме мультипрограмиирования мультиобработки, в данный период времени на обслуживании находится пакет заданий, каждое из которых представлено совокупностью процессов. Понятие процесса в качестве основной единицы обработки), используется в вычислительной технике как необходимое средство представления задач,. выполняемых одновременно и параллельно и конкурирующих друг с другом при обращении к общим ресурсам внутри вычис" Процесс " это часть задания (или задание) пользователя, образующая независимую ветвь и выполняемая паралмлько с другими ветвями (процес" сами) этого задания и других заданий. Процесс включает в себя операторы пользователя, области сохранения информации при прерываниях и управляющую информацию для связи с другими процессами, Управляющая информация, представляющая достаточнуюавтономность процессу, оформляетсяв виде таблицы управления процессом15 9075 трех возможных состояний: активности (процессу выделен процессор и его программы выполняются в данный момент), готовности (процесс готов к . выполнению, но ожидает освобождения одного из процессоров) и блокировки (процесс ожидает наступления некоторого события, например сообщения от другого процесса ). Управление процессами в мультимикропроцессорных 10 системах осуществляется ядром операционной системы ( ОС), которое включает в себя следующие компоненты, планировщик нижнего уровня (регулировщик) средства создания уничто Б жения процессов в системе, средства общения процессов, средства синхронизации процессов, Регулировщик обес" печивает параллельность выполнения процессов в системе, учет состояний 20 всех процессов в системе, изменение состояний процессов выбор готовых процессов и назначение им процессороа. Средства создания / уничтожения процессов используются для оформле ния заданий и независимых частей заданий в виде процессов, а также для вывода выполненных процессов из контура обслуживания, Средства общения процессов обеспечивают возможность зо обмена сообщениями между процессами. Средства создания/ уничтожения и об" щения процессов являются системными примитивами, входящими в ядро ОС и реализующими взаимодействие пользо 35 вателя с управляющими программами ОС, Средства синхронизации обеспечивают координацию процессов при обращении к общим 6 есурсам системы (например, Р и Ч - операции над семафорами). Структура мультимикропроцессорной системы в значительной степени определяется ра:пределением функций ядра ЛС по управлению процессами между45 модулями системы. В системе Функции системных примитивов выполняются микропроцессорными блоками управляющего микропроцессорного устройства 7.При управлении процессами в систе-ме используются следующие системные указатели и семафоры, размещенные в запоминающем устройстве 2:УКАЗ СОСТ образуют список указателей состояний исполнительных микропроцессорных блоков 18,1-;18.п и используются для индикации состояний этих блоков при обращении к ним мик" 51 16ропроцессорного блока 1 распределения ресурсов, Кроме того, каждьйуказатель состояния содержит адресТУП процесса, выполняемого в данныймомент на этом исполнительном микропроцессорном блоке;СЛЕДУЮЦИЙ является указателем процесса, который должен быть назначенпервым иэ готовых процессов на освободившийся исполнительный микропроцессорный блокУКАЗ ПАМ является указателем адреса первой зоны свооодной памяти всписке свободных зон памяти;УКАЗ СПИСКА является указателемадреса первой ТУП в общем списке процессов (ОБИ СПИСОК);СЕМ ОБЦ СПИСКА используется длясинхронизации блоков управляющего микропроцессорного устройства 7 и микропроцессорного блока 4 распределения ресурсов при обращении к ОБЩСПИСКУ;СЕМ ПЯМ (семафор памяти) исполь"зуется для управления блокированными процессами, ожидающими удовлетворения запросов на память;СЕМ СПИСКА ПАМ (семафор спискасвободных зон памяти) используетсядля синхронизации блоков управляющего микропроцессорного устройства 7при обращении к СПИСКУ ПАМ;СЕМ СПИСКА БЛОК ПЯМ (семафорсписка процессов, блокированных наСЕМ ПАМ) используется для синхронизации блоков управляющего микропроцессорного устройства 7.Средством связи процессов в системе является ТУП, которую образуютследующие составляющие:имя процесса (ИМЯ)указатель следующего процесса вОБЦ СПИСКЕ (СЛЕД ОБЩ);указатель следующего, процесса всписке группы процессов, относящихся к одному заданию (СЛЕД ГРУПП);указатель состояния активностипроцесса (А);указатель состояния готовностипроцесса к выполнению (Г);указатели обращения процесса кмикропроцессорным блокам 90-:93 создания процесса уничтожения процесса,передачи сообщения и приема сообщения (С У, ПЕР, ПР);указатель блокировки процесса наожидании сообщения (БЛОК СООБЩ);указатель блокировки процессана ожидании свободной памяти при10 15 20 25 Зо 40 45 50 55 35 17 9 выполнении микропроцессорным блоком 90 примитива СОЗДАТЬ ПРОЦЕСС(БЛОК ПАМ С);указатель блокировки процесса на ожидании свободной памяти при выполнении микропроцессорным блоком 92 примитива ПЕРЕДАТЬ СООБ 1.",ЕНИЕ (БЛОК ПАМ ПЕР);семафор сообщений процесса (СЕМ СООБЦ);семафор списка сообщений, адресованных данному процессу (СЕМ СПИСКА СООБЩ);указатель адреса следующей ТУП в списке процессов, блокированных на одном семафоре (СЛЕД СЕМ);область сохранения слова состояния и содержимого регистров микропроцессорных блоков (ОБЛ СОХР);область параметров обращения к управляющему микропроцессорному устройству 7 (ПАРАМЕТРЫ).После инициализации операционной системы планировщик заданий, оформленный в виде процесса и являющийся одним из компонентов ОС, назначается на один из исполнительныхмикропроцессорных блоков 18.1-:18,п, например блок 18.1. Далее исполнительный микропроцессорный блок 18. 1 через устройство 6 связи с памятью и микропроцессорный блок 5 ввода"вывода вводит 1 заданий использователей с манитного диска ( не показан ) в проблемную область оперативной памяти. После окончания ввода 1-го задания исполнительный микропроцессорный блок 18.1 выполняет команду обращения к ядру ОС, в результате чего возникает прерывание, обрабатываемое стандартным образом путем смены слова состояния процесса. По коду причины прерывания в ТУП планировщика заданий устанавливается указатель С и переписывается сохраняемая информация, после чего указатель блока 18.1 в списке указателей состояния исполнительных микропроцессорных блоков 18. 1-: 18.п устанавливается в состояние СВОБОДЕН, и через микропроцессорный блок 4 распределения ресурсов происходит обращение к микропроцессорному блоку 90 создания процесса, который оформляет ТУП первого иэ введенных заданий и сообщает микропроцессорному блоку 4 распреде" пения ресурсов о наличии готового к выполнению процесса в системе. После этого возобновляется выполнение пла" 07551 18нировщика заданий на исполнительном компрессорном блоке 18.1.Планировщик заданий повторяет вышеописанный цикл по созданию процессов для каждого иэ 1 загруженных заданий. Параллельно с этим микропроцессорный блок 4 распределения ресурсов выполняет назначение вновь созданных процессов пользователей насвободные исполнительные микропроцессорные блоки 18,1-.18.п,После того, как планировщик заданий закончит 1-ый цикл созданияпроцесса, он выполняет обращение кядру ОС и с помощью микропроцессорного блока 93 приема сообщения переводится в список блокированных наожидании сообщения процессов до появления сообщения об обработке одногоиз введенных в систему заданий,Созданные пользовательские процессы выполняются параллельно на исполнительном микропроцессорном устройстве 1, При этом области оперативной памяти, с которыми работают исполнительные микропроцессорные блоки 18, 1-. 18,п, задаются соответствующими параметрами ТУП. Выполнение команды программы исполнительным микропроцессорным блоком 18.К осуществляется з следующем порядке, В регистре 27 адреса памяти под управлением микрокоманд, поступающих из узла 22 памяти микрокоманд через регистр 23 микрокоманд, устанавливается адрес команды, С двенадцатого выхода регистра 23 микрокоманд на второй управляющий выход исполнительного микропроцессорного блока 18.К подается сигнал "Запрос шин", после чего микропроцессорный блок 18.К переходит в режим "Ожиданием, Появление на первом управляющем входе исполнительного микропроцессорного блока 18.К сигнала "Под" тверждение запроса", поступающего на четвертый управляющий вход регист ра 21 адреса микрокоманд, вызывает считывание микрокоманды, согласно которой на первый и второй управляю" щие входы микропроцессорных узлов 20, 1-, 20.8 подаются сигналы откры" тия первого и второго выходных бу- феров 34 и 35. В результате этого на адресном выходе исполнительного микропроцессорного блока 18.К устанавливается адрес команды, а на первый управляющий выход микропро"

СмотретьЗаявка

2899929, 07.01.1980

ПРЕДПРИЯТИЕ ПЯ М-5339

ЗАБЛОЦКИЙ ВЛАДИМИР НИКОЛАЕВИЧ, ГРЕК ВАСИЛИЙ ВАСИЛЬЕВИЧ, КАРАБАНЬ ДМИТРИЙ ИВАНОВИЧ, СПАССКИЙ ВИКТОР ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 15/16

Метки: мультимикропроцессорная

Опубликовано: 23.02.1982

Код ссылки

<a href="https://patents.su/27-907551-multimikroprocessornaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Мультимикропроцессорная система</a>

Предыдущий патент: Контроллер с переменным приоритетом

Следующий патент: Модель узла для исследования графа

Случайный патент: Двигатель внутреннего сгорания