Сумматор последовательного действия

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 920710

Авторы: Лукашевич, Остафин, Романкевич

Текст

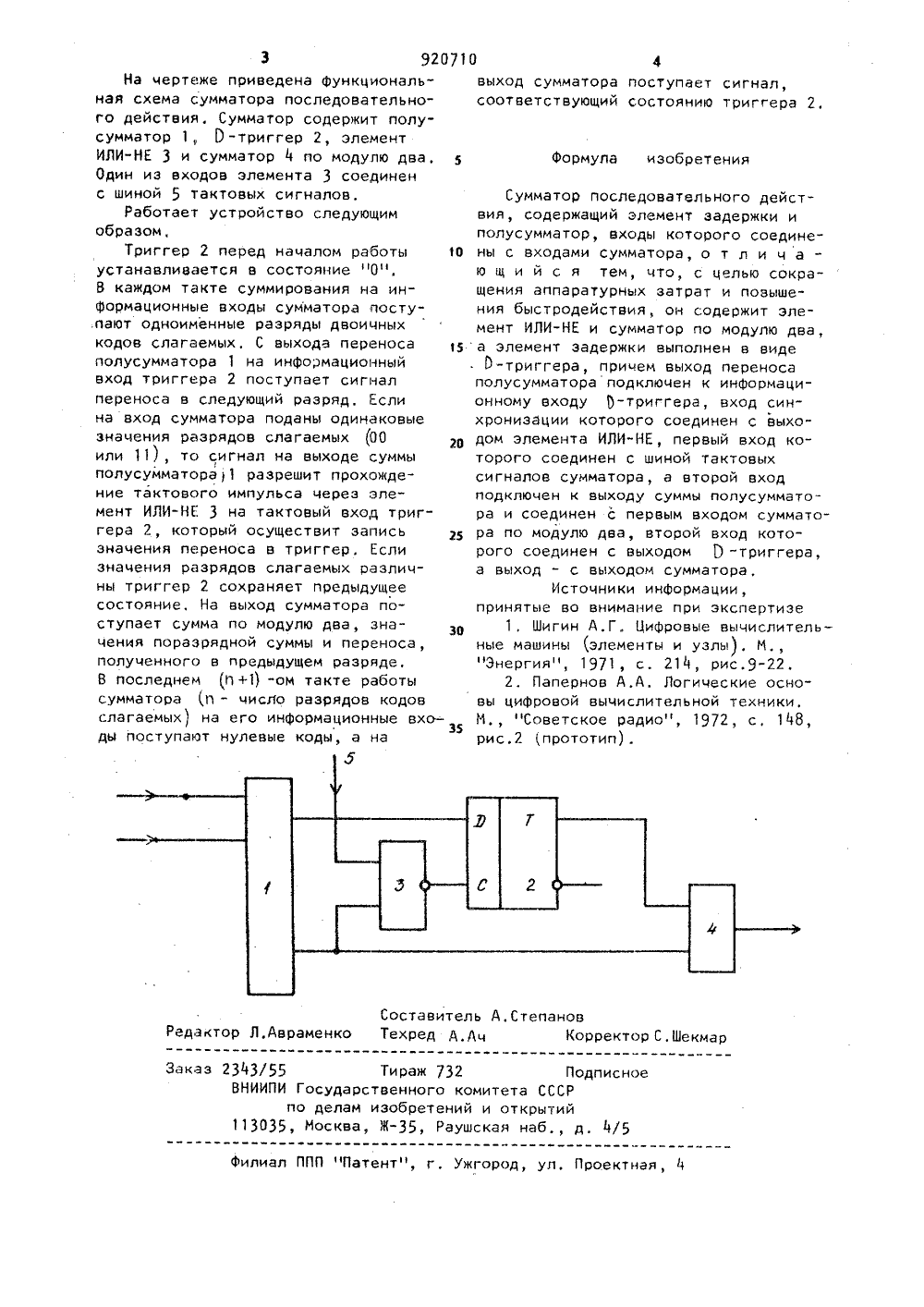

О П И С А Н И Е и 920710ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(22) Заявлено 18. 07, 80 (2 ) 2961845/18-14с присоединением заявк Рй(5 З) УД К 681, 325,5 (088.8) Дата опубликования описания 15, 04 .82 А,М.Романкевич, В,А,Остафин и М.Г,Лукашевич(72) Авторы изобретения сКиевский ордена Ленина политехнический институтим.50-летия Великой Октябрьской социалистическойреволюции(54) СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ Изобретение относится к вычислительной технике и может быть использовано в арифметических устдойствахЭВМ и устройствах обработки цифровойинформации.Известен сумматор последовательного действия, состоящий из двухкомбинационных полусумматоров, двухэлементов задержки и трех элементов И 11,Недостатком его является большойобъем оборудования,Известен также сумматор последовательного действия, содержащий двакомбинационных полусумматора, элемент задержки, элемент И и элементИЛИ 21,Недостатками его являются большойобъем оборудования и низкое быстродействие, так как длительность одного такта сложения в нем определяетсявременем прохождения сигнала черезчетыре уровня логических схем и линию задержки,Цель изобретения - изменениеаппаратурных затрат и повышениебыстродействия сумматора. 5Указанная цель достигается тем,что сумматор последовательного действия, содержащий элемент задержкии пслусумматор, входы которого соединены со входами сумматора, содержиттакже элемент ИЛИ-НЕ и сумматор помодулю два, а элемент задержки выполнен в виде ) -триггера, причемвыход переноса полусумматора подключен к информационному входу О-триггера, вход синхронизации которогосоединен с выходом элемента ИЛИ-НЕгервый вход которого соединен с шиной тактовых сигналов сумматора, авторой вход подключен к выходу суммы 20 полусумматора и соединен а первым входом сумматора по модулю два, второйвход которого соединен с выходомР-триггера, а выход - с выходом сум.Формула изобретения оставител ехред А,А епанов едактор Л.Авраменко ректор С.Шекма аказ 2343/55 ВНИИПИ Госу по де 113035, Мос32 Покомитета СССРний и открытийаушская наб д Тираж рственног м изобрет а, Ж,сн М 5 лиал ППП "Патент", г, Ужгород, ул, Проектна 3 92 О 71На чертеже приведена Функциональная схема сумматора последовательного действия. Сумматор содержит полусумматор 1 0 -триггер 2, элементИЛИ-Нб 3 и сумматор 4 по модулю два.Один из входов элемента 3 соединенс шиной 5 тактовых сигналов.Работает устройство следующимобразом,Триггер 2 перед началом работы 10устанавливается в состояние "0",В каждом такте суммирования на информационные входы сумматора посту.пают одноименные разряды двоичныхкодов слагаемых, С выхода переносаполусумматора 1 на информационныйвход триггера 2 поступает сигналпереноса в следующий разряд, Бслина вход сумматора поданы одинаковыезначения разрядов слагаемых (ОО20или 11), то сигнал на выходе суммыполусумматора 11 разрешит прохождение тактового импульса через элемент ИЛИ-НЕ 3 на тактовый вход триггера 2, который осуществит записьзначения переноса в триггер. Еслизначения разрядов слагаемых различны триггер 2 сохраняет предыдущеесостояние, На выход сумматора поступает сумма по модулю два, значения поразрядной суммы и переноса,полученного в предыдущем разряде.В последнем (П +1) -ом такте работысумматора (и - число разрядов кодовслагаемых) на его информационные вхо 35ды поступают нулевые коды, а на выход сумматора поступает сигнал,соответствующий состоянию триггера 2. Сумматор последовательного действия, содержащий элемент задержки иполусумматор, входы которого соединены с входами сумматора, о т л и ч аю щ и й с я тем, что, с целью сокращения аппаратурных затрат и повышения быстродействия, он содержит элемент ИЛИ-НЕ и сумматор по модулю два,а элемент задержки выполнен в виде0 -триггера, причем выход переносаполусумматора подключен к информационному входу О-триггера, вход синхронизации которого соединен с выходом элемента ИЛИ-Н 1, первый вход которого соединен с шиной тактовыхсигналов сумматора, а второй входподключен к выходу суммы полусумматора и соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом Э -триггера,а выход - с выходом сумматора,Источники информации,принятые во внимание при экспертизе1, Шигин А,Г, Цифровые вычислительные машины (элементы и узлы), М"Энергия", 1971, с. 214, рис,9-22.2. Папернов А.А. Логические основы цифровой вычислительной техники.М "Советское радио", 1972, с, 148,рис.2 прототип).

СмотретьЗаявка

2961845, 18.07.1980

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

РОМАНКЕВИЧ АЛЕКСЕЙ МИХАЙЛОВИЧ, ОСТАФИН ВИКТОР АНТОНОВИЧ, ЛУКАШЕВИЧ МИХАИЛ ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: действия, последовательного, сумматор

Опубликовано: 15.04.1982

Код ссылки

<a href="https://patents.su/2-920710-summator-posledovatelnogo-dejjstviya.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор последовательного действия</a>

Предыдущий патент: Устройство для сложения

Следующий патент: Устройство для умножения двух n-разрядных чисел

Случайный патент: Уравновешенный регулирующий клапан