Устройство для умножения двух n-разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 920711

Автор: Стасюк

Текст

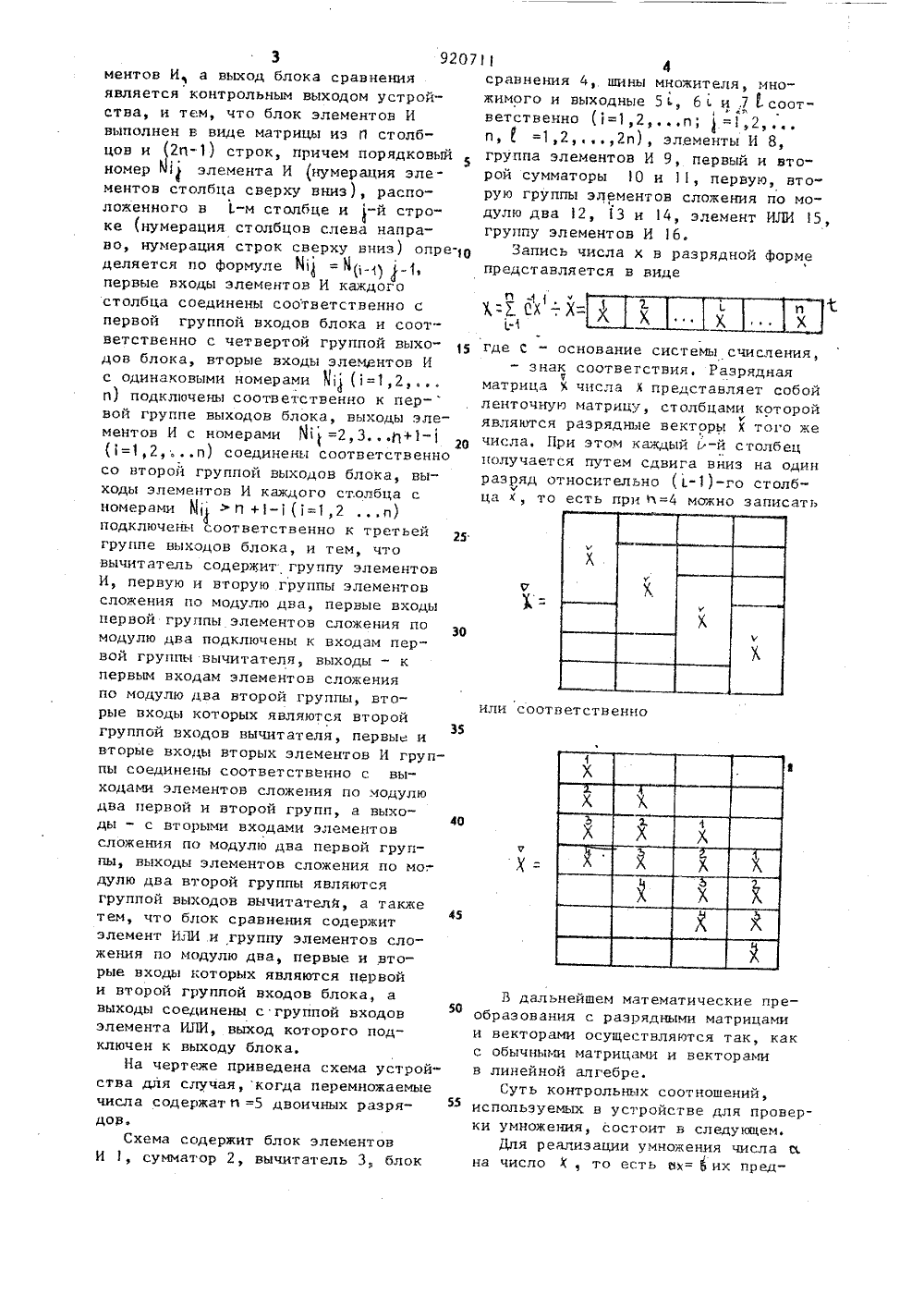

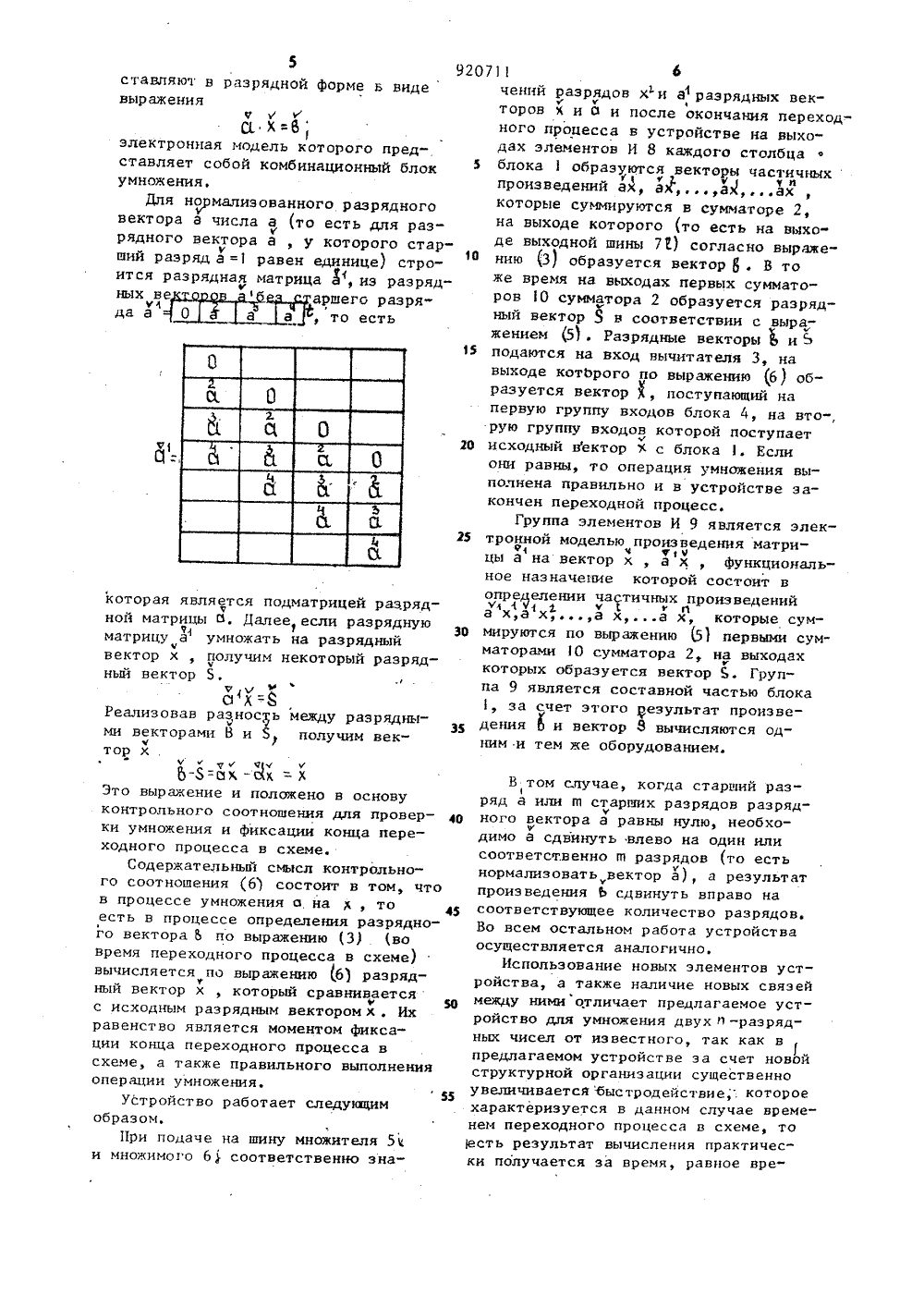

(5 )М, Кл, 6 Об Г 7/52 Гееуавратееный камнтет СССР ае лелем изабретений и аткрцткк(72) Автор изобретения А.И.Стасюк Киевский ордена Трудового Красного Знаме 1 ти институт. инженеров гражданской авиации(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВУХ Д -РАЗРЯДНЫХ ЧИСЕЛИзобретение относится к вычислительной технике и может быть использовано в составе универсальных вычислительных машин или в специализированных вычислительных устройствах,Известно устройство для умножения двух чисел, содержащее регистры множимого и множителя, сдвигающий регистр, сумматоры-вычитатели, счетчик, блок управления и элемент И-НЕ 11 .10 Недостатком устройств является невысокое быстродействие, определяемое тем, что вычислительный процесс в них представляется в виде последовательности шагов, кроме того, из-за невозможности осуществления контроля вычислительного процесса и конечного результата выполнения операции умножения снижается их надежность.Наиболее близким по технической сущности к предлагаемому являетсяустройство ,ля умножения двух И-разрядных чисел, содержащее сумматор Я . Недостатки этого устройства - пониженные быстродействие и надежность,Цель изобретения - повышение быстродействия надежности устройства,Указанная цель достигается тем, что устройство содержит вычитатель, блок сравнения и блок элементов И, первая группа входов которого соединена с шинами множителя, вторая группа входов - с шинами множимого, первая, вторая и третья группы выходов с первой, второй и третьей группами входов сумматора соответственно, первая и вторая группы выходов сумматора подключены соответственно к псрвой и второй группам входов вычитателя и к первой группе выходных шин устройства третья группа выходов сумматора соединена.со второй группой выходных шин устройства, группа выходов вычитателя подключена к первой группе входов блока сравнения, вторая группа входов которого соединена с четвертой группой выходов блока эле92073ментов И 1 а выход блока сравнения является контрольным выходом устройства, и тем, что блок элементов И выполнен в виде матрицы из П столбцов и 2 п) строк, причем порядковый номер Ю элемента И (нумерация элементов столбца сверху вниз), расположенного в 1-м столбце и -й стро" ке (нумерация столбцов слева направо, нумерация строк сверху вниз) опрер деляется по формуле Мц = 1(, )1, первые входы элементов И каждого столбца соединены соответственно с первой группой входов блока и соответственно с четвертой группой выходов блока, вторые входы элементов И с одинаковыми номерами 1 (1,2,.и) подключены соответственно к пер-вой группе выходов блока, выходы элементов И с номерами 11 =2,3 Д+1- (1=1,2,п) соединены соответственно со второй группой выходов блока, выходы элементов И каждого столбца с номерамиП +1-1(1=1,2 и) подключены соответственно к третьей группе выходов блока, и тем, что вычитатель содержит группу элементов И, первую и вторую группы элементов сложения по модулю два, первые входы первой группы элементов сложения по модулю два подключены к входам первой группы вычитателя, выходы - к первым входам элементов сложения но модулю два второй группы, вторые входы которых являются второй35 группсй входов вычитателя, первые и вторые входы вторых элементов И группы соединены соответственно с выходами элементов сложения по модулюде С основание системы счисления, знак соответствияРазрядная7цачислапредставляет собой чнуи матрицу, столбцами которой ются разрядные векторы 1 того жеПри этом каждый -й столбец ается путем сдвига вниз на одинотносительно (Е)-го столбто есть при =4 можно записать лент явля пол и соответственно 11 4сравнения 4, шины множителя, множимого и выходные 5 , би,7 1 соот"ветственно (1=1,2. и=1,2,п,=1,22 п), элементы И 8,группа элементов И 9, первый и вто"рой сумматоры 1 О и 11, первую, вторую группы элементов сложения по модулю два 12, 13 и 14, элемент ИЛИ 15,группу элементов И 16,Запись числа х в разрядной формепредставляется в видеными матрицамияются так, каи векторами Яд екторами ос бычными мат нейной алг цест ицамибре. в ли Сроиь контро ных соотношении стройстве для и ер используемых содержитатор 2,ед два первои и второи групп, а выходы - с вторыми входами элементов сложения по модулю два первой группы, выходы элементов сложения по мо-. дулю два второй группы являются группой выходов вычитателй, а также тем, что блок сравнения содержит элемент ИЛИ .и группу элементов сложения по модулю два, первые и вторые входы которых являются первой и второй группой входов блока, а выходы соединены с группой входов элемента ИЛИ, выход которого подключен к выходу блока,На чертеже приведена схема уст ства для случая, когда перемножаемые числа содержат п =5 двоичных разрядовСхема блок элементов И 1, сумм вычитатель 3, блок ки умножения, состоит в следующ Для реализации умножения чи на число 1, то есть ох= 1 их и9207ставляют в разрядной форме ь видевыражения с 1, х=б;электронная модель которого пред-. ставляет собой комбинационный блок умножения,Для нормализованного разрядного вектора а числа а (то есть для разрядного вектора а, у которого стар 1 О ший разряд а = равен единице) строится разрядная матрица 3, из разрядных ве ариего разрядда а О а а , то есть 15 вед б=С 1 В том случае, когда старший разряд а или щ старших разрядов разрядтного вектора а равны нулю, необходимо а сдвинуть влево на один илисоответственно ш разрядов (то естьнормализовать, вектор а), а результатпроизведения Ь сдвинуть вправо насоответствующее количество разрядов.Во всем остальном работа устройстваосуществляется аналогично,Использование новых элементов устройства, а также наличие новых связей между ними отличает предлагаемое устройство для умножения двух л -разрядных чисел от известного, так как в предлагаемом устройстве за счет новой структурной организации существенно увеличивается:быстродействие,. которое характеризуется в данном случае временем переходного процесса в схеме, то 1 есть результат вычисления практически получается эа время, равное вре 40 45 50 55 и множимо которая является подматрицей разрядной матрицы В, Далее 1 если разрядную матрицу а" умножать на разрядныйчвектор х , получим некоторый разрядный вектор 5,Бк=3Реализовав разность между разрядны 4 У 35 ми векторами В иполучим векчтор х .т Это выражение и положено в основу контрольного соотношения для проверки умножения и фиксации конца переходного процесса в схеме.СодержательньпЪ смысл контрольного соотношения (6 состоит в том, что в процессе умножения о на К, то есть в процессе определения разрядного вектора 6 по выражению (3, (во время переходного процесса в схеме) вычисляется по выражению 16) раэрядтный вектор х , который сравниваетсям с исходным разрядным вектором х . Их равенство является моментом фиксации конца переходного процесса в схеме, а также правильного выполнения операции умножения.Устройство работает следукзцим образом.1 ри пода че на шину множителя 5 6 соответственно эна 1 6ченнй разрядов х" и а 1 разрядных вектторов х и О и после окончания переходного процесса в устройстве на выходах элементов И 8 каждого столбца ф блокаобразуются векторы частичныхт П произведений ах, аха 1,дх которые суммируются в сумматоре 2, на выходе которого (то есть на выходе выходной шины 7 Ц согласно выраже" нию (3) образуется вектор 5 . Б то же время на выходах первых сумматоров О сумматора 2 образуется разрядный вектор Я в соответствии с выражением (5), Разрядные векторы 1 иподаются на вход вычитателя 3, на выходе которого по выражению (6) об" разуется вектор , поступающий на первую группу входов блока 4, на вто-, рую группу входов которой поступает исходный вектор Х с блока . Если они равны, то операция умножения выполнена правильно и в устройстве закончен переходной процесс.Группа элементов И 9 является электронной моделью произведения матрич уцы а на вектор х , а х , функциональное назначение которой состоит в определении частичных произведений ч 1С т аа х,а ха х,а х, которые суммируются по выражению Ь) первыми сумматорами О сумматора 2, на выходах которых образуется вектор ь. Группа 9 является составной частью блока за счет этого результат продения в и вектор 8 вычисляютсяним и тем же оборудованием.920 1меци задержки сигнала между входнымишинами 5 с, 6и выходцой ниной М,кроме тогс, в устройстве осуществляется параллельный контроль вычислений и фиксируется момент окончанияпереходного процесса в схеме, та естьмомент окончания выполнения операции умножения, за счет чего из устройства в этот момент можно считыватьдостоверный результат Ь, а устройство запус:кать на следующий цикл работы. По сути предлагаемое устройство является асинхронньм с возможностью диагностического контроля правильности его функционирования в процессе работы, что споссбствует применению устройства для синтеза системуправления динамическими процессамив реальном масштабе времени технологическими процессами, в системахоперативного управления,формула изобретения1. Устройство для умножения двух И-разрядных чисел, содержащее сумматор,отличающееся тем, чтос нетью повышения быстродействия и надежности устройства, ано содержит вычитатель, блок сравнения и блок элементов И, первая группа входов которого соединена с шинами множителя, вторая группа входов - с шинами мнажимого, перьая, вторая и тре 35 тья группы выходов - с первой, второй и третьей группами входов сумматора соответственно, первая и вторая группы выходов сумматора подключены соответственно к первой и вто 4 О рой группам входов вычитателя и к первой группе выходных шин устройства, третья группа выходов сумматора соединена со второй группой выходных шин устройства, группа выходов вычи 45 тателя подключена к первой группе входов блока сравнения, вторая группа входов которого соединена. с четвертой группой выходов блока элементов И, а выход блока сравнения является контрольным выходом устройства.5 О2. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что блок элементов И выполнен в виде матрицы из й столбцов и 2 пстрок, причем порядковый номер В элемента И (нумерация элементов столбца сверху вниз), расположеннога в 1-столбце 1 8и -строке (нумерация столбцов слева направо, нумерация строк сверлувниз) определяется по формуле 1= М ввпервые входы элементовИ каждого столбца с:оедицецы соответствеццо с первой группой входов блока и соответственно с четвертой группой выходов блока вторые входы элементов И с одинаковыми номерами 1(1=1,2 п) подключеп соответственна к первой группе выходов блока,выходы элементов И с номерами=2,3 п+1-(1=1,2, ,и, соединены соответственно со второй группой выходов блока выходы элементовИ каждого столбца с номерами М 1+1 (=1,2и) падк,почены соответственно к третьей группе выходовблока,3, Устройство па п, 1, о т л ич а ю щ е е с я тем., что вычитательсодержит группу элементов И, первуюи вторую группу элементов сложенияпо модулю два, первые входы первойгруппы элементов сложения по модулюдва подключены к входам первой группы вычитателя, выходы - к первымвходам элементов сложения по модулюдва второй группь 1, вторые входы которых являются второй группой входоввычитателя, первые и вторые ьходывторых элементов И группы соединенысоответственно с. выходами элементовсложения по модулю два первой и второй групп, а выходы - с вторыми входами элементов сложения по модулюдва первой группы, выходы элементовсложения по модулю два второй группы являются группой выходов вычитателя,4. Устройство па п. 1, о т л ич а ю щ е е с я тем, что, блок сравнения содержит :-лемент ИЛИ, группуэлементов сложения по модулю два,первые и вторые входы которых являются первой и второй группой входовблока, а выходы соединены с группой входов элемента ИЛИ, выход которого подключен к выходу блока,Источники информации, принятые во внимание при экспертизе1. Авторское свидетельство СССР 9 651341, кл. С 06 Г 7/39, 1978,2, Авторское свидетельство СССР Ф 623204, кл, 6 06 Г 739, 1978 (прототип).Составитель И,АлексеевРедактор Л.Авраменко Техред А,Бабинец Корректор С.Шек Заказ 2 343/ 32 ЛодписнСР мите открытиишская наб., д, 4/5 иал Л 11 П Латент", г, Ужгород, ул. Проектн Тир НИИ 11 И Госудапо делам иэ 13035, Москв ственногобрет енийЖ, Р

СмотретьЗаявка

2837362, 06.11.1979

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

СТАСЮК АЛЕКСАНДР ИОНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: n-разрядных, двух, умножения, чисел

Опубликовано: 15.04.1982

Код ссылки

<a href="https://patents.su/5-920711-ustrojjstvo-dlya-umnozheniya-dvukh-n-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двух n-разрядных чисел</a>

Предыдущий патент: Сумматор последовательного действия

Следующий патент: Множительно-делительное устройство

Случайный патент: Устройство для повторения информации в дискретных системах связи с переспросом