Преобразователь унитарного кода в сдвиг фазы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 506123

Авторы: Гафиятуллин, Остроумов

Текст

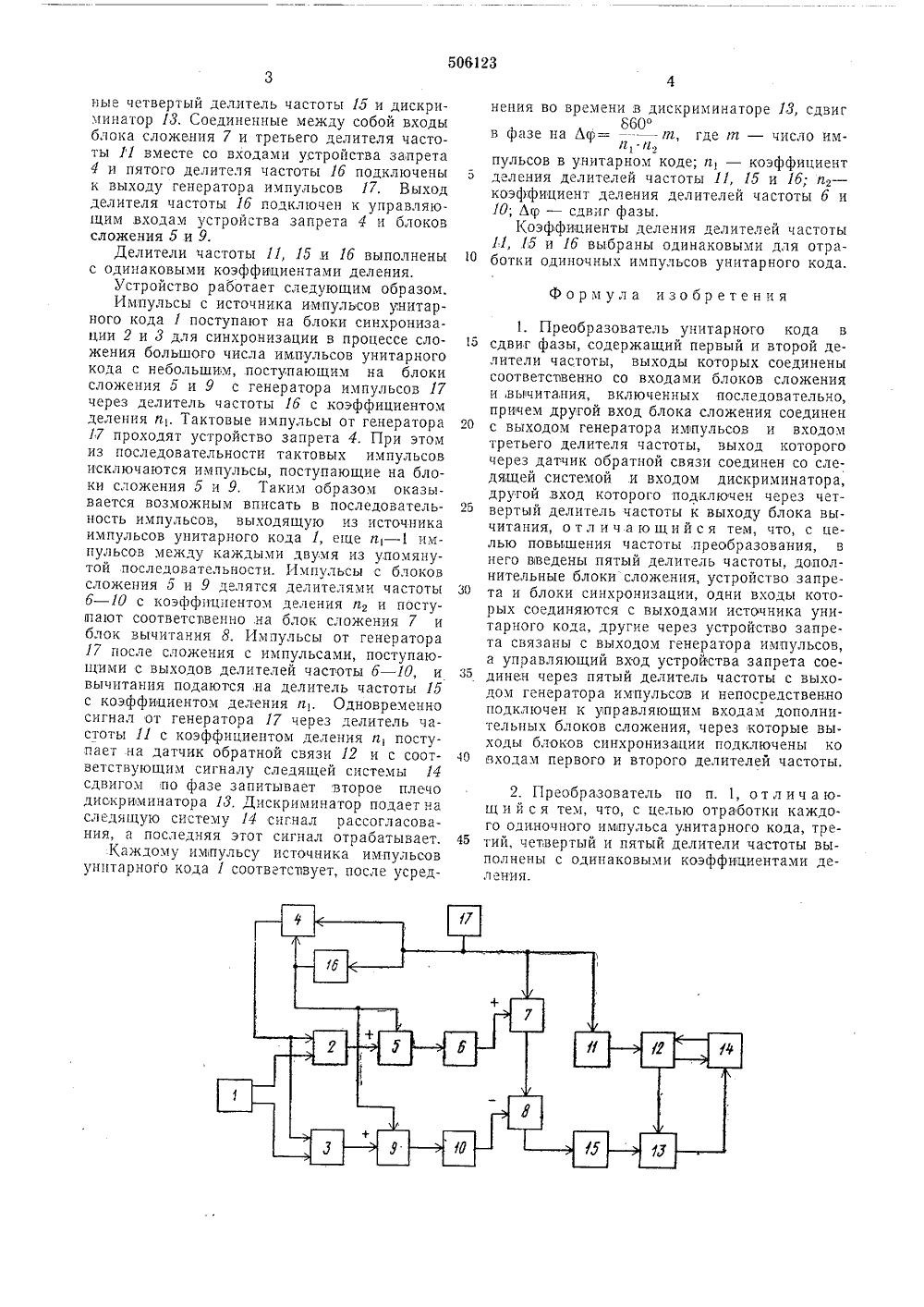

ИЗОБР ЕТЕ Н И Я К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ое к авт свпд 7,74 (2) 2042 ополнител 1 1 хл е Я 03 1( , 3/О 22) Заявлено п 1 тпсоединенпем аявки -23 пор итетвубликовано 05.03,76.:ста опубликования описа(088.8 1 43) ло делам изобретений и открытий(54) ПРЕОБРАЗОВАТЕЛЬ УИИТАРИОГО КО В СДВИГ ФАЗЫб(лох г:,рво Изобретение относится к импульсной технике, может использоваться в станках с программным упразлением.Известен преобразователь унитарного кода з сдвиг фазы, содержащий первый и второй делители частоть 1, выходы которых соединены соответственно со входами блоков сложения и вычитания, включенных последовательно, причем другой вход блока сложениясоединен с выходом генератора импульсов ивходом третьего делителя частоты, выход которого через датчик обратной связи соединенсо следящей системой и входом дискриминатора, другой вход которого подключен черезчетвертый делитель частоты к выходу блокавычитания,Цель изобретения - повышение частотыпреобразования,В предлагаемый преобразователь введеныпятый делитель частоты, дополнительные блоки сложения, устройство запрета и блокисинхронизации, одни входы которых соединяются с выходами источника унитарного кода, другие через устройство запрета связаныс выходом генератора импульсов, а управляющий вход устройства запрета соединенчерез пятый делитель частоты с выходом генератора импульсов и непосредственно подключен к управляющим входам дополнительных блоков сложения, через которые выходы оз синхронизации подключены ко входамго и второго делителей частоты.С целью отработки каждого одиночногоимпульса унитарного кода третий, четвертый и пятый делители частоты выполнены с одинаковь.мп коэффициентами деления.1-1 а чертеже приведена функциональнаясхема преобразователя,Выходы источника унитарного кода 1 под кл 1 очают к первым входам блоков синхронизации 2 и 3, другие входы которых соединены между собой и подключены к выходу устройстза запрста 4. Выход блока синхронизации 2 через дополнительный блок сложения б и первый делитель частоты б подключен ко в.;оду блока сложения 7, выход которого соединен с первым входом блока вычитания 8.Хо второму входу блока вычитания 8 подключен выход блока синхпонизации 3 через "Опоследовательно соединенные дополнительный блок сложения 9 и второй делитель частоты 10, Вход блока сложения 7 соединенсо входом третьего делителя частоты 11, выход которого через датчик обратной связи 12 подключен к первому входу дискриминатора 13 и первому входу следящей системы 14, выход которой подклю (ен ко,второму входу датчика обратной связи 12, Второй вход следящеп системы 14 подключен к выходу блока з 0 вычитания 8 через последовательно соединенные четвертый делитель частоты 15 и дискриминатор 13. Соединенные между собой входы блока сложения 7 и третьего делителя частоты 11 вместе со входами устройства запрета 4 и пятого делителя частоты 1 б подключены з к выходу генератора импульсов 17. Выход делителя частоты 1 б подключен к управляющим входам устройства запрета 4 и блоков сложения 5 и 9.Делители частоты 11, 15 .и 1 б выполнены О с одинаковыми коэффициентами деления.Устройство работает следующим образом.Импульсы с источника импульсов унитарного кода 1 поступают на блоки синхронизации 2 и 3 для синхронизации в процессе сло- гз жения большого числа импульсов унитарного кода с небольшим, поступающим на блоки сложения 5 и 9 с генератора импульсов 17 через делитель частоты 1 б с коэффициентом деления и,. Тактовые импульсы от генератора 20 17 проходят устройство запрета 4. При этом из последовательности тактовых импульсов исключаются импульсы, поступающие на блоки сложения 5 и 9. Таким образом оказывается возможным вписать в последователь ность импульсов, выходящую из источника импульсов унитарного кода 1, еще и, - 1 импульсов между каждыми двумя из упомянутой последовательности. Импульсы с блоков сложения 5 и 9 делятся делителями частоты ЗО б - 10 с коэффициентом деления гг, и поступают соответственно на блок сложения 7 и блок вычитания 8. Импульсы от генератора 17 после сложения с импульсами, поступающими с выходов делителей частоты б - 10, и з 5 вычитания подаются,на делитель частоты 15 с коэффициентом деления а,. Одновременно сигнал от генератора 17 через делитель частоты 11 с коэффициентом деления и, поступает на датчик обратной связи 12 и с соот ветствующим сигналу следящей системы 14 сдвигом по фазе запитывает второе плечо дискриминатора 13, Дискриминатор подает на следящую систему 14 сигнал рассогласования, а последняя этот сигнал отрабатывает. 45Каждому импульсу источника импульсов унитарного кода 1 соответспвует, после усреднения во времени в дискриминаторе 13, сдвигЯ 6 Ов фазе на Лср= -- и, где т - число имгг, ггпульсов в унитарном коде; гг, - коэффициент деления делителей частоты П, 15 и 16; а, - коэффициент деления делителей частоты б и 10; Лр - сдвиг фазы.Коэффициенты деления делителей частоты 11, .15 и 1 б выбраны одинаковыми для отработки одиночных импульсов унитарного кода.Формула изобретения1. Преобразователь унитарного кода в сдвиг фазы, содержащий первый и второй делители частоты, выходы которых соединены соответспвенно со входами блоков сложения и,вычитания, включенных последовательно, причем другой вход блока сложения соединен с выходом генератора импульсов и входом третьего делителя частоты, выход которого через датчик обратной связи соединен со следящей системой и входом дискриминатора, другой вход которого подключен через четвертый делитель частоты к выходу блока вычитания, о тл и ч а ю щий с я тем, что, с целью повышения частоты, преобразования, в него введены пятый делитель частоты, дополнительные блоки сложения, устройство запрета и блоки синхронизации, одни входы которых соединяются с выходами источника унитарного кода, другие через устройство запрета связаны с выходом генератора импульсов, а управляющий вход устройства запрета сое. динен через пятый делитель частоты с выходом генератора импульсов и непосредственно подключен к управляющим входам дополнительных блоков сложения, через которые выходы блоков синхронизации подключены ко входам первого и второго делителей частоты.2. Преобразователь по п. 1, отличающ и й с я тем, что, с целью отработки каждого одиночного импульса унитарного кода, третий, четвертый и пятый делители частоты выполнены с одинаковыми коэффициентами дел ения.

СмотретьЗаявка

2042439, 05.07.1974

ПРЕДПРИЯТИЕ ПЯ Г-4695

ОСТРОУМОВ НИКОЛАЙ КОНСТАНТИНОВИЧ, ГАФИЯТУЛЛИН ЯГИТ НАСРУЛЯННОВИЧ

МПК / Метки

МПК: H03K 13/05

Метки: кода, сдвиг, унитарного, фазы

Опубликовано: 05.03.1976

Код ссылки

<a href="https://patents.su/2-506123-preobrazovatel-unitarnogo-koda-v-sdvig-fazy.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь унитарного кода в сдвиг фазы</a>

Предыдущий патент: Устройство для широтно-импульсной модуляции

Следующий патент: Аппроксиматор дельта-модулятора

Случайный патент: Устройство для умножения двоичных чисел