Блок стробирования считанных сигналов запоминающего устройства

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

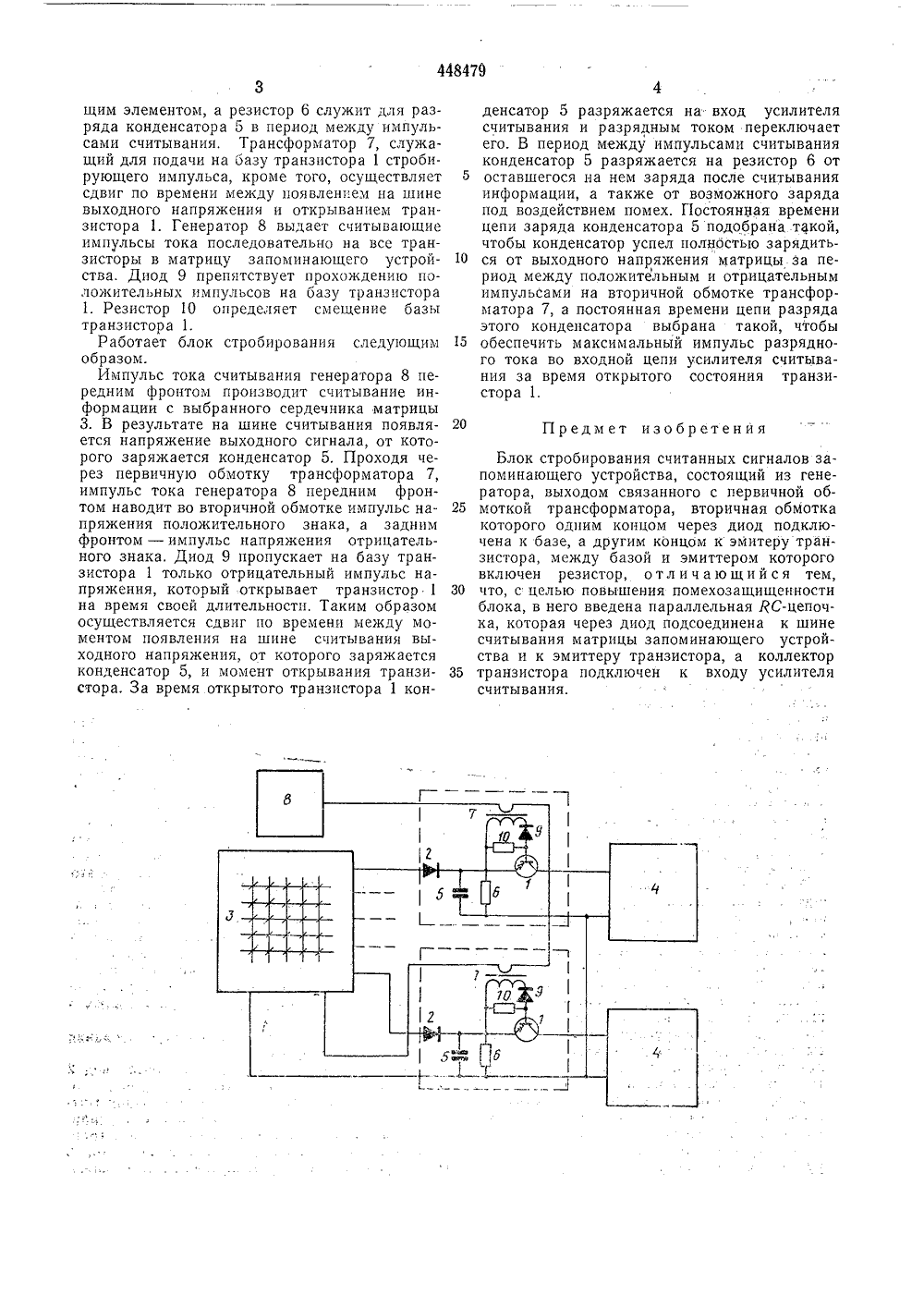

(32) ПриоритетОпубликовано 30,10.74. БюллеДата опубликования описания Комитет по делам изобретений и открытий при Совете Министров СССР(71) Заявитель 54) БЛОК СТРОБИРОВАНИЯ СЧИТАННЫХ СИГНАЛО ЗАПОМИ НАЮ ЩЕГО УСТРО ЯСТВА1Изобретение относится к области вычислительной техники и может быть использовано в запоминающих устройствах электронных вычислительных машин.Известны блоки стробирования считанных сигналов запоминающих устройств, состоящие из генератора, выходом связанного с первичной обмоткой трансформатора, вторичная обмотка которого одним концом через диод подключена к базе транзистора, а другим концом к эмиттеру транзистора, между базой и эмиттером которого включен резистор.В условиях интенсивных помех, действующих по цепи питания, эти блоки стробирования работают ненадежно. Например, при совместной работе ферромагнитных запоминающих устройств и электромагнитных реле, питающихся от общего источника, реле создают импульсные помехи как на выходе усилителей считывания, так и в цепях питания. Усиленные усилителями считывания помехи поступают на входы стробирующих ключей, а импульсы помехи, действующие синхронно по цепи питания, открывают эти ключи. Через открытые ключи помехи поступают в выходные устройств, вызывая их ложные срабатывание, Кроме того, при сравнительно малой длительности выходных сигналов матрицы запоминающего устройства момент открывания стробирующих ключей не удается синхронизовать с моментом появления сигнала на шине считывания. В результате происходит частичная передача сигнала в выходные устройства. Прн этом чувствительность выходных устройств приходится увеличивать, что ухудшает их помехоустойчивость. Для перекрытия временного диапазона между открытым состоянием стробирующих ключей и длительностью выходных сигналов матрицы запоминающего уст ройства необходимо стробирующие импульсыподавать на входы ключей с опережением считывания и увеличивать их длительность, а это приводит к снижению помехоустойчивости.Цель изобрения - повышение помехоустой чивости блока стробирования считанных сигналов, что достигается за счет введения в него параллельной ЯС-цепочки, которая через диод подсоединена к шине считывания матрицы запоминающего устройства и к эмиттеру тран зистора, а коллектор транзистора подключенк входу усилителя считывания.Схема предлагаемого блока стробированияприведена на чертеже.Транзистор 1 через разделительный диод 2 25 включен коллекторно-эмиттерной цепью последовательно между шиной считывания матрицы 3 запоминающего устройства и усилителем считывания 4. Параллельно входу транзистора включена РС-цепочка, конденсатор 5 30 которой является промежуточным запоминаю 448479щим элементом, а резистор б служит для разряда конденсатора 5 в период между импульсами считывания. Трансформатор 7, служащий для подачи на оазу транзистора 1 стробирующего импульса, кроме того, осуществляет сдвиг по времени между появлением на шине выходного напряжения и открыванием транзистора 1. Генератор 8 выдает считывающие импульсы тока последовательно на все транзисторы в матрицу запоминающего устройства. Диод 9 препятствует прохождению положительных импульсов на базу транзистора 1. Резистор 10 определяет смещение базы тра нзи стор а 1.Работает блок стробирования следуощим образом.Импульс тока считывания генератора 8 передним фронтом производит считывание информации с выбранного сердечника матрицы 3. В результате на шине считывания появляется напряжение выходного сигнала, от которого заряжается конденсатор 5. Проходя через первичную обмотку трансформатора 7, импульс тока генератора 8 передним фронтом наводит во вторичной обмотке импульс напряжения положительного знака, а задним фронтом - импульс напряжения отрицательного знака. Диод 9 пропускает на базу транзистора 1 только отрицательный импульс напряжения, который открывает транзистор 1 на время своей длительности. Таким образом осуществляется сдвиг по времени между моментом появления на шине считывания выходного напряжения, от которого заряжается конденсатор 5, и момент открывания транзистора. За время открытого транзистора 1 конденсатор 5 разряжается на вход усилителя считывания и разрядным током переключает его. В период между импульсами считывания конденсатор 5 разряжается на резистор 6 от5 оставшегося на нем заряда после считыванияинформации, а также от возможного заряда под воздействием помех. Постоянная времени цепи заряда конденсатора 5 подобрана такой, чтобы конденсатор успел полностью зарядить- О ся от выходного напряжения матрицы за период между положительным и отрицательным импульсами на вторичной обмотке трансформатора 7, а постоянная времени цепи разряда этого конденсатора выбрана такой, чтобы 5 обеспечить максимальный импульс разрядного тока во входной цепи усилителя считывания за время открытого состояния транзистора 1.20Предмет изобретенияБлок стробирования считанных сигналов запоминающего устройства, состоящий из генератора, выходом связанного с первичной об моткой трансформатора, вторичная обмоткакоторого одним концом через диод подключена к базе, а другим концом к эмитеру транзистора, между базой и эмиттером которого включен резистор, о т л и ч а ю щ и й с я тем, 30 что, с целью повышения помехозащищенностиблока, в него введена параллельная ЯС-цепочка, которая через диод подсоединена к шине считывания матрицы запоминающего устройства и к эмиттеру транзистора, а коллектор 35 транзистора подключен к входу усилителясчитывания.

СмотретьЗаявка

1769228, 04.04.1972

ПРЕДПРИЯТИЕ ПЯ В-2868

ЕРЕМИН ВЯЧЕСЛАВ ГРИГОРЬЕВИЧ, ЛИБАУЭР АБРАМ НАХМАНОВИЧ, ИВАНОВА ОЛЬГА МИХАЙЛОВНА

МПК / Метки

МПК: G11C 7/22

Метки: блок, запоминающего, сигналов, стробирования, считанных, устройства

Опубликовано: 30.10.1974

Код ссылки

<a href="https://patents.su/2-448479-blok-strobirovaniya-schitannykh-signalov-zapominayushhego-ustrojjstva.html" target="_blank" rel="follow" title="База патентов СССР">Блок стробирования считанных сигналов запоминающего устройства</a>

Предыдущий патент: Устройство для записи на магнитном барабане

Следующий патент: Запоминающее устройство

Случайный патент: Способ получения сополимера