Распределенная система для программного управления технологическими процессами

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

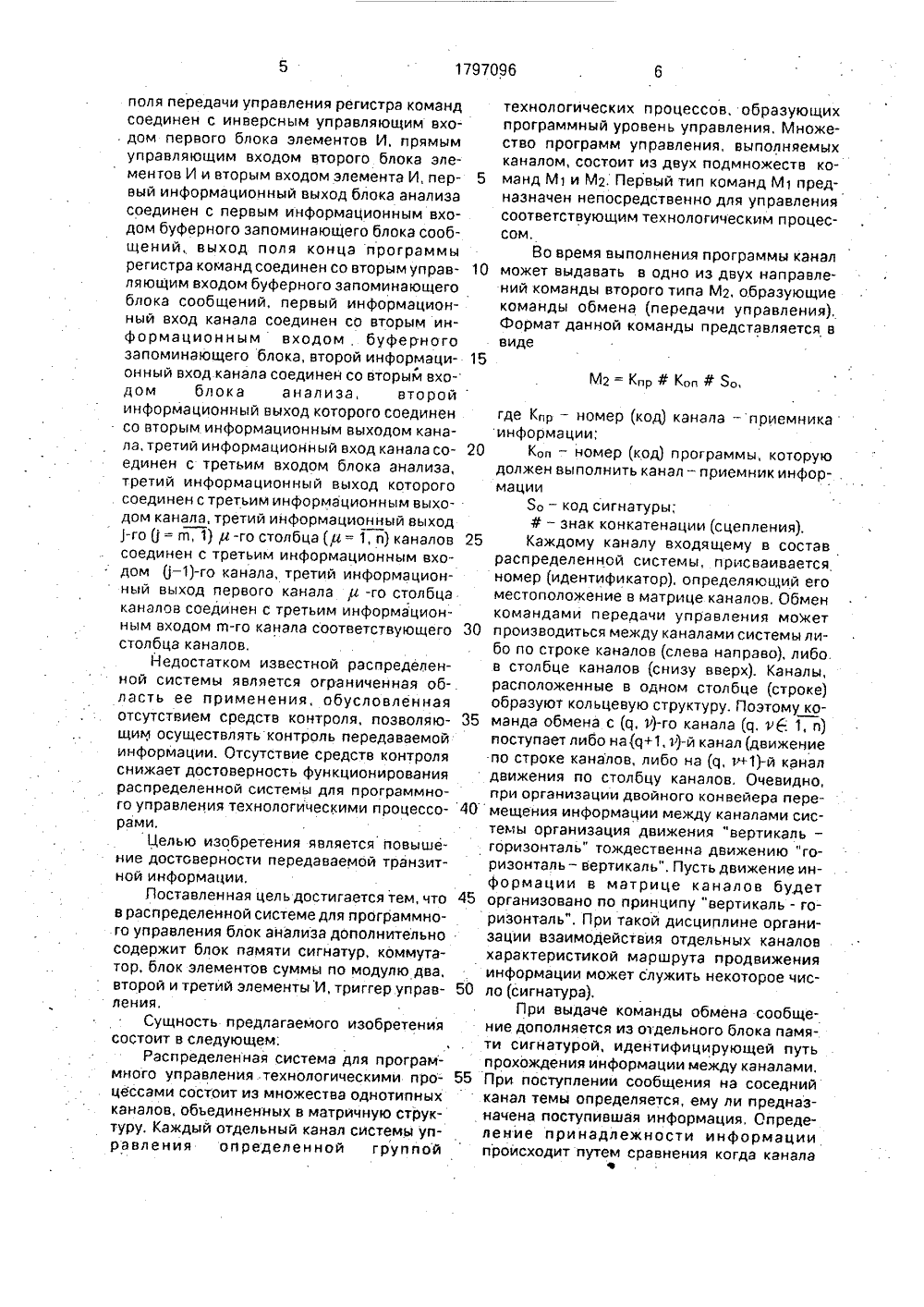

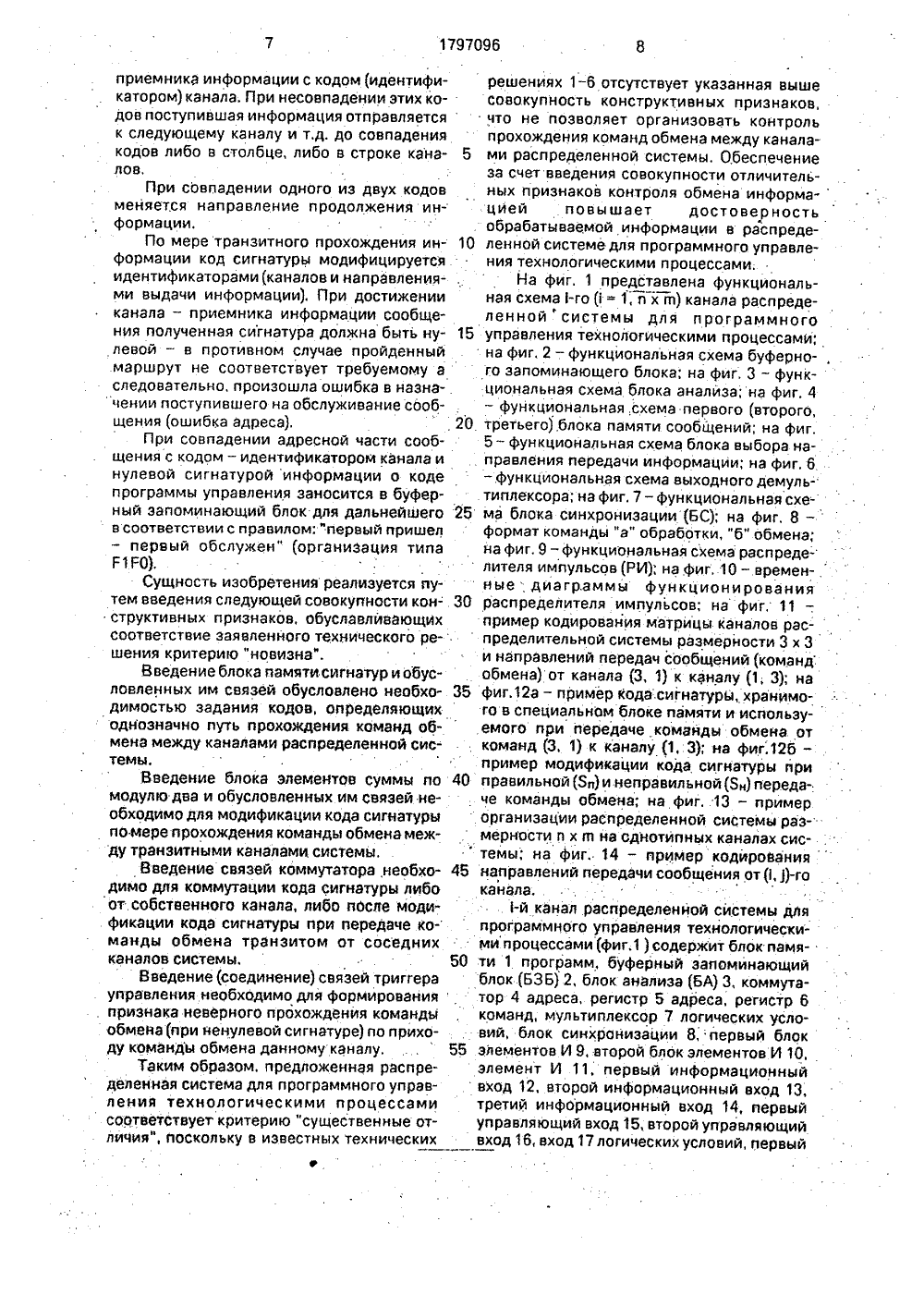

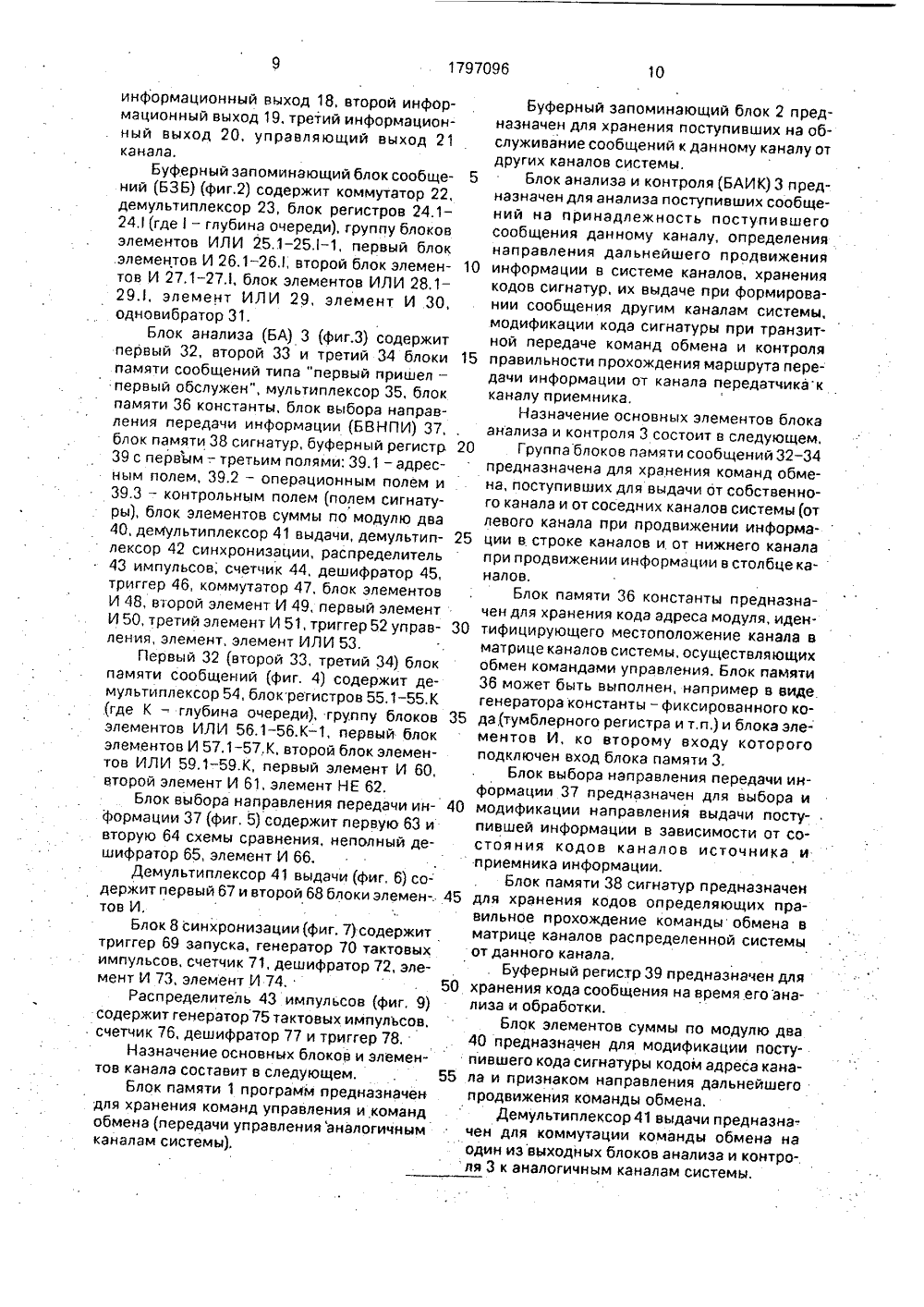

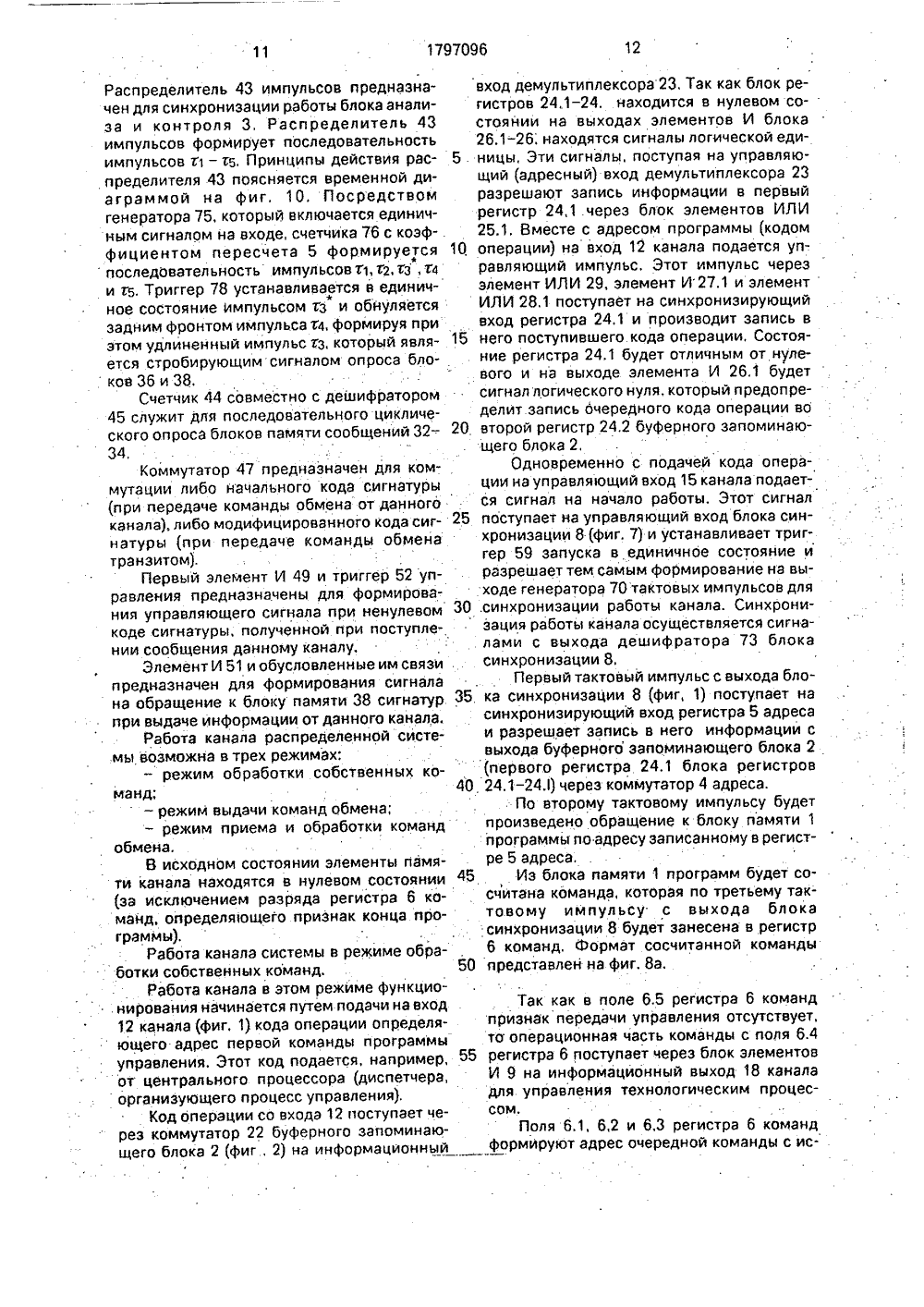

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКРЕСПУБЛИК 096 А 05 В 191 ГОСУДАРСВЕННОЕ ПАТЕНВЕДОМСТВО СССР. Бюл. М 7льников, ВВ,Диго ран ое свидете кл. 606 Р ое свидет кл. 0 05 В(54) РАСПРЕДЕЛЕН ПРОГРАММНОГО УП ЛОГИЧЕСКИМИ ПРО (57) Изобретение отн вычислительной техни меиение в программи станках с числовым и НАЯ СИСТЕМА ДЛ РАВЛЕНИЯ ТЕХН ЦЕССАМИ сится к автоматике ке и может найти пр руемых контроллер рограммным управл Я Ом в блок анаблок памяти ы по модулю пения и два Б иах, еИзобретение относится к автоматике и вычислительной технике и может найти применение в распределенных системах программного управления, программируемых контроллерах, станках с числовым программным управлением, АСУ технологическими процессами.Известно устройство для программного управления, содержащее блок набора программ, задатчик длительности временного интервала, генератор импульсов, три счетчика, блок задержки, регистр сдвига, блок элементов И, формирователь импульсов.Недостатком устройства является сложность модификации программ при изменении функций системы управления, Кроме того, устройство не позволяет выдавать команды управления одновременно по нением, АСУ технологическими процессами. Цель изобретения - надежность системы путем повышения достоверности передаваемой транзитной информации. Распределенная система содержит и х гп каналов (где и и гп - число каналов соответственно в строке и столбце матричной организации системы), а каждый канал содержит блок памяти программ, коммутатор адреса. регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок анализа, два блока элементов И,элемент И, причелиза дополнительно введенысигнатур, блок элементов суммдва, коммутатор, триггер управэлемента И. 1 табл., 14 ил,скольким каналам, что снижает его производительность, а следовательно, ограничивает область применения,Известно устройство для программного управления. содержащее запоминающий блок, процессор, селекторы - демультиплексоры, дешифратор, счетчик, генератор импульсов, блок формирования выходных сигналов, блок элементов И,Недостатком устройства является ограниченная область его применения, обусловленная сложностью модификации программы управления при расширении функций управления и низкой помехоустойчивостью, Отсутствие возможности работы устройства с несколькими обьектами управления снижает производительность системы, приводит к увеличению потребногона инверсный управляющий вход коммутатора вход коммутатора 22 и тем самым запрещается занесение в блок 2 адресапрограммы с выхода блока анализа 3 (фиг.1), 5После обслуживания поступивших наобработку в блоки памяти 32 - 34 сообщений(фиг, 4) на выходе элементов И 62 будутсигналы логического нуля, Эти сигналы навыходе элемента ИЛИ блока анализа 3 (фиг, 103) образуют сигнал логического нуля, который поступает на инверсный вход элементаИ 50 и разрешает тем самым при выдачепоследней команды обмена на соседний канал или данному каналу импульсом с выходараспределителя 43 обнуление триггера 46.На этом анализе и контроль поступившихкоманд обмена завершается,Г 1 аступившие от соседних каналов команды обмена (операционные части - коды .20адресов программ) заносятся с. выхода блока анализа 3 в буферный запоминающийблок 2 (фиг. 2) и обслуживаются по принципу"первым пришел - первым обслужен" аналогично обработке собственных команд. 25После обслуживания (формированиявсего множества программ, адреса которых .были занесены в буферный запоминающийблок 2 (фиг,2) на выходе элемента И 30 образуется сигнал логической единицы поступающий на управляющий вход блока 8синхронизации (фиг. 1), Этот сигнал поступает на вход элемента И 73(фиг, 7) на второйвход которого поступила метка конца выполненной программы с поля 6.8 регистра 356. Триггер запуска 69 устанавливается в нулевое состояние и на этом канал завершаетсвою рабату,Таким образом, в предложенной распределенной системе для программного управления технологическими процессамиосуществляется контроль прохождения информации, что позволяет повышать достоверность функционирования системы,Пусть имеется матрица каналов системы размерности М = 3 х 3 (фиг. 11). Пустьнеобходимо передать команду обмена отканала с номером (3.1) к каналу с номером (1,3). В этом случае из блока памяти сигнатур будет сосчитан контрольный код 3 - 50 011001 (фиг, 12 а), При правильном прохождении информации и распределенной сис-теме оставшаяся сигнатура Я = Ял = 000000 (фиг, 12 б), Допустим, что при поступлении информации в канал с номером (2.2) (фиг, 11) 55адресная часть будет изменена (001011) -ф -э(010011). В этом случае произойдет изменение прохождения информации будет передано на канал с номером(2.3), Сообщение будет принято к исполнению и в распределенной системе произойдет искажение формируемой информации. В предлагаемом канале оставшаяся сигнатура 3 = Ян Ф000= 001001 и будет сформирован признак неверного прохождения информации. По данному признаку возможно обращение, например, к диагностической процедуре,Количественно достигаемый выигрыш в достоверности пропуска ошибки,0Д =гт-где 0 - вероятность появления отказа (сбоя) аппаратуры, вызывающего искажение информации;ФР - вероятность обнаружения искажения в предлагаемой системе.При Рм = 0,99 и 0 = 0,001 получаем до = 100, Таким образом, предлагаемой системе имеется возможность на два порядка уменьшить недостоверность обмена информацией в системе, что обуславливает расширение области ее применения,Распределенная система для программного управления технологическими процессами может найти применение в АСУ ТП, построенных на основе модульных структур, где отдельные строки (столбцы) каналов могут быть изготовлены в виде отдельных СБИС. Такая организация систем повышает гибкость и адаптивность системы к внешним условиям (расширению макрофункций системы),ф ар мула и за бр ете н ия Распределенная система для и рограммного управления технологическими процессами, содержащая и х в каналов, где и а, и - число каналов в строке матричной организации системы; а - число строк, причем 1-й канал( =1, и х п) системы содержит блок памяти программ, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блок синхронизации, блок элементов И, элемент И, причем первый управляющий вход канала соединен с первым входом блока синхронизации, первый выход которого соединен с синхронизирующим входом регистра адреса, выход которого соединен с входом блока памяти программ, выход блока памяти программ соединен с информационным входом регистра команд, синхронизирующий вход которого соединен с вторым выходом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с первым информационным входом мультиплексора логических условий. выход модифицируемого разрядаадреса регистра команд соединен с вторым информационным входом мультиплексора логических условий, выход которого соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого.соединен с информационным входом регистра адреса, вход логических условий канала соединен с управляющим входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен с соответствующими входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И; выход которого соединен с первым информационным выходом канала, выход поля конца программы регистра команд соединен с прямым и инверсным управляющими входами коммутатора адреса и вторым входом блока синхронизации, второй управляющий вход канала соединен с третьим входом блока синхронизации, второй информационный выход К-го(К =1, п) канала т й (1, . щ) строки каналов соединен с вторым ин-.формационным входом (К+1)-го канала ю-й строки, второй информационный выход и-го канала Р-й строки соединен с вторым информационным входом первого канала гй строки, кроме того, каждый канал содержит буферный запоминающий блок, блок анализа, второй блок элементов И, причем информационный выход буферного запоминающего блока соединен с вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом второго блока элементов И, выход которого и выход элемента И соединены с первым входомблока анализа, управляющий выход которого соединен с управляющим входом буферного запоминающего блока, управляющий выход которого соединен с четвертым вхо. дом блока синхронизации, третий выход ко. торого соединен с первым входом элементаИ, выход поля передачи управления регист. ра команд соединен с инверсным управляющим входом первого блока элементов И, прямым управляющим входом второго блока элементов И и вторым входом элемента И, первый информационный выход блока анализа соединен с первым информационным входом буферного запоминающего блока, выход поля конца программы регистра команд соединен с вторым управляющим входом буферного запоминающего блока, первый информационный вход канала сое 20 25 30 35 выходом распределителя импульсов, третий40 выход распределителя импульсов соединен 50 55 5 1 О 15 динен с вторым информационным входом буферного запоминающего блока, второй информационный вход канала соединен с вторым входом блока анализа, второй информационный выход которого соединен с вторым информационным выходом канала, третий информационный вход канала соединен с третьим входом блока анализа, третий информационный выход которого - с третьим информационным выходом канала, третий информационный выход /-го 0 = и, 1) канала,и-го столбца (,и =1, и) каналов соединен с третьим информационным входом О)-го канала, третий информационный выход первого канала р -го столбца каналов соединен с третьим информационным вхо-дом а-го канала соответствующего столбца каналов, причем блок анализа содержит первый, второй и третий блоки памяти сообщений, мультиплексор, блок памяти константы, блок выбора направления передачи информации, триггер, буферный регистр, блок элементов И, выходной демультиплексор, демультиплексор синхронизации, дешифратор, счетчик, распределитель импульсов, элемент И и элемент ИЛИ, выход которого соединен с Я-го входом триггера и инверсным входом элемента И, выход которого соединен с В-входом триггера, прямой выход триггера соединен с управляющим входом распределителя импульсов, первый выход которого соединен со счетным входом счетчика, выходы счетчика соединены с входами дешифратора и управляющими входами мультиплексора, выход которого соединен с информационным входом буферного регистра, синхронизирующий вход которого соединен с вторым с входом считывания блока памяти константы, выход которого соединен с первым входом блока выбора направления передачи информации, второй вход которого соединен с выходом адресного поля буферного регистра, выход операционного поля буферного регистра соединен с информационным входом блока элементов И, выход которого соединен с первым информационным выходом блока анализа, выходы адресного и операционного полей буферного регистра соединены с информационным входом выходного демультиплексора, первый и второй выходы которого соединены соответственно с вторым и третьим информационными выходами блока анализа, первый, второй и третий входы которого соединены с информационным и первым управляющим входами соответствующих бло 1797096 24ков памяти сообщений, информационные выходы которых соединены с соответствующими информационными входами мультиплексора, управляющие выходы блоков памяти сообщений соединены с входами элемента ИЛИ, четвертый выход распределителя импульсов соединен с прямым входом элемента И и информационным входом демультиплексора синхронизации, выход которого соединены с соответствующими выходами блока анализа, первый выход блока выбора направления передачи информации соединен с управляющими входами выходного демультиплексора и демультиплексора синхронизации, второй выход блока выбора направления передачи информации соединен с управляющими входами демультиплексара синхронизации и блока элементов И и управляющим выходом блока анализа, пятый выход распределителя импульсов соединен с тактовыми входами первого, второго и третьего блоков памяти сообщений, выходы дешифратора соединены с вторыми управляющими входами соответствующих блоков памяти сообщений, о т л и ч а ю щ а я с я тем, что, с целью повышения надежности системы путем повышения достоверности передаваемой транзитной информации, блок анализа -го канала ( = 1, и х гп) системы содержит блок памяти сигнатур, блок элементов суммы по модулю два, коммутатор, второй и третий элементы И, триггер управления, прямой выход которого соединен с вторым управляющим выходом блока анализа, выход третьего поля буферного регистра соединен с первым входом блока элементов суммы по модулю два и входами второго элемента И, 5 выход которого соединен с инверсным 3 входом триггера управления, первый выход дешифратора соединен с первым входом третьего элемента И и прямым и инверсным управляющими входами коммутатора, вы ход которого соединен с информационным,входом демул ьтиплексора выдачи, выход блока памяти константы соединен с вторым входом блока элементов суммы по модулю два, выход котороо соединен с первым ин формационным входом коммутатора, второй информационный вход которого соединен с выходом блока памяти сигнатур, выход первого поля буферного регистра соединен с информационным входом блока 20 памяти сигнатур, управляющий вход которого соединен с выходом третьего элемента И, второй вход которого соединен с третьим выходом распределителя импульсов, первый выход блока выбора направления пере дачи информации соединен ссинхронизирующим входом триггера управления, второй выход блока выбора направления передачи информации соединен с первым входом блока элементов суммы по 30 модулю два, второй управляющий выходблока анализа соединен с управляющим выходом соответствующего канала и вторым управляющим входом буферного запомина- ющего блока.351797096 0 ПЬИПЬН 06 пюохдониа нсИа сии нелръьиьим =." Россжаениамоэмами ф1797096 г 1= С 1 С Я 000 ЯОа 00 Я ООО.а СОСЯ 01 ООО Я о ОС а О ЯОО 0 ОЯ 0000 Я Оо+С 0 ОО ЯОСОаОЯ оЯ ооо =ооас оо оса+=СООССО сосо. асс фи, 11 СоставитеГехредУ,р Т.Куркова Реда ректор Л,Лиарин Ти ВКНОГ 3035, аз 6 ВНИ ПОдписн 08ЗОбрЕтЕниям и открытРаушская наб., 4/5 И Государ 04 И ОСК сс та ЙО , жтвенно-издательский комбинат " тент", г. Уж ар Я= ССС ООС Я 0 С 001 ЯОСО ОООЯ 01 СС 1 Я ЯС 00 Оат Я о 0101 С Я 000 001 Я со С 1 =Жобьема памяти, что также ограничивает область применения устройства,Известен программируемый контроллер, содержащий блок памяти, регистр адреса, выходные регистры, демультиплек соры, генератор импульсов, блок элементовИ, элементы И, ИЛИ,Недостатком контроллера является избыточность.блока памяти, что снижает егофункциональную надежность.Известна система для программного управления, содержащая каналы, а в каждомканале. - блок памяти; блок проверки условий, регистр адреса, два триггера, два элемента ИЛИ, элемент НЕ,В известной системе взаимодействие. между каналами организованы, но в видекоманд передачи управления в одном направлении, то ограничивает класс обменных взаимодействий и увеличивает классобменных взаимодействий и увеличиваетвремя взаимодействия. Кроме того, недостатком системы является ограниченная область ее применения в структурахконвейерного типа и отсутствие воэможности применения в матричных структурахпрограммного управления, Отмеченные недостатки ограничивают область целесообразного применения,Известна распределенная система дляпрограммного управления, содержащая каналы, блок памяти, шину данных, шину адреса, шину управления, блок элементовИЛИ.Недостатком известной системы является ограниченная пропускная способность, обусловленная строго последовательным режимом работы отдельных каналов. Кроме того, недостатком известного устройства является ограниченное числообменных взаимодействий в системе, построенной по модульному принципу отдельных каналов, что ограничиваетфункциональные возможности, а следовательно, и область целесообразного применения,Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому решению являетсяраспределенная система для программногоуправления технологическими процессами,. содержащая и х ги каналов, где и е- а и -число каналов в строке матричной организации системы, а щ - число строк, причем 1-йканал ( = 1,и х и 1) системы содержит блокпамяти программ, коммутатор адреса, регистр адреса, регистр команд, мультиплексор логических условий, блоксинхронизации, блок элементов И, элементИ, причем первый управляющий выход которого соединен с синхранизирующим входом регистра адреса, выход которого соединен со входом блока памяти программ, выход блока памяти программ соединен с 5 информационным входом регистра команд,синхронизирующий вход которого соединен со вторым входом блока синхронизации, выход поля проверяемых логических условий регистра команд соединен с пер- "0 вым информационным входом мультиплексора логических условий, выход модифицируемого разряда адреса регистра команд соединен со вторьм информационным входом мультиплексором логических 15 условий, выход которого соединен со вхо-дом модифицируемого разряда адреса первого информационного входа коммутатора адреса, выход которого соединен с информационным входом регистра адреса, вход 20 логических условий канала соединен с управляющим мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра команд соединен со входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом блока элементов И, выход которого соединен с первым информационЗ 0 ным выходом канала, выход поля конца программы регистра команд соединен с прямым и инверсным управляющими входами коммутатора адреса и вторым входом блока синхронизации, второй управляющий З 5 вход канала соединен с третьим входом блока синхронизации, второй информационный выход К-го (К " 1; и - 1) канала ъ"й ( у = =1,а) строки каналов соединен со вторым информационным входом (К+1)-го канала ив й строки, второй информационный выход и-го канала ю строки соединен со вторым информационным входом первого канала т- й строки, каждый канал содержит буферный запоминающий блок сообщений, блок ана- "5 лиза, второй блок элементов И, причем информационный выход буферного запоминающего блока соединен со вторым информационным входом коммутатора адреса, выход операционного поля регистра команд соединен с информационным входом второго блока элементов И, выход которого и выход элемента И соединены с первым входом блока анализа, управляющий выход которого соединен с управляющим входом буферного запоминающего блока сообщений, управляющий выход которого соединен с четвертым входом блока синхронизации, третий выход которого соединен с первым входом элемента И, выход51015 М 2 = КпрКопЯо,20 25 30 35 при организации двойного конвейера пере 40 мещения информации между каналами сис 50 55 поля передачи управления регистра командсоединен с инверсным управляющим входом первого блока элементов И, прямымуправляющим входом второго блока элементов И и вторым входом элемента И, первый информационный выход блока анализасоединен с первым информационным входом буферного запоминающего блока сообщений, выход поля конца программырегистра команд соединен со вторым управляющим входом буферного запоминающегоблока сообщений, первый информационный вход канала соединен со вторым информационным входом . буферногозапоминающего блока, второй информационный вход канала соединен со вторым входом блока анализа, второйинформационный выход которого соединенсо вторым информационным выходом канала, третий информационный вход канала соединен с третьим входом блока анализа,третий информационный выход которогосоединен с третьим информационным выходом канала, третий информационный выход)-го О = щ, 1),и-го столбца(,и= 1, и) каналовсоединен с третьим информационным входом О - 1)-го канала, третий информационный выход первого канала р -го столбцаканалов соединен с третьим информационным входом т-го канала соответствующегостолбца каналов,Недостатком известной распределенной системы является ограниченная об-.ласть ее применения, обусловленнаяотсутствием средств контроля, позволяющим осуществлять контроль передаваемойинформации. Отсутствие средств контроляснижает достоверность функционированияраспределенной системы для программного управления технологическими процессорами,Целью изобретения является повышение достоверности передаваемой транзитной информации.Поставленная цель достигается тем, что 4в распределенной системе для программного управления блок анализа дополнительносодержит блок памяти сигнатур, коммутатор. блок элементов суммы по модулю два,второй и третий элементы И, триггер управления.Сущность предлагаемого изобретениясостоит в следующем:Распределенная система для программного управления технологическими процессами состоит из множества однотипныхканалов, обьединенных в матричную структуру, Каждый отдельный канал системы управления определенной группой технологических процессов, образующих программный уровень управления, Множество программ управления, выполняемых каналом, состоит из двух подмножеств команд М 1 и М 2. Первый тип команд М 1 предназначен непосредственно для управления соответствующим технологическим процессом.Во время выполнения программы канал может выдавать в одно из двух направлений команды второго типа М 2, образующие команды обмена (передачи управления), Формат данной команды представляется в виде где Клр - номер (код) канала - приемника информации;К - номер (код) программы, которую должен выполнить канал - приемник инфор- . мацииЯо - код сигнатуры;- знак конкатенации (сцепления).Каждому каналу входящему в состав распределенной системы, присваивается номер (идентификатор), определяющий его местоположение в матрице каналов, Обмен командами передачи управления может производиться между каналами системы либо по строке каналов (слева направо), либо. в столбце каналов (снизу вверх). Каналы, расположенные в одном столбце (строке) образуют кольцевую структуру, Поэтому команда обмена с (ц, Р)-го канала (ц. И-; 1, и) поступает либо на(ц+1, )-й канал (движение по строке каналов, либо на (ц, т+1)-й канал движения по столбцу каналов, Очевидно,темы организация движения "вертикаль -горизонталь" тождественна движению "горизонталь - вертикаль". Пусть движение информации в матрице каналов будет организовано по принципу "вертикаль - горизонталь", При такой дисциплине организации взаимодействия отдельных каналов характеристикой маршрута продвижения информации может служить некоторое число (сигнатура).При выдаче команды обмена сообщение дополняется из отдельного блока памяти сигнатурой, идентифицирующей путь прохождения информации между каналами, При поступлении сообщения на соседний канал темы определяется, ему ли предназначена поступившая информация, Определение принадлежности информации происходит путем сравнения когда каналаФ10 15 20 25 30 40 50 каналов системы приемника информации с кодом (идентификатором) канала. При несовпадении этих кодов поступившая информация отправляется к следующему каналу и т.д, до совпадения кодов либо в столбце, либо в строке каналов,При совпадении одного из двух кодов меняется направление продолжения информации. По мере транзитного прохождения информации код сигнатуры модифицируется идентификаторами (каналов и направлениями выдачи информации). При достижении канала - приемника информации сообщения полученная сигнатура должна быть нулевой - в противном случае пройденный маршрут не соответствует требуемому а следовательно, произошла ошибка в назна"чении поступившего на обслуживание сообщения (ошибка адреса),При совпадении адресной части сообщения с кодом - идентификатором канала и нулевой сигнатурой информации о коде программы управления заносится в буферный запоминающий блок для дальнейшего в соответствии с правилом: "первый пришел - первый обслужен" (организация типа Р 1 Р 0),Сущность изобретения реализуется путем введения следующей совокупности конструктивных признаков, обуславливающих соответствие заявленного технического решения критерию "новизна", Введение блока памяти сигнатур и обусловленных им связей обусловлено неабходимостью задания кодов, определяющих однозначно путь прохождения команд обмена между каналами распределенной системы,введение блока элементов суммы по модулю два и обусловленных им связей необходимо для модификации кода сигнатуры по.мере прохождения команды обмена между транзитными каналами системы. Введение связей коммутатора,необходимо для коммутации кода сигнатуры либо от собственного канала, либо пОсле модификации кода сигнатуры при передаче команды обмена транзитом от соседних Введение (соединение) связей триггерауправления необходимо для формирования признака неверного прохождения команды обмейа (при ненулевой сигнатуре) по приходу команды обмена данному каналу.Таким образом. предложенная распределенная система для программного управлений технологическими процессами соответствует критерию "существенные отличия", поскольку в известных технических решениях 1-6 отсутствует указанная выше совокупность конструктивных признаков, что не позволяет организовать контроль прохождения команд обмена между каналами распределенной системы. Обеспечение за счет введения совокупности отличительных признаков контроля обмена информа-цией повышает достоверность обрабатываемой информации в распределенной системе для программного управления технологическими процессами,На фиг, 1 представлена функциональная схема 1-го ( = 1, и х т) канала распределенной системы для программного управления технологическими процессами; на фиг, 2 - функциональная схема буферно-, го запоминающего блока; на фиг, 3 - функциональная схема блока анализа; на фиг, 4 - функциональная, схема первого (второго, третьего) блока памяти сообщений; на фиг.5 - функциональная схема блока выбора направления передачи информации; на фиг. 6 - функциональная схема выходного демультиплексора; на фиг. 7 - функциональная схема блока синхронизации (БС); на фиг. 8 - формат команды "а" обработки, "б" обмена; на фиг. 9- функциональная схема распределителя импульсов (РИ); на фиг. 10 - времен- . ныедиаграммы функционирования распределителя импульсов; на фиг, 11 - . пример кодирования мэтрйцы каналов распределительной системы размерности 3 х 3 и направлений передач сообщений (команд. обмена) от канала (3, 1) к каналу (1; 3); на фиг.12 а - пример кода. сигнатуры, хранимого в специальном блоке памяти и используемого при передаче команды обмена от команд (3, 1) к каналу (1,.3); на фиг.12 б - пример модификации кода сигнатуры при правильной(Яп) и неправильной(ЯН) передаче команды обмена; на фиг. 13 - пример организации распределенной системы размерности и х гп нв однотипных каналах системы; на фиг, 14 - пример кодирования .направлений передачи сообщения от(3,-го канала.1-й канал распределенной системы для программного управления технологическими процессами (фиг,1 ) содержит блок памяти 1 программ, буферный запоминающий блок (БЗБ) 2, блок анализа (БА) 3, коммутатор 4 адреса, регистр 5 адреса, регистр 6 команд, мультиплексор 7 логических условий, блок синхронизации 8,первый блок элементов И 9, второй блок элементов И 10, элемент И 11, первый информационный вход 12. второй информационный вход 13, третий информационный вход 14, первый управляющий вход 15, второй управляющий вход 16, вход 17 логических условий, первыйинформационный выход 18, второй информационный выход 19, третий информационный выход 20, управляющий выход 21 канала.Буферный запоминающий блок сообщений (БЗБ) (фиг.2) содержит коммутатор 22, демультиплексор 23, блок регистров 24,1 - 24.1(где 1 - глубина очереди), группу блоков элементов ИЛИ 25.1 - 25.1-1, первый блок элементов И 26,1-26,1, второй блок элементов И 27.1 - 27.1, блок элементов ИЛИ 28.1- 29.1, элемент ИЛИ 29, элемент. И 30, одновибратор 31.Блок анализа (БА) 3 (фиг,3) содержит первый 32, второй 33 и третий 34 блоки памяти сообщений типа "первый пришел - первый обслужен", мультиплексор 35, блок памяти 36 константы, блок выбора направления передачи информации (БВНПИ) 37, блок памяти 38 сигнатур, буферный регистр 39 с первым - . третьим полями: 39,1 - адресным полем, 39,2 - операционным полем и 39.3 - контрольным полем (полем сигнатуры), блок элементов суммы по модулю два 40, демультиплексор 41 выдачи, демультиплексор 42 синхронизации, распределитель 43 импульсов, счетчик 44, дешифратор 45, триггер 46, коммутатор 47, блок элементов И 48, второй элемент И 49, первый элемент И 50, третий элемент И 51, триггер 52 управления, элемент, элемент ИЛИ 53.Первый 32 (второй 33, третий 34) блок памяти сообщений (фиг, 4) содержит демультиплексор 54, блок регистров 55,1 - 55.К (где К - глубина очереди), группу блоков элементов ИЛИ 56.1 - 56.К - 1, первый блок элементов И 57.1-57,К, второй блок элементов ИЛИ 59,1 - 59.К, первый элемент И 60, второй элемент И 61, элемент НЕ 62,Блок выбора направления передачи информации 37 (фиг. 5) содержит первую 63 и вторую 64 схемы сравнения, неполный дешифратор 65, элемент И 66.Демультиплексор 41 выдачи (фиг, 6) содержит первый 67 и второй 68 блоки элемен-. тов И.Блок 8 синхронизации (фиг. 7) содержит триггер 69 запуска, генератор 70 тактовых импульсов, счетчик 71, дешифратор 72, элемент И 73, элемент И 74.Распределитель 43 импульсов (фиг. 9) содержит генератор 75 тактовых импульсов. счетчик 76, дешифратор 77 и триггер 78.Назначение основных блоков и элементов канала составит в следующем,Блок памяти 1 программ предназначен для хранения команд управления и команд обмена (передачи управления аналогичным каналам системы).20 Группа блоков памяти сообщений 32-34 предназначена для хранения команд обме 25 30 35 40 от данного канала. Буферный регистр 39 предназначен для50 хранения кода сообщения на время егоанапившего кода сигнатуры кодом адреса кана 55 ла и признаком направления дальнейшего 51015 Буферный запоминающий блок 2 предназначен для хранения поступивших на обслуживание сообщений к данному каналу от других каналов системыБлок анализа и контроля (БАИК) 3 предназначен для анализа поступивших сообщений на принадлежность поступившего сообщения данному каналу, определения направления дальнейшего продвижения информации в системе каналов, хранения кодов сигнатур, их выдаче при формировании сообщения другим каналам системы, модификации кода сигнатуры при транзитной передаче команд обмена и контроля правильности прохождения маршрута передачи информации от канала передатчикак каналу приемника, Назначение основных элементов блока анализа и контроля 3 состоит в следующем на, поступивших для выдачи от собственного канала и от соседних каналов системы(от левого канала при продвижении информации в строке каналов и от нижнего канала при продвижении информации в столбце каналов.Блок памяти 36 константы предназначен для хранения кода адреса модуля, идентифицирующего местоположение канала в матрице каналов системы, осуществляющих обмен командами управления, Блок памяти 36 может быть выполнен, например в виде. генератора константы - фиксированного кода,(тумблерного регистра и т,п.) и блока элементов И, ко второму входу которогоподключен вход блока памяти 3.Блок выбора направления передачи информации 37 предназначен для выбора и модификации направления выдачи поступившей информации в зависимости от состояния кодов каналов источника и приемника информации. Блок памяти 38 сигнатур предназначен для хранения кодов определяющих пра вильное прохождение команды обмена в матрице каналов распределенной системы лиза и обработки. блок элементов суммы по модулю два 40 предназначен для модификации поступродвижения команды обмена. Демультиплексор 41 выдачи предназначен для коммутации команды обмена наодин из выходных блоков анализа и контроля 3 к аналогичным каналам системы, 1797096 12Распределитель 43 импульсов предназначен для синхронизации работы блока анализа и контроля 3, Распределитель 43импульсов формирует последовательностьимпульсов г 1 - г 5, Принципы действия распределителя 43 поясняется временной диаграммой на фиг, 10, Посредствомгенератора 75, который включается единичным сигналом на входе, счетчика 76 с коэф-.фициентом пересчета 5 формируетсяпоследовательность импульсов т 1, г 2, гз, х 4и т 5. Триггер 78 устанавливается в единичное состояние импульсом тз и обнуляетсязадним фронтом импульса т 4, формируя приэтом удлиненный импульс гз, который является стробирующим сигналом опроса блоков 36 и 38,Счетчик 44 совместно с дешифратором45 служит для последовательного циклического опроса блоков памяти сообщений 3234,Коммутатор 47 предназначен для коммутации либо йэчального кода сигнатуры(при передаче команды обмена от данногоканала), либо модифицированного кода сигнатуры (при передаче команды обменатранзитом).Первый элемент И 49 и триггер 52 управления предназначены для формирования управляющего сигнала при ненулевомкоде сигнатуры, полученной при поступлении сообщения данному каналу,Элемент И 51 и обусловленные им связипредназначен для формирования сигналана обращение к блоку памяти 38 сигнатурпри выдаче информации от данного канала,Работа канала распределенной системы возможна в трех режимах;- режим обработки собственных команд;- режим выдачи команд обмена;- режим приема и обработки командобмена.В исходном состоянии элементы памяти канала находятся в нулевом состоянии 4(зэ исключением разряда регистра 6 команд, определяющего признак конца программы),Работа канала системы в режиме обработки собственных команд.Работа канала в этом режиме функцио 10 15 20 25 30 35 40 24.1-244 через коммутатор 4 адреса 50 55 нирования начинается путем подачи на вход 12 канала (фиг. 1) кода операции определяющего адрес первой команды программы управления. Этот код подается, например, от центрального процессора (диспетчера, организующего процесс управления),Код операции со входа 12 поступает через коммутатор 22 буферного запоминающего блока 2 (фиг . 2) на информационный вход демультиплексора 23, Так как блок регистров 24,1-24. находится в нулевом состоянии на выходах элементов И блока 26,1-26; находятся сигналы логической единицы, Эти сигналы, поступая на управляющий (адресный) вход демультиплексора 23 разрешают запись информации в первый регистр 24,1.через блок элементов ИЛИ 25.1, Вместе с адресом программы (кодом операции) на вход 12 канала подается управляющий импульс, Этот импульс через элемент ИЛИ 29, элемент И 27.1 и элемент ИЛИ 28,1 поступает на синхрониэирующий вход регистра 24.1 и производит запись в него поступившего кода операции, Состояние регистра 24.1 будет отличным от нулевого и нэ выходе элемента И 26.1 будет сигнал логического нуля, который предопределит. запись очередного кода операции во второй регистр 24,2 буферного запоминающего блока 2,Одновременно с подачей кода операции на управляющий вход 15 канала подается сигнал на начало работы. Этот сигнал поступает на управляющий вход блока синхронизации 8 (фиг. 7) и устанавливает триггер 59 запуска в единичное состояние й разрешает тем самым формирование на выходе генератора 70 тактовых импульсов для синхронизации работы канала, Синхронизация работы канала осуществляется сигналами с выхода дешифратора 73 блока синхронизации 8. Первый тактовый импульс с выхода блока синхронизации 8 (фиг, 1) поступает на синхронизирующий вход регистра 5 адреса и разрешает запись в него информации с выхода буферного запоминающего блока 2 (первого регистра 24,1 блока регистров По второму тактовому импульсу будетпроизведено обращение к блоку памяти 1 программы по адресу записанному в регистре 5 адреса,Из блока памяти 1 программ будет сосчитана команда, которая по третьему тактовому импульсу с выхода блока синхронизации 8 будет занесена в регистр 6 команд, формат сосчитанной команды представлен на фиг. 8 а,Так как в поле 6.5 регистра 6 команд признак передачи управления отсутствует, то операционная часть команды с поля 6.4 регистра 6 поступает через блок элементов И 9 на информационныи выход 18 канала для. управления технологическим процессом. Поля 6.1, 6,2 и 6,3 регистра 6 команд формйруют адрес очередной команды с использованием мультиплексора 7 логических Работа канала в режиме выдачи командусловий, который предназначен для форми- обмена,рования значения модифицируемого разря- В процессе обработки собственных кода адреса очередной команды и реализует манд канал может выдать команды обменалогическую функцию вида: 5 другим аналогичным каналам образующиму 1 = х 1 а + хгг 1- хзгг ++ хк+1 гк, двунаправленную кольцевую структуру расгде у - выходной сигнал мультиплексора 7 пределенной системы,логических условий; Формат команды обмена (передачи упх 1 - конъюнкция а 1 аг а, соответст- равления) представлен на фиг. 8 б, В этомвующая коду с выхода 6,1 кода логических 10 случае с поля 6.4 регистра 6 команд выдаетусловий, решающему прохождению моди- ся командафицируемого адресного разряда а без изме- п 1 = ппр 4 гпк,нения; где тпр - код (номер) канала приемникахг = а 1 аг аз а информации;хз = а 1 аг аз Й 15 . в - код (номер) программы, которуюх = а 1 аг % а; должен выполнить гп, -й канал системы;конъюнкции соответствующие кодам, опре- Ф - знак конкатенации (сцепления),деляющим прохождение на выход мульти- В свою очередьплексора 7 одного из сигналов логических гппР = щпр ф щпрусловий г, ггг со входа 17 логических 20 где епр - номер канала приемника инфорусловий канала, мации в строке аналогичных каналов;С выдачей последней команды форми- гппр - номер канала приемника инфорруемой программы в поле 6,6 регистра 6 мации в стрельбе аналогичных каналов,заносится метка - признак окончания про- Одновременно с кодом п 1 команды обграммы, Эта метка поступает на управляю 25 мена с выхода поля 6,5 регистра 6 командщий вход коммутатора 4 адреса и разрешает выдается метка - признак передачи управпрохождениечерезнего информации(адре- ления аналогичному каналу, Эта метка поса очередной программы) из буферного за- ступает на управляющие входы блокапоминающего блока 2, Крометого,эта метка элементов И 10 и элемента И 1 (фиг, 1) ипоступает на управляющий вход буферного 30 разрешает тем самым прохождение команзапоминающего блока 2 (фиг.2) и формирует. ды обмена с поля 6,4 регистра 6 через блокпо фронту на выходе одновибратора 31 им- элементов И 10 на информаЦионный входпульс. Этот импульс через элементы ИЛИ блока анализа и контроля 3 (фиг. 3), Одно 28,1-28. поступает на синхронизирующие. временно с командой обмена на этот входвходы блока регистров 24.1-24 Л и осущест поступает с выхода блока синхронизации 8вляет тем самым сдвиг информации.тактовый импульс.Если выполнялась последняя команда, Поступившая команда обмена заноситто очередь поступивших на обслуживание ся в блок приема сообщения (БПС) 32 (фиг,запросов становится пустой (нулевое состо). Так как блок регистров 55.1 - 55.К (где К -яние блока регистров 24.1 - 24,). На выходах 40 глубина очереди) находится в нулевом соэлементов И 26,1 - 26. образуется сигналы стоянии, то на выходах элементов И 57,1 логической единицы, На выходе элемента И. 57.К находятся сигналы логической30 появляется сигнал логической единицы, единицы, Эти сигналы поступают на адрескоторый с выхода буферного запоминающе- ный входдемультиплексора 54 и разрешаютго блока 2 (фиг, 1) поступает на вход блока 45 тем самым запись поступившего сообщениясинхронизации 8(фиг 7). На выходе элемен- в первый регистр очереди 55,1, Состояниета И 73 формируется сигнал логической еди- . этого регистра будет отличным от нулевогоницы, который через элемент ИЛИ 74 и тем самым будет подготовлен для записиустанавливает триггер 69 запуска в нулевое очередного сообщения второй регистр 55,2,состояние и модуль завершает свою работу 50 При записи информации в регистр 55.1 блоЕсли очередь в буферном запоминаю- ка приема сообщения 32 на выходе элеменщем блоке 2 не пуста, то после сдвига ин- та И 62 появляется сигнал логическойформации в блоке регистров 24,1 -24, единицы(фиг,4), который с выхода БПС 32первым тактовым импульсом очередной им- через элемент ИЛИ 53(фиг. 3) устанавливаетпульсной последовательности производит триггер 46 в единичное состояние. Единичся запись информации в регистр 5 адреса и . ное состояние триггера 46 идентифицируетдалее канал функционирует аналогично рас-Разрешение формирования на выходах рассмотрен ному ранее. пределителя импульсов (РИ) 43 импульсовдля синхронизации работы блока анализа 3, 1797096 16Синхронизация работы блока анализа 3 происходит по импульсам, которые формируюгся на первом-пятом выходах распределителя 43 импульсов (фиг,9) и представляют собой пять импульсных последовательностей (фиг,10), Такт (цикл) работы состоит из пяти фаз. Каждая фаза работы блока анализа 3 начинается тактовым импульсом соответствующей импульсной последователь- ности.По первому тактовому импульсу происходит обращение к соответствующему блоку памяти сообщений 32 - 34 путем увеличения содержимого счетчика 44 на единицу,По второму тактовому импульсу производится запись сообщения в буферный регистр 39.По третьему тактовому импульсу происходит обращение к блокам памяти 38 и констант 36,По четвертому тактовому импульсу производится выдача команды обмена либо к соседним каналам системы, либо к данному каналу для ее дальнейшей обработки.По пятому тактовому импульсу производится сдвиг информации в блоке памяти сообщений иэ которого была сосчитана информация для анализа и контроля.Далее такт (цикл) работы блока анализа 3 повторяется путем обращения к очередному блоку памяти сообщений 32-34,Источниками информации для данного блока анализа 3 могут быть: собственно канал системы при передаче сообщения другим каналам системы и соседние каналы, находящиеся в матрице каналов снизу и слева (фиг. 13). В свою очередь, потребителями информации выступают: собственно канал при поступлении сообщения (команды обмена) данному каналу и соединим каналам, находящимся вверху и справа матрицы каналов при передаче сообщений транзитом.Каждому каналу в системе присваивается свой идентификатор - адрес, определяющий местоположение канала (номер строки и номер столбца в матрице системы). Передаваемая информация состоит из трех частей: адресной, операционной и контрольной. Адресная часть представляет собой код адреса канала, которому предназначена данная операционная часть (номер программы). Контрольная часть слова представляет собой код (сигнатуру) однозначно определяющий путь между двумя каналами - передатчиком и приемником информации. По мере подтверждения команды обмена и матрицы каналов проигходит модификация сигнатуры, во-первых, кодом (идентификатором) транзитного канала и, во-вторых, на правлением выдачи информации, При выдаче информации от данного канала она дополняется кодом сигнатуры.Выбор направления передачи информации блоком анализа 3 осуществляется следующим образом,Адресная часть поступившего сообщения сравнивается с адресом (идентификатором) данного канала по нормам строки и столбца и определяется одно из трех возможных направлений передачи (два - на 10 соседние каналы и третье - на обработкуданному каналу) по следующему правилу. кали (строки и столбца) размещения каналов в системе, а С и О - коды адресов канала приемника информации. Процедура выбора направления передачи информации реализуемой блоком 37 определяется табл, 1,В блоке памяти 36 блока анализа 3 (фиг. 20 3) записан код адреса (иДентификатор) (код строки и код столбца) данного канала относительно других каналов в однородной структуре распределенной системы, При занесении информации (команды обмена) в блок памяти сообщений 32 тактовый импульс с выхода распределителя 43(фиг. 3 ) увеличивает содержимое счетчика 44 на единицу, На выходе дешифратора 45 инициатируется единичный сигнал для опроса блока памяти сообщений 32. Код с выхода счетчика 44, поступая на управляющий 30(адресный) вход мультиплексора 35 и разрешает тем самым запись информации по второму импульсу с блока памяти 32 в буферный регистр 39,Считываемая информация из блока пэмя 35 ти 32 сообщений (фиг, 3) состоит из трех частей - адресной, операционной и контрольной, которые заносятся соответственно в поля 39.1, 39.2 и 39.3 буферного регистра 39.Отличие функционирования канала в режиме передачи команды обмена от собственного канала заключается в следующем, . Команда обмена в передаваемом сообщении должна быть дополнена контрольной информацией (сигнатурой) в зависимости от кода (номера) канала приемника информа 50 ции. Все сигнатуры прохождения команд обмена отданного канала записаны в блоке памяти сигнатур 38. В поле 39.3 буферного регистра находится нулевая контрольная информация.Счетчик 44 будет находиться в состоянии, определяющем обращение к блоку памяти сообщений 32. На соответствующем выходе дешифратора 45 будет сигнал логической единицы, Этот сигнал поступает на уп 55 Путь А и В коды адресов канала источ 15 ника информации по горизонтали и верти 17 17970965 10 15 20 25 30 35 40 45 50 55 равляющий вход коммутатора 47 и разрешит прохождение через него информации свыхода блока памяти 38 сигнатур, Очередной импульс тз с выхода распределителя 43поступает на управляющий вход блока памя ти 38 сигнатур и производится считывание изнего информации по адресу, хранимому в поле 39,1 буферного регистра 39,Код сигнатуры с выхода блока памяти 38через коммутатор 47 поступает на информационный вход демультиплексора 41. Кромекода сигнатуры на информационный входдемультиплексора 41 поступает информация о кодах адреса канала приемника информации и адреса программы,Сформированная команда обмена выдаетсяна один из двух выходов блока анализа 3 навыход 19 или 20 к соседним каналам распределенной системы (фиг, 13):Выбор направления передачи командыобмена от данного канала осуществляетсяблоком направления передачи информации(ВВНПИ) 37 (фиг, 3), На основе сравнениядвух кодов адресов каналов на схемах сравнения 63 и 64 (фиг. 5) БВНПИ 37 на выходенеполного дешифратора 65 образуется в соответствии с таблицей 1 признак,, 1, если требуется передать информаР= цию вверх;О, если требуется передать информацию вправо.Сформированный признак направления выдачи информации с выхода БВНПИ37 (фиг.-З) поступает на адресные (управляющие) входы демультиплексоров 41 и 42,Очередной импульс 4 с выхода распределителя 43 через демультиплексор 42 поступаетна соответствующий выход блока анализа 3для синхронизации записи сообщения вблок памяти сообщения 33 (34) соседнегоканала, Далее канал функционирует аналогично описанному,Работа канала в режиме приема и обработки команд обмена.При обработке команды обмена от соседних каналов происходит обращение к соответствующему блоку памяти сообщений33 или 34 блока анализа 3 (фиг. 3). Черезмультиплексор 35 команды обмена заносится в буферный регистр 39. При этом поле39,3 находится код сигнатуры,При передаче информации транзитомкод сигнатуры Я при прохождении каналабудет промодифицирован, во-первых, доком адреса(идентификатором) канала и, вовторых, кодом направления выдачиинформации, Модификация кода сигнатуры,поступающего с выхода поля 39,3 буферного регистра 39, происходит на блоке сверткипо модулю два 40, поступающем признаком направления передачи направления р с выхода БВНПИ 37 и кодом адреса канала с выхода блока памяти 36, Полученная сигнатура с выхода блока элементов суммы по модулю два через коммутатор 47 поступает для дальнейшей ее передачи совместно с адресной и операционной частями команды обмена к соседнему каналу. Далее канал функционирует аналогично описанному ранее, По мере продвижения команды обмена в матрице каналов системы к каналу приемнику информации будет происходить модификация сигнатуры.При совпадении кодов адресов приемника информации с адресной частью команды обмена на выходах "Равно" первой 63 и второй 64 схем сравнения блока 37 (фиг, 5) формируются сигналы логической единицы. На выходе элемента И 66 будет также сигнал логической единицы. Этот с выхода блока 37 выбора направления передачи информации(фиг, 3) поступает на управляющий вход блока элементов И 48 и разрешает тем самым при поступлении импульса с выхода распределителя 43 приложение операционной части (кода адреса программы) с выхода поля 39.2 буферного регистра 39 на выход блока анализа 3 для последующей записи в буферный запоминающий блок 2 (фиг. 1) для дальнейшей обработки данным каналом.Кроме того, управляющий сигнал с выхода блока выбора направления передачи информации 37 поступает на управляющий вход синхронизации триггера 52. На выходы элемента И 49 с нулевых выходов поля 39,3 буферного регистра 39 поступает код сигнатуры. Отсутствие ошибки в прохождении команды обмена в матрице каналов системы будет при Я =000 ; в противном случае маршрут прохождения сообщения будет отличным от запланированного. При нулевой сигнатуре Я =000на выходе элемента И 49 будет сигнал логической единицы, идентифицирующий правильность прохождения команды, обмена, а следовательно, и правильность принадлежности поступившего на обслуживание запроса, Этот сигнал поступает на инверсный Я - вход триггера 52 управления и не изменяет его состояния. При Я Ф 0000 сигнал логического нуля с выхода элемента И 49 (фиг, 3) установит триггер 52 в единичное состояние, На прямом выходе триггера 52 будет сигнал логической единицы, поступающий на выход блока анализа 3 и с его выхода на выход 21 канала и на управляющий вход буферного запоминающего блока 2 (фиг, 1). Этот сигнал поступает на управляющий вход буферного запоминающего блока 2 (фиг, 2) и с его входа

СмотретьЗаявка

4801901, 10.01.1990

ВОЙСКОВАЯ ЧАСТЬ 73790

МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, КОПЫЛОВ ВЛАДИМИР ВЛАДИМИРОВИЧ, СИЛАНТЬЕВ ЮРИЙ НИКИТОВИЧ, ДИГОРАН АЛЕКСАНДР ВАСИЛЬЕВИЧ, ГАЛИЦКИЙ АЛЕКСАНДР ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G05B 19/18

Метки: программного, процессами, распределенная, технологическими

Опубликовано: 23.02.1993

Код ссылки

<a href="https://patents.su/19-1797096-raspredelennaya-sistema-dlya-programmnogo-upravleniya-tekhnologicheskimi-processami.html" target="_blank" rel="follow" title="База патентов СССР">Распределенная система для программного управления технологическими процессами</a>

Предыдущий патент: “устройство для моделирования системы “двигатель-насос”

Следующий патент: Устройство для контроля аналогового сигнала

Случайный патент: Устройство для промывки фотографических отпечатков