Параллельное микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

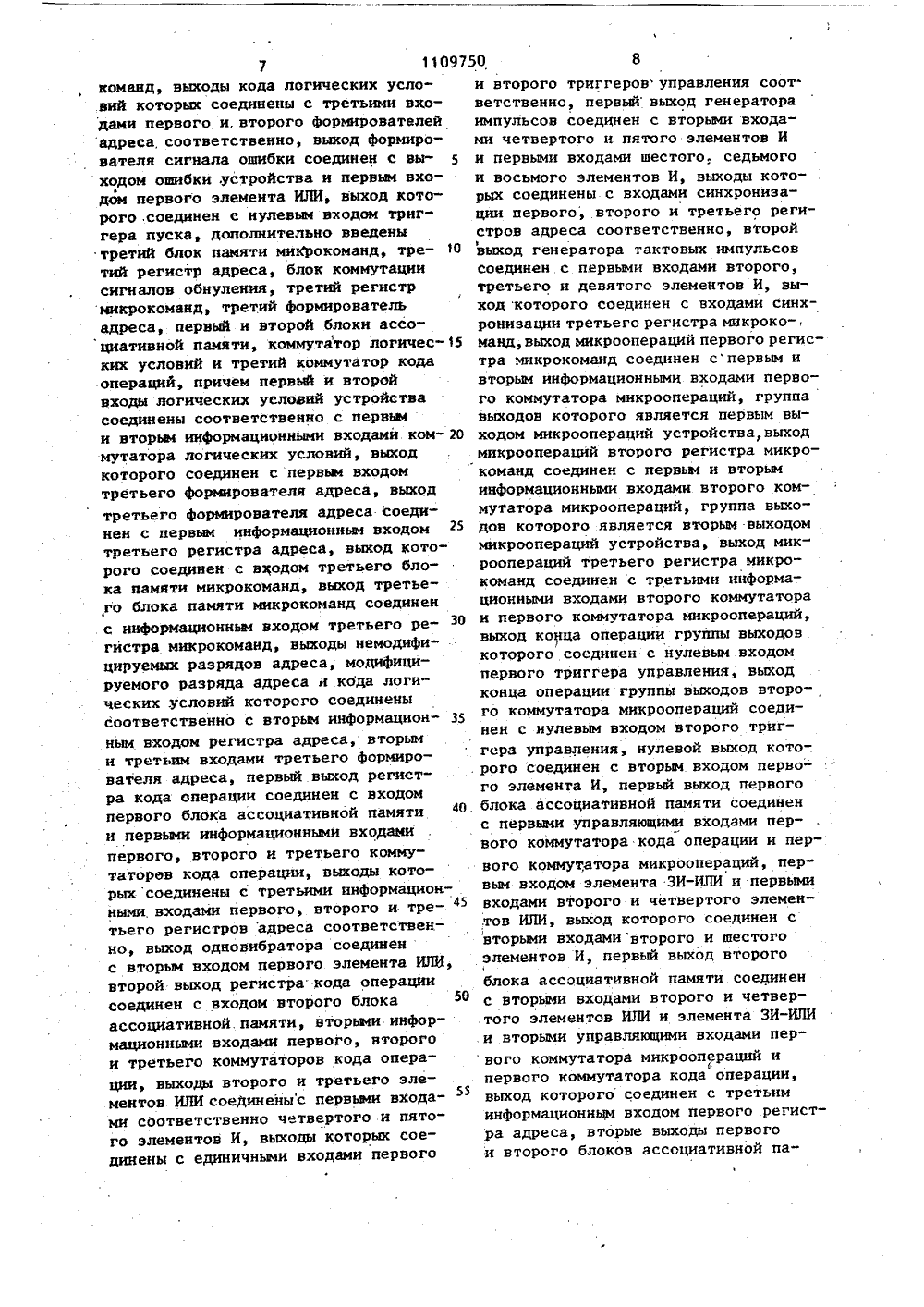

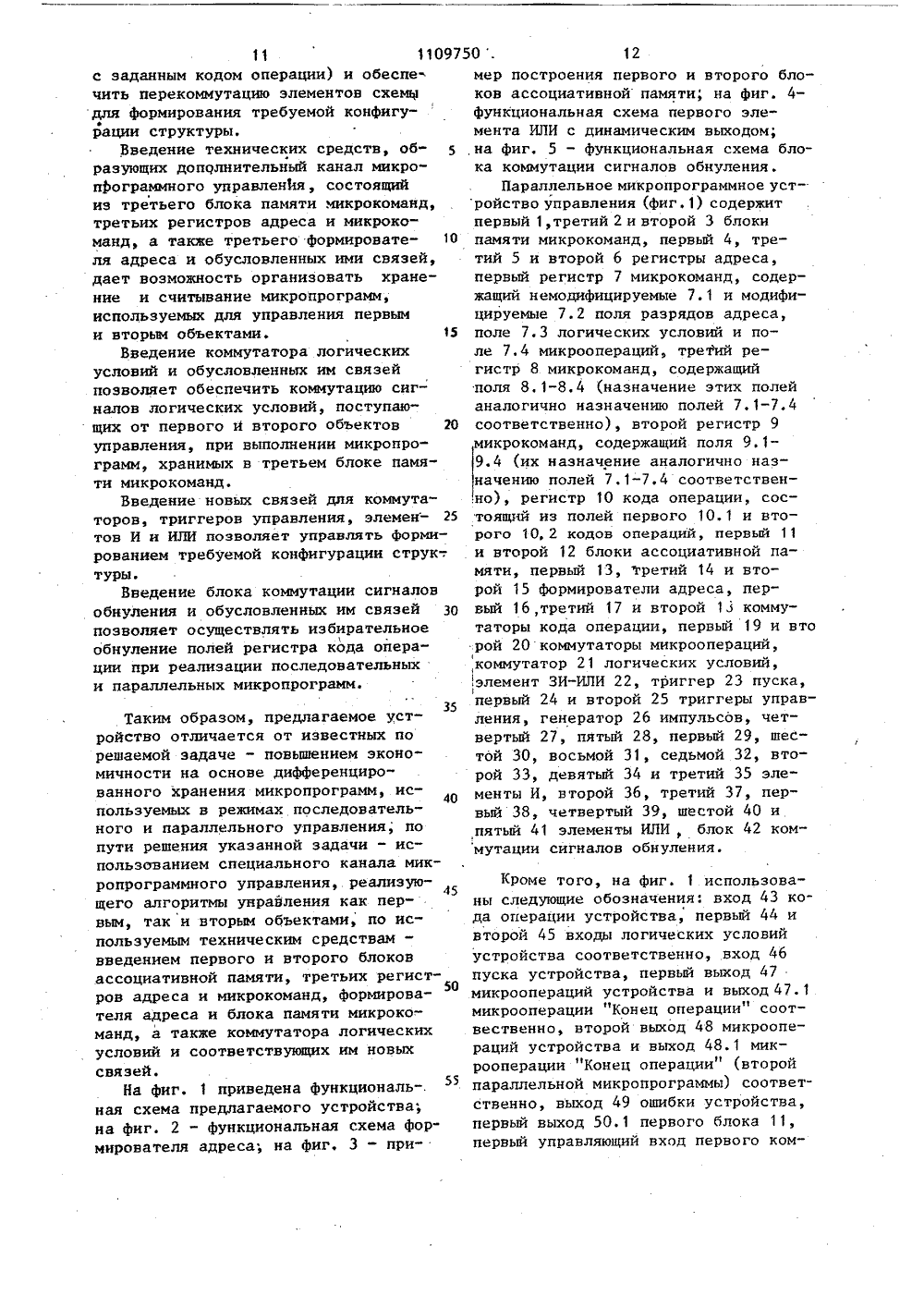

СОЮЗ СОВЕТСКИшии ампаРЕСПУБЛИК .(191 ( С 06.Р 11 ОБРЕТ ОПИС ИДЕТЕЛЬСТВ АВТОРСН во СССР74.СССР74.СССР81.СССР82 са пекоманционнвого госудАРственный комитет сссРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПЮ(56) 1, Авторское свидетельст У 437072, кл. С 06 Р 9/22, 192, Авторское свидетельство 9 451080, кл. С 06 Р 9/22, 193. Авторское свидетельство Оф 830383, кл. С 06 Р 9/22, 194. Авторское свидетельство У 1020825, кл,С 06 Р 9/22, 19 (прототип).(54) (57) 1. ПАРАЛЛЕЛЬНОЕ ИИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд, первый и второй регистры адреса, первый и второй формирователи. адреса, регистр кода операции, элемент ЗИ-ИЛИ, генератор импульсов, первый и второй триггеры управления, триггер пуска, первый и второй коммутаторы кода операции, первый и второй коммутаторы микро- операций, первый - девятый элементы И, первый - шестой элементы ИЛИ, одновибратор, причем вход кода опе- . рации устройства соединен с информационным входом регистра кода операции, вход пуска устройства соединен с входом синхронизации регистра кода операции и единичным входом триггера пуска, единичный выход которого соединен с входом генератора импульсов, нулевой выход первого триггера управления соединен с первым вхо" дом первого элемента И, выход которого соединен с входом одновибратора, первый и второй входы логических условий устройства соединены с первыми входами соответственно первого и второго формирователей адреса, выходы которых соединены с первыми информационными входами соответственно первого и второго регистров адреса, выходы немодифицируемых разрядов адрервого и второго регистров микрод соединены с вторыми информации входами соответственно пери второго регистров адреса, выходы которых соединены с входами первого и второго блоков памяти мик.рокоманд соответственно, выходы первого и второго блоков памяти соедине.ны с информационными входами соответственно первого и второго регистров микрокоманд, выходы модифицируемых разрядов адреса которых соединены с .вторыми входами первого и второго формирователей адреса соответственно выходы второго и третьего элементов И соединены с входами синхронизации соответственно первого и третьего регистров микрокоманд, выходы кода логических условий которых соединены с третьими входами первого и второго формирователей адреса соответственно, выход формирователя сигнала ошибки соединен с выходом ошибки устройства и первым входом первого элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, о т л и ч а ю щ е е с я тем, что, с целью повышения экономичности, в него введены третий блок памяти микрокоманд, третий регистр адреса, блок коммутации сигналов обнуления,15.К средствам хранения и считывания микрокоманд,относятся регистр 10 кода операции, формирователи 13-15 фор- . мирования, регистры 4-6 адреса, блоки 1-3 памяти микрокоманд, регист ры 7-9 микрокоманд.Регистр 1 О обеспечивает хранение кода операции. Этот регистр имеет два поля, обнуление которых производится раздельно сигналами с 10 выходом 47.1 и 48. 1.Формирователи 13-15 адреса служат для формирования адреса очередных микрокоманд в зависимости от кода и значения логических условий и 15 формирования начального адреса в соответствии с кодом операции.Мультиплексор 63 реализует логическую Функцию9:к а а 2.а +Х а а 2 аз"ао+ а 1 а Й " ао2" и 21 2 Ю огде х б 0,1,- значения логическихусловий;а 1 - значения 1-го разряда .кода логических условий,осИо К К - число логических услоъ 2вий,11097 Элемент ИЛИ 64 в точках ветвленияпроизводит модификацию младшего разряда адреса (его изменение с "0" на "1" в случае равенства единице проверяемого логического условия),Блоки 1-3 памяти предназначены35 для хранения микропрограмм. Регистры 4-6 обеспечивают хранение адреса очередной микрокоманды. Регистры 7-9 служат для запоминания считываемой микрокоманды.Средства пуска и синхронизации включают генератор 26 импульсов, триггер 23, элементы ИЛИ 38-41, элементы И 30-35. Элементы ИЛИ 38 и триг гер 23 выполняют Функции пуска устройства и останова его при появлении сигнала, ошибки или сигнала "Конец операции".Особенностью элемента ИЛИ 38 является наличие динамического выхода.50 При появлении сигнала на одном иэ входов элемента ИЛИ 38 на его выходе формируется короткий импульс, который производит обнуление триггера 23 пуска. Формирование импульса осуществляется одновибратором 66 (фиг, 4).55Генератор 26 импульсов выполняет функцию формирования двух серий тактовых импульсов. Элементы ИЛИ 39-4116 50 и элементы И 30-35 обеспечивают синхронизацию устройства в, зависимости от режима работы и кода операции. При выполнении последовательных микропрограмм осуществляется считывание: информации из одного блока памяти микрокоманд (блоков 1,2 или 3). В параллельном режиме работы в зависимости от кода операции производится одновременное считывание из пары блоков памяти 1 и 2 (1 и 3), (2 и 3).К средствам управления и коммута- ции относятся блоки 11 и 12, триггеры 24 и 25 управления, коммутаторы 16-21, элементы ИЛИ 36 и 37, элементы И 27-29, блок 42 коммутации сигналов обнуления, Блоки 11 и 12 формируют сигналы, разрешающие считывание микрокоманд с блоков 1-3 памяти в последовательном режиме и параллельное считывание микрокоманд иэ блоков 1 и 2 (1 и 3), (2 и 3), управляют синхронизацией устройства, коммутацией операционных частей микрокоманд и кодов логических условий. Блок 42 осуществляет избирательное обнуление полей регистра 10. Обнуление разрядов поля 10,1 (10.2) производится при окончании микропрограмм, реализуемых каналами микропрограммного управления и инициируемых сигналами на выходах 50.1-50.3 (51.1-51.3) блоков 11 (12) . При поступлении кодов 0100, 0010, 1001, которым соответствуют кодыоперации 0100, 1100, 0010, 1001, 1011, формируется сигнал на выходе 50. 1 (51. 1), т.е.микропрограммы с указанными кодами операции хранятся в блоке 1 памяти микрокоманд. Единичные сигналы на выходах 50.2 (51.2) и 50.3 (51,3) формируются при поступлении кодов 1101, 0001, 0110, 1110 и 0011, 0111, 1111 соответственно.Коммутаторы 16-18 коммутируют код операции в зависимости от сигналов блоков 11- 12, Коммутаторы 19 и 20 предназначены для коммутации операционных частей микрокоманд,коммутатор 21 коммутирует коды логических условий. Элементы ИЛИ 36 и 37 формируют сигналы начала выполнения микропрограмм, Элементы И 27-29, триггеры 24 и 25 формируют команды на запоминание начала микропрограмм и останов устройства после окончания выполнения микропрограммы.110975 17 При появлении сигналов на выходах 50. 1, 50.2 сигнал обнуления поля 10. 1 формируется одновибратором 71.При этом единичным сигналом с выходаэлемента ИЛИ 69 открывается первыйэлемент И коммутатора 67 и при окончании микропрограммы по микрооперациина выходе 47.1, проходящей черезвход 75.1, формируется перепад "0"поступающий на одновибратор 71. 0Кроме того, сигнал обнуления выдается на выход 76 в случае появлениясигналов на выходе 50.3 (входе 73.3)и выходе 48. 1 (входе 75.2), Аналогично формируются сигналы обнуления поля 10.2 коммутатором 68 и одновибратором 72,К средствам контроля относитсяэлемент ЗИ-ИЛИ 22. Он предназначендля контроля правильности функционирования блоков 11 и 12, регистра 10и контроля правильности подачи кодовопераций на вход устройства и представляет собой элемент И-ИЛИ.Сигналошибки появляется на выходе 49 в случае одновременного появления сигналов на выходах 50.1 и 51.1, 50.2и 51.2, 50,3 и 51.3 блоков 11 и 12,что соответствует. обращению к одномуканалу двух внешних устройств в параллельном режиме. Этим сигналомобнуляется триггер 23 пуска и работа устройства пркращается. Предлагаемое устройство работает в двух режимах: раелизации после- З 5довательныхмикропрограмм и параллельной реализации двух микропрограмм.Реализация последовательных микропрограмм.В исходном состоянии элементыпамяти находятся в "О". После прихода кода операции на вход 43 подается команда "Пуск" на вход 46. По,этой команде происходит запись кодаоперации в регистр 10. С поля 1 О,(10.2) регистра 10 код операции поступает на вход блока 11 (12), навыходе 50. 1 (50.2, 50.3 (51.1,51.2, 51.3) которой появляется50сигнал, управляющий работой коммутаторов 16-18, Они определяют, ккакому каналу необходимо обратитьсядля считывания очередной микропро"граммы. Одновременно триггер 23 устанавлиается в единичное состояние55и разрешает формирование тактовыхимпульсов от генератора 26 импульсов.Импульсы на выходе 53,1 генерато-. 0 18ра 26 задержаны на величину 1, относительно сигналов на выходе 53.2.Пусть код операции записан в поле 10. регистра 10 кодов операций и в соответствии с этим кодом на выходе 50,1 блока 11 формируется управляющий сигнал, который разрешает прохождение синхроимпульсов с выходов 54 и 57 и разрешает формирование микроопераций коммутатором 9 на выходе 47. На выходе, элемента ИЛИ 36 формируется единичный сигнал, который поступает на вход элемента И 27. Первый синхроимпульс с выхода 53. 1 генератора 25 открывает элемент И 27 выходной сигнал которого устанавливает триггер 24 в единичное состояние, С первым импульсом на выходе 54 происходит запись начального адреса в регистр 4. Тактовым импульсом с выхо,да 57 производится запись кода микрокоманд из блока 1 памяти в регистр 7 в соответствии с начальным адресом, записанным в регистре 4. Операционная часть микрокоманды с поля 7.4 регистра 7 поступает иа первый и второй информационные входы коммутатора 19, который выдает операционную часть микрокоманды на выход 47 под воздействием управляющего сигнала на входе 50, 1, Косвенный адрес микро- команды с ноля 7.1 регистр 7 поступает на вход регистра 4.Модифицируемый разряд с поля 7.4 и код логического условия с поля 7.3 регистра 7 поступают на входы формирователя 13 адреса. В формирователе (фиг. 2) осуществляется модификация адреса следу. - ющим образом. На вход мультиплексора 63 подаются номера логических условий 7.3 и 7,4, на выходе формируется сигнал и подается на второй вход элемента ИЛИ 64, на первый вход которого поступает модифицируемый разряд. На выходе элемента ИЛИ 64 формируется значение модифицированного разрядаС выхода формирователя 13 модифицированный раз ряд поступает иа вход регистра 4.При подаче очередного тактового импульса на вход 54 адрес очередной микракоманды, состоящий из косвенного адреса и модифицированного разряда, записывается в регистр 4;.По очередному тактовому импульсу с выхода 57 из блока 1 памяти считывается очередная микрокоманда, которая заносится в регистр 7. Далее работа устройства20 продолжается аналогично описанному. При считьвании последней микрокоманды на выходе 47.1 появляется сигнал "Конец операции", который переводит к нулевое состояние триггер 24. Кроме того, по этому сигналу производится обнуление поля 10.1 регистра 10. Эту функцию реализует блок 42 коммутации сигналов обнуления (фиг, 5). Так как сигнал "Конец операции" появ О ляется по тактовому импульсу с выхода 53.2, а единичный сигнал на входе триггера 25 появляется по импульсу с выхода 53, 1, то этим исключается возможность появления единич ных сигналов на двух входах триггера 24.После обнуления посредством блока 42 поля 10. 1 регистра 10 и триггера 24 на выходе элемента И 29 появляется единичный потенциал. После этого импульсом с выхода элемента ИЛИ 38 обнуляется триггер 23, который запрещает формирование импульсов генератором 26. Устройство 25 устанавливается в исходное состояние, Если после записи кода операции в поле 10. 1 регистра 10 появляются управляющие сигналы на выходах 50.2 или 50.3, работа устройства проис- зО ходит аналогично описанному, Отличие состоит лишь в том, что считывание микрокоманд производится из блоков 2 или 3 памяти соответственно. При работе с блоком 2 памяти логичес-З 5 кие условия с входа 44 через коммутатор 21 под воздействием управляющего сигнала с выхода 50.2 подают.ся на вход 52 формирователя 14.При записи кода операции в по де 10.2 регистра 10 работа устройства происходит согласно рассмотренному алгоритму. В этом случае управле" ние производится с помощью блока 12.Параллельная реализация двух мик ропрограмм.В исходном состоянии после подачи команды "Пуск" на входе 43 в отличие ат режима реализации одной микропрограммы происходит запись двух кодов операций в поля 10. 1 и 10.2 регистра 10. При этом в соответствии с кодами операций на выходах блоков 11 и 12 появляются управляющие сигналы, которые разрешают независимое считывание микрокоманд из пары блоков памяти в соответствии с управляющими сигналами. Выдача операционных частей микрокоманд производится одновременно с двух выходов 47 и 48 в соответствии с управляющими сигналами блоков 11 и 12. Работа каждого канала происходит аналогично алгоритму работы при реализации одной последовательной микропрограммы. По первому тактовому импульсу с выхода 53. триггеры 24 и 25 устанавливаются в единичное состояние в соответствии с сигналами на выходах блоков1 и 12. Например, пусть параллельно считьваются микропрограммы из блоков 2 и 3 памяти микрокоманд (присутствуют сигналы на выходе 50.2 блока 11 и 51.3 блока 12). Если первым заканчивается считьвание микропрограммы иэблока 3 памяти, тогда сигналом с выхо-да 47.1 триггер 24 н сигналом с выхода 76 блока 42 первое поле 10.1 регистра 10 устанавливаются в нулевое состояние, По окончании считыва" ния микрокоманд из блока 3 памяти сигналом с выхода 48.триггер 25 и второе поле 10.2 регистра 10 сигна. лом с выхода 77 блока 42 устанавливаются в нулевое состояние, Под воздействием положительного перепада одновибратор 66 формирует импульс, который устанавливает в нулевое состояние триггер 23, Нулевой сигнал на,выходе триггера 23 запрещает выдачу синхроимпульсов генератором 26. Устройство устанавливается в исходное состояниеПри одновременном появлении сигналов на двух одноименных выходах блоков 11 и 12 элемент ЗИ-ИЛИ 22 выдает сигнал ошибки и блокирует работу предлагаемого устройства.1109750 дактор А.Мотыл ПодписноСР Тираж 699 ственного Ко бретеиий и о , Ж, Раушс митет ткрыт д. 4/ илиал ППП "Патент", г.ужгород, ул.Проектная, 4 Заказ 6085/34 ВН и 113ИИПИ Госудаделам из 5, Москв ставитель Н.Сигаловхред Л,Мартяшова Корректор С.Шекмар750 1109третий регистр микрокоманд, третийформирователь адреса, первый и второй блоки ассоциативной памяти, коммутатор логических условий и третийкоммутатор кода операций, причем первый и второй, входы логических условйй устройства соединены соответственно с первым и вторым информационными входами коммутатора логическихусловий, выход которого соединен спервым входом третьего формирователя адреса, выход третьего формирователя адреса соединен с первым информационным входом третьего регистраадреса, выход которого соединен свходом третьего блока памяти микрокоманд, выход третьего блока памятимикрокоманд соединен с информационным входом третьего регистра микрокоманд, выходы немодифицируемых разрядов адреса, модифицируемого разряда адреса и кода логических условий которого соединены соответственнос вторым информационным входом регистра адреса, вторым и третьим входами третьего формирователя адреса, первый выход регистра кода операциисоединен с входом первого блока ассоциативной памяти и первыми информационными входами первого, второго . и третьего коммутаторов кода операции выходы которых соединены с третьими информационными входами первого, второго и третьего регистров адреса соответственно, выход одновибратора соединен с вторым входом первого элемента ИЛИ, второй выход регистра кода операции соединен с входом второго блока ассоциативной памяти, вторыми информационными входами первого, второго и третьего коммутаторов кода операции, выходы второго и третьего элементов ИЛИ соедийены с первыми входами соответ. ственно четвертого и пятого элементов И, выходы которых соединены с единичными входами первого и второго триггеров управления соответственно, первый выход генератора импульсов соединен с вторыми входами четвертого и пятого элементов И и первыми входами шестого, седьмого и восьмого элементов И, выходы которых соединены с входами синхронизации первого, второго и третьего регистров адреса соответственно, второй выход гене- Р атора тактовых импульсов соединен с первыми входами второго, третьего и девятого элементов И, выход которого соединен с входами синхронизациитретьего регистра микрокоманд, выходмикроопераций первого регистра микрокоманд соединен с первым и вторым информационными входами первого коммутатора микроопераций, группа выходовкоторого является первым выходоммикроопераций устройства, выход микроопераций второго регистра микрокоманд соединен с первым и вторыминформационными входами. второго .коммутатора микроопераций, группавыходов которого является вторымвыходом микроопераций устройства, выход микроопераций третьего регистрамикрокоманд соединен с треТьими информационными входами второго коммутатора и первого коммутатора микроопераций, выход конца операции группы,выходов которого соединен с нулевым входом первого триггера управления, выход конца операции группывыходов второго коммутатора микроопераций соединен с нулевым входомвторого триггера управления, нулевой выход которого соединен с вторымвходом первого элемента И, первыйвыход первого блока ассоциативнойпамяти соединен с первыми управляю-щими входами первого коммутатора кода операции и первого коммутаторамнкроопераций, первым входом элемен"та ЗИ-ИЛИ и первыми входами второгои четвертого элементов ИЛИ, выходкоторого соединен с вторыми входамивторого и шестого элементов И, первый выход второго блока ассоциативнойпамяти соединен с вторыми входамивторого, четвертого элементов ИЛИи элемента ЗИ-ИЛИ и вторыми управляющими входами первого коммутатора микроопераций и первого коммутатора кода операции, выход которого соединенс третьим. информационным входом пер-.вого регистра адреса, вторые выходыпервого и второго блоков ассоциативной памяти соединены соответственнос первым и вторым управляющими входами коммутатора логических условий,третий выход первого блока ассоциативной памяти соединен с первым входомтретьего элемента ИЛИ, с первыми управляющими входами второго коммутатора кода операции и второго коммутатора микроопераций, третьим входомэлемента ЗИ-ИЛИ и первым входом пятого элемента ИЛИ, выход которого сое-динен с вторыми входами третьего иседьмого элементов И, третий выход1109750ка коммутации сигналов обнуления,первый и второй выходы группы выходов которого соединены с первым ивторым установочньми входами регистФра кода операции соответственно. второго блока ассоциативной памяти соединен с четвертым входом элемента ЗИ-ИЛИ, вторыми входами третьего и пятого элементов ИЛИ и вторыми управляющими входами второго коммутатора микроопераций и второго коммутатора кода операции, выход которого соединен с третьим информационным входом второго регистра адреса, второй выход первого блока ассоциативной памяти соединен с первым управляющим входом третьего коммутатора адреса, пятым входом элемента ЗИ-ИЛИ, третьим управляющим входом первого коммутатора микроопераций, третьим входом второго элемента ИЛИ и первым входом шестого элемента ИЛИ, выход которого соединен с вторыми входами восьмого и девятого элементов И, второй выход второго блока ассоциативной памяти соединен с третьим входом третьего элемента ИЛИ, вторым входом шестого элемента ИЛИ, шестым входом элемента ЗИ-ИЛИ, третьим управляющим входом второго коммутатора микроопераций и вторым управляющим входом третьего коммутатора кода операции, выход которого соединен с третьим информационным входом третьего регистра адреса, первый - третий выходы первого и второго преобразователей кода операции в начальный адрес соединены с группой управляющих входов блока коммутации сигналов обнуления, выходы конца операции . групп выходов первого и второго коммутаторов микроопераций соединены с группой информационных входов бло 2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок коммутации сигналов обнуления содержит первый и второй коммутаторы, первый и второй элементы ИЛИ, первый и второй одновибраторы, причем первый и второй входы группы управляющих входов блока соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым управляющим входом первого коммутатора, третий и четвертый входы группы управляющих входов блока соединены соответственно с вторым управляющим входом первого и пер- вым управляющим входом второго коммутаторов, выходы которых через первый и второй одновибраторы соединены соответственно с первым и вторым выходами группы выходов блока, пятый и шестой входы группы управляющих входов блока соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, первый вход группы информационных входов блока соединен с первыми информационными входами первого и второго коммутаторов, второй вход группы информационных входов блока соединен с вторыми информационными входами первого и второго коммутаторов.Изобретение относится к цифровой"вычислительной технике и может бытьиспользовано при разработке устройств управления параллельными процессами вычислительных и управляющих систем,Известны микропрограммные устройства управления, содержащие первыйи второй блоки памяти микрокоманд,10регистры микрокоманд и адреса, формирователи адреса, триггеры, элементы И 11 и 2. Недостатками указанных устройсгв являются низкая производительность и узкая область применения, обусловленные их невозможностью управления параллельными процессамиИзвестно микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры адреса, первый и второй коммутаторы, блок синхронизации, первый и второй триггеры управления, элементы.И, ИЛИ 3 3,Недостаток такого устройства - низкая производительность, обуслов-, ленная отсутствием техническихсредств для управления параллельными процессами и перетактовкой схемы при последовательном выполнении двух четных (нечетных) микрокоманд.Наиболее близким к предлагаемому по технической сущности и достигаемому результату является параллельное микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры, адреса, первый и второй регистры микрокоманд, схему сравнения, первый - четвертый коммутаторы, формирователь тактовых импульсов, первый и второй формирователи адреса, первый - пятый триггеры управления, первый - восьмой элементы И, первый- седьмой элементы ИЛИ, первый и второй элементы И-НЕ, одновибратор, блок элементов ИЛИ, причем вход логических условий устройства соединен с первыми информационными входами первого и второго формирователей адреса, выходы которых соединены с первыми входами соответственно первого и второго регистров адреса, вход кода операции устройства соединен с вторыми информационными входами первого и второго регистров адреса, выходы которых соединены с информационными входами соответственно первого и второго блоков памяти микрокоманд, выходы первого и второго элементов И соединены с управляющими входами соответственно первого и второго блоков памяти микрокоманд, выходы которых соединены с входами соответственно первого и второго регистров микрокоманд, первые управляющие выходы первого и второго регистров микрокоманд соединены с единичными входами соответственно первого и второго триггеров управления, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого является выходом микроопераций устройства, выход адреса первого регистра микракоманд соединен с первыми информационными входами первого и второго коммутаторов, выход адреса второго регистра микрокоманд соединен с вторыми информационными входами первого н второго коммутаторов, выходы которых соединены с вторыми информационными входами соответственно первого и второго формирователейадреса, вход кода операции устройства через первый элемент.ИЛИ соединенс единичным входом третьего триггерауправления, единичный выход которогосоединен с входом формирователя тактовых импульсов, первый выход формирователя. тактовых импульсов соеди О нен с нулевыми входами триггеровполей микроопераций первого и второго регистров микрокоманд и с первымиинформационными входами третьего ичетвертого коммутаторов, выходыкото рых соединены с первыми входами соответственно первого и второго элементов И, второй и третий выходы форми"рователя тактовых импульсов соединены соответственно с вторыми и тре тьими информационными входами третьего и четвертого коммутаторов, единичный выход четвертого триггерауправления соединен с первыми управляющими входами третьего, четверто го коммутаторов, первыми входамитретьего, четвертого, пятого элементов И и первого и второго элементов И-НК, выходы которых соединеныс вторыми входами соответственно перЗ 0 ваго и второго элементов И, второйуправляющий выход первого регистрамикрокоманд соединен с первыми входами второго и третьего элементов ИЛИ,выход которого соединен с первым 35управляющим входом первого коммутатора, второй управляющий выход второго регистра микрокоманд соединен спервым входом четвертого и вторым входом второго элементов ИЛИ, выход 40 которого соединен с Т-входом пятого1триггера управления единичный выходпятого триггера управления соединен свторыми управляющими входами третьегои четвертого коммутаторов, а нулевой 4 выход соединен с третьими управляющи-.45ми входами третьего и четвертого коммутаторов, третьи управляющие выхо-.ды первого и второго регистров микрокоманд через пятйй элемент ИЛИ сое динены с единичным входом четвертого триггера управления, нулевой выход которого соединен с вторым управляющим входом первого коммутатораи первым управляющим входом второго 55 коммутатора, нулевые выходы первогои второго триггеров управления соединены с вторыми входами соответственно третьего и пятого элементов И,выходы которых соединены с вторыми40 входами соответственно третьего и четвертого элементов ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, третьи управляющие выходы первого и второго регистров микрокоманд соединены с третьими управляющими входами соответственно первого и второго коммутаторов, единичный выход первого триггера управления соединен с вторым О входом первого элемента И-НЕ и первым входом шестого элемента И, единичный выход второго триггера управ. - ления соединен с вторым входом второго элемента И-НЕ и вторым входом 15 шестого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов И, а через одно- вибратор - с нулевыми входами первого, второго и четвертого триггеров 20 обнуления, выходы адреса первого и второго регистров микрбкоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверсный выходы которой соедине ны с вторьии входами соответственно седьмого и восьмого элементов И, выход седьмого элемента И соединен с третьими, входами третьего и четвертого элементов ИЛИ, выход восьмого элемента И, соединен с первыми входами шестого и седьмого элементов ИЛИ, выходы которых соединены соответственно с нулевым входом третьего триггера управления и выходом ошибки устройства, выход конца операции блока элементов ИЛИ соединен с вторыми входами шестого элемента ИЛИ и четвертого элемейта И, выход которого соединен с вторьи входом седьмого элемента ИЛИ 41.Недостатком известного устройства является низкая экономичность, обусловленная избыточньи объемом блоков памяти микрокоманд.45В известном устройстве имеются два блока памяти микрокоманд, в которых записаны микропрограммы, реализуемые в последовательном и параллельном режимах. В последовательном ре 50 жиме известное устройство функционирует по двуплечевой схеме, те. микрокоманды поочередно считываются из блоков памяти, в параллельном режиме микрокоманды параллельно считы 55 ваются из двух блоков памяти и поступают на объект (объекты) управления.Хранение в блоках памяти известного устройства большого числа повторяющихся микропрограмм обусловливает его низкую экономичность, а следовательно, и низкую надежность,Цель изобретения - повышение экономичности устройства.Поставленная цель достигается тем что в параллельное микропрограммное устройство управления, содержащее первый и второй блоки памяти микро- команд, первый и второй регистры микрокоманд, первый и второй регистры адреса, первый и второй формирователи адреса, регистр кода операции, элемент ЗИ-ИЛИ, генератор импульсов, первый и второй триггеры управления, триггер пуска, первый и второй коммутаторы кода операции, первый и второй коммутаторы микроопераций, пер-; вый - девятый элементы И, первый - шестой элементы ИЛИ, одновибратор, причем вход кода операции устройства соединен с информационньи входом регистра кода операции, вход пуска устройства соединен с входом синхронизации регистра. кода операции и единичньи входом триггера пуска, единичный выход которого соединен с входом генератора импульсов, нулевой выход первого триггера управления соединен с первым входом первого элемента И, выход которого соединен с входом одновибратора, первый и второй входы логических условий устройства соединены с первьии входами соответственно первого и второго формирователей адреса, выходы которых соединены с первыми информационньии входами соответственно первого и второго регистров адреса, выходы немодифицируемых разрядов адреса первого и второго регистров микрокоманд соединены с вторыми информационными входами соответственно первого и второго регистров адреса, выходы которых соединены с входами первого и второго блоков памяти микрокоманд соответст венно, выходы первого и второго блоков памяти соединены с информационными входами соответственно первого и второго регистров микрокоманд, выходы модифицируемых разрядов адреса которых соединены с вторыми входами первого и второго формирователей адреса соответственно, выходы второго и третьего элементов И соединены с входами синхронизации соответственно первого и третьего регистров микрои второго триггеров управления соот.ветственно, первый выход генератораимпульсов соединен с вторыми входами четвертого и пятого элементов Ии первыми входами шестого, седьмогои восьмого элементов И, выходы которых соединены с входами синхронизации первого, второго и третьего регистров адреса соответственно, второйвыход генератора тактовых импульсовсоединен.с первыми входами второго,третьего и девятого элементов И, выход которого соединен с входами синхронизации третьего регистра микроко-манд, выход микроопераций первого регистра микрокоманд соединен спервым ивторым информационными входами первого коммутатора микроопераций, группавыходов которого является первым выходом микроопераций устройства, выходмикроопераций второго регистра микрокоманд соединен с первым и вторыминформационными входами второго коммутатора микроопераций, группа выходов которого является вторым выходоммикроопераций устройства, выход микрооперацнй третьего регистра микрокоманд соединен с третьими информационнымн входами второго коммутатораи первого коммутатора микроопераций,выход конца операции группы выходовкоторого соединен с нулевым входомпервого триггера управления, выходконца операции группы выходов второго коммутатора микроопераций соединен с нулевым входом второго триггера управления, нулевой выход которого соединен с вторым. входом первого элемента И, первый выход первогоблока ассоциативной памяти соединенс первыми управляющими входами первого коммутатора кода операции и первого коммутатора микроопераций, первьк входом элемента ЗИ-ИЛИ и первымивходами второго и четвертого элемен.тов ИЛИ, выход которого соединен свторыми входамивторого и шестогоэлементов И, первый выход второгоблока ассоциативной памяти соединенс вторыми входами второго и четвертого элементов ИЛИ и элемента ЗИ-ИЛИи вторыми управляющими входами первого коммутатора микроопераций ипервого коммутатора кода операции,выход которого соединен с третьиминформационным входом первого регистра адреса, вторые выходы первогои второго блоков ассоциативной па 7 1109750 команд, выходы кода логических усло.вий которых соединены с третьими входами первого и, второго формирователей адреса, соответственно, выход формирователя сигнала ошибки соединен с выходом ошибки .устройства и первым входом первого элемента ИЛИ, выход которого, соединен е нулевым входом триггера пуска, дополнительно введены третий блок памяти миКрокоманд, тре тий регистр адреса, блок коммутации сигналов обнуления, третий регистр микрокоманд, третий формирователь адреса, первый и второй блоки ассоциативной памяти, коммутатор логичес ких условий и третий коммутатор кода операций, причем первый и второй входы логических условий устройства соединены соответственно с первым и вторым ииформационнымн входами ком мутатора логических условий, выход которого соединен с первым входом третьего формирователя адреса, выход третьего формирователя адреса соединен с первым информационным входом25 третьего регистра адреса, выход которого соединен с входом третьего блока памяти микрокоманд, выход третьего блока памяти микрокоманд соединен с информационным входом третьего ре 30 гистра микрокоманд, выходы немодифицируемых разрядов адреса, модифици. руемого разряда адреса и кода логических условий которого соединены соответственно с вторым информацион ным входом регистра адреса, вторым и третьим входами третьего формирователя адреса, первый выход регистра кода операции соединен с входом первого блока ассоциативной памяти40. и первыми информационными входами первого, второго и третьего комму" таторев кода операции, выходы которых соединены с третьими информациокными, входами первого, второго и. тре 45 тьего регистров адреса соответственно, выход одновибратора соединен с вторым входом первого элемента ИЛИ, второй выход регистра кода операции соединен с входом второго блока50 ассоциативной, памяти, вторыми информационными входами первого, второго и третьего коммутаторов кода операции, выходы второго и третьего эле 55 ментов ИЛИ соединейыс первыми входами соответственно четвертого и пятого элементов И, выходы которых соединены с единичными входами первого40 45 50 55 яти соединены соответственно с перГ,вым и вторым управляющими входамикоммутатора логических условий, третий выход первого блока ассоциативной памяти соединен с первым входомтретьего элемента ИЛИ, с первымиуправляющими входами второго коммутатора кода операции и второго коммутатора микроопераций, третьим входом элемента ЗИ-ИЛИ и первым входомпятого элемента ИЛИ, выход которогосоединен с вторыми входами третьегои седьмого элементов И, третий выходвторого блока ассоциативной памятисоединен с четвертым входом элемента ЗИ-ИЛИ, вторыми входами третьегои пятого элементов ИЛИ и вторымиуправляющими входами второго коммутатора микроопераций и второго коммутатора кода операции, выход которогосоединен с третьим информационнымвходом второго регистра адреса, второй выход первого блока ассоциативной памяти соединен с первым управляющим входом третьего коммутатораадреса, пятым входом элемента ЗИ-ИЛИ,третьим управляющим входом первого , коммутатора микроопераций, третьимвходом второго элемента ИЛИ и первьмвходом шестого элемента ИЛИ, выходкоторого соединен с вторыми входамивосьмого и девятого элементов И,второй выход второго блока ассоциативной памяти соединен с третьимвходом третьего элемента ИЛИ, вторымвходом шестого элемента ИЛИ, шестьивходом элемента ЗИ-ИЛИ, третьим управляющим входом второго коммутатора микроопераций и вторым управляющим входом третьего коммутатора кода операции, выход которого соединенс третьим информационным входом третьего регистра адреса, первый - третий выходы первого и второго преобразователей кода операции в начальный адрес соединены с группой управляющих входов блока коммутации сигна-,лов обнуления, выходы конца операциигрупп выходов первого и второго коммутаторов микроопераций соединены сгруппой информационных входов коммутатора сигналов обнуления, первый ивторой выходы группы выходов которого соедйнены с первым и вторым установочными входами регистра кода операции соответственно.Кроме того, блок коммучации сигналов обнуления содержит первый и второй коммутаторы, первый и второйэлементы ИЛИ, первый и второй одновибраторы, причем первый и второйвходы группы управляющих входов бло ка соединены соответственно с первыми вторым входами первого элемента ИЛИ,выход которого соединен с первым управляющим входом первого коммутатора, третий и четвертый входы группы 10 управляющих входов блока соединенысоответственно с вторым управляющимвходом первого и первым управляющимвходом второго коммутаторов, выходыкоторых через первый и второй одно вибраторы соединены соответственнос первым и вторым выходами группывыходов блока, пятый и шестой входыгруппы управляющих входов блока соединены соответственно с первым и 20 вторым входами второго элемента ИЛИ,выход которого соединен с вторым управляющим входом второго коммутатора,первый вход группы информационныхвходов блока соединен с первыми ин формационными входами первого и второго коммутаторов, второй вход груп-пы информационных входов блока соединен с вторыми информационными входамипервого и второго коммутаторов. З 0 Сущность изобретения состоитвповышении экономичности устройствапутем сокращения суммарного объемапамяти микрокоманд за счет введе- фния специального блока памяти изаписи в него микропрограмм, реализуемых в обоих каналах управления. В предлагаемом устройстве в нервом блоке памяти хранятся микропрограммы, предназначенные для управле- ния, как правило, только первым каналом (объектом), во втором блоке памяти хранятся микропрограммы, предназначенные для управления только вторым каналом, в третьем блоке памяти хранятся микропрограммы, используемые для управления как первьи, так и вторым каналами. При этом исключается (или существенно уменьшается) дублирование микропрограмм, используемых в режимах последовательного и параллельного управления.Введение первого и второго блоков ассоциативной памяти, обусловленных ими связей позволяет по коду операции идентифицировать номер блока памяти микрокоманд, к которому долм- нО быть произведено обращение (в котором хранится микропрограмма12 50 11 11097с заданным кодом операции) и обеспечить перекоммутацию элементов схемыдля формирования требуемой конфигурации структуры,Введение технических средств, образующих дополнительный канал микропрограммного управления, состоящийиз третьего блока памяти микрокоманд,третьих регистров адреса и микрокоманд, а также третьего формирователя адреса и обусловленных ими связей,дает возможность организовать хранение и считывание микропрограмм,используемых для управления первыми вторым объектами, 15Введение коммутатора логическихусловий и обусловленных им связейпозволяет обеспечить коммутацию сигналов логических условий, поступающих от первого й второго объектов 20управления, при выполнении микропрограмм, хранимых в третьем блоке памяти микрокоманд.Введение новых связей для коммутаторов, триггеров управления, элементов И и ИЛИ позволяет управлять формированием требуемой конфигурации струк-.туры.Введение блока коммутации сигналовобнуления и обусловленных им связей Зопозволяет осуществлять избирательноеобнуление полей регистра кода операции при реализации последовательныхи параллельных микропрограмм.35Таким образом, предлагаемое устройство отличается от известных порешаемой задаче - повышением экономичности на основе дифференцированного хран 1 ния микропрограмм ф ис 4пользуемых в режимах последовательного и параллельного управления, попути решения указанной задачи - использованием специального канала микропрограммного управления, реализующего алгоритмы унравления как первым, так и вторым объектами, по используемым техническим средствам -введением первого и второго блоковассоциативной памяти третьих регистУ50ров адреса и микрокоманд, формирователя адреса и блока памяти микрокоманд, а также коммутатора логическихусловий и соответствующих им новыхсвязей.На фиг. 1 приведена функциональ-.ная схема предлагаемого устройства;на фиг. 2 - функциональная схема формирователя адреса; на фиг. 3 - пример построения первого и второго блоков ассоциативной памяти; на фиг. 4 функциональная схема первого элемента ИЛИ с динамическим выходом; на фиг. 5 - функциональная схема блока коммутации сигналов обнуления.Параллельное микропрограммное устройство управления (фиг. 1) содержит первый 1,третий 2 и второй 3 блоки памяти микрокоманд, первый 4, третий 5 и второй 6 регистры адреса,первый регистр 7 микрокоманд, содержащий немодифицируемые 7.1 и модифицируемые 7,2 поля разрядов адреса,поле 7.3 логических условий и поле 7,4 микроопераций, третий регистр 8 микрокоманд, содержащийполя 8. 1-8.4 (назначение этих полейаналогично назначению полей 7.1-7.4соответственно), второй регистр 9 микрокоманд, содержащий поля 9.19.4 (их назначение аналогично назначению полей 7,1-7.4 соответственно), регистр 10 кода операции, состоящий из полей первого 10. 1 и второго 10, 2 кодов операций, первый 11и второй 12 блоки ассоциативной памяти, первый 13, третий 14 и второй 15 формирователи адреса, первый 16,третий 17 и второй 13 коммутаторы кода операции, первый 19 и второй 20 коммутаторы микрооперацийкоммутатор 21 логических условий,1 элемент ЗИ-ИЛИ 22, триггер 23 пуска,первый 24 и второй 25 триггеры управления, генератор 26 импульсов, четвертый 27, пятый 28, первый 29, шестой 30, восьмой 31, седьмой 32, второй 33, девятый 34 и третий 35 элементы И, второй 36, третий 37, первый 38, четвертый 39, шестой 40 ипятый 41 элементы ИЛИ, блок 42 коммутации сигналов обнуления. Кроме того, на фиг. 1 использованы следующие обозначения; вход 43 ко" да операции устройства, первый 44 и второй 45 входы логических условий устройства соответственно, вход 46 пуска устройства, первый выход 47 микроопераций устройства и выход 47.1 микрооперации "Конец операции" соотвественно, второй выход 48 микроопераций устройства и выход 48.1 микрооперации "Конец операции" (второй параллельной микропрограммы) соответственно, выход 49 ошибки устройства, первый выход 50.1 первого блока 11, первый управляющий вход первого ком110975 13мутатора 16 кода операции, первые входы элементов ИЛИ 36 и 39, первый вход элемента ЗИ-ИЛИ, первый управляющий вход первого коммутатора 19 микроопераций, второй выход 50.2 5 блока 11, первый управляющий вход третьего коммутатора 17 кода операции; первый управляющий вход коммутатора 21 логических условий, третий вход элемента ИЛИ 36, первый вход 1 О элемента ИЛИ 40, третий вход элемента 3 И-ИЛИ, третий управляющий вход первого коммутатора 19 микро- операций; третий выход 50,3 первого блока 11, первый управляющий вход 15 второго коммутатора 18 кода операции, первые входы элементов ИЛИ 37, 41, пятый вход элемента ЗИ-ИЛИ 22, второй управляющий вход второго коммутатора 20 микроопераций; первый вы ход 51.1 второго блока 12, второй управляющий вход первого коммутатора 16 кода операции, вторые входы элементов ИЛИ 36, 39, второй вход элемента ЗИ-ИЛИ 22, второй управляю щий вход первого коммутатора 19 микроопераций; второй выход 51,2 второго блока 12, второй управляющийвход третьего коммутатора 17 кода опе рации, второй управляющий вход ком- ЗО мутатора 21 логических условий, третий вход элемента ИЛИ 37, второй вход элемента ИЛИ 40, четвертый вход элемента ЗИ-ИЛИ 22, первый управляющий вход второго коммутатора 20 микроопераций, третий выход 51.3 второго блока 12, второй управляющий вход второго коммутатора 18 кода операции, вторые входы элементов ИЛИ 37, 41, шестой вход элемента ЗИ-ИЛИ 22, тре О тий управляющий вход второго коммутатора 20 микроопераций, выход 52 коммутатора 21 логических условий, первый 53.1 и второй 53.2 выходы генератора 26 импульсов, выход 54 45 элемента И 30, вход синхронизации первого регистра 4 адреса, выход 55 элемента И 31, вход синхронизации третьего регистра адреса, выход 56 элемента И 32, вход синхронизации второго регистра адреса; выход 57 элемента И 33, вход синхронизации первого регистра 7 микрокоманд, выход 58 элемента И 34, вход синхронизации третьего регистра 8 микрокоманд выход 59 элемента И 35, вход информации второго регистра 9 микрокоманд, выход 60 элемента ИЛИ 39, второй вход элемента И 30, второй вход 0 14элемента И 33, выход 61 элемента ИЛИ 40, второй вход элемента И 31, второй вход элемента И 34; выход 62 элемента ИЛИ 41второй вход элемента И 32, второй вход элемента И 35.Нафиг. 2 обозначены мультиплексор 63 и элемент ИЛИ 64.На фиг. 3 показана функциональная схема блоков 11 (12), реализуемых на базе программируемой матрицы для конкретного случаи кодировки кодов операции. Символами 65-68 обозначены первый - четвертый элементы НЕ соответственно, Х 1, Х 2, ХЗ, Х 4 - входы кода операций, Например, когда на вход блока 11 (12) поступают ко" . ды 0100 и 1100, сигнал появится на выходе 50.1 (51.1), Это означает, что микропрограммы с данным кодом операции хранятся в блоке 10 памяти микрокоманд. На фиг. 4 представлена функциональная схема элемента ИЛИ 38 с динамическим выходом, содержащая элемент ИЛИ 65 и одновибратор 66.Блок 42 коммутации сигналов обнуления (фиг. 5) состоит из первого 67 и второго 68 коммутаторов, первого 69 и второго 70 элементов ИЛИ и первого 71 и второго 72 одновибраторов, Кроме того, на фиг. 5 использованы следующие обозначения: первый 73. 1 - третий 73.3 управляющие входы группы управляющих входов соответственно. Эти входы соединены с первым 50. 1 - третьим 50.3 выходами блока 11 соответственно; четвертый 74.1 - шестой 74.3 управляющие входы группы управляющих входов соотвественно, которые соединены с первым 51. 1 - третьим 51.3 выходами блоками 12 соответственно; первый 75. 1 и второй 75.2 входы группы информационных входов блока, которые соединены с выходами 47, 1 и 47.2 соответственно; первый 76 и второй 77 выходы группы выходов соответственно. Эти выходы соединены с первым и вторым установочными входами (входами обнуления) регистра 10 кода операции,Рассмотрим назначение элементов устройства, в котором условно могут быть выделены: средства хранения и считывания микрокоманд, средства пуска и синхронизации; средства управления й коммутации, а также средства контроля.

СмотретьЗаявка

3573465, 06.04.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШ. СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, КАЛЬЧЕНКО СЕРГЕЙ БОРИСОВИЧ, ЧИГРИН ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное, параллельное

Опубликовано: 23.08.1984

Код ссылки

<a href="https://patents.su/15-1109750-parallelnoe-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Параллельное микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления с контролем переходов

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для автоматического измерения разрыхленности постели отсадочной машины